# Bachelorarbeit

Jana Miericke

Entwicklung und Validierung der Datenkommunikation zwischen FPGA und Processing System mit Linux-Betriebssystem auf einem System on Chip für die Regelung einer Magnetstromversorgung

### Jana Miericke

# Entwicklung und Validierung der Datenkommunikation zwischen FPGA und Processing System mit Linux-Betriebssystem auf einem System on Chip für die Regelung einer Magnetstromversorgung

Bachelor Thesis based on the examination and study regulations for the Bachelor of Engineering degree programme

Bachelor of Science Elektro- und Informationstechnik

at the Department of Information and Electrical Engineering

of the Faculty of Engineering and Computer Science

of the University of Applied Sciences Hamburg

Erstprüfer: Prof. Dr. Lutz Leutelt Zweitprüfer: Prof. Dr. Ulrich Sauvagerd Betreut durch Dr. Christian Putscher

Tag der Abgabe: 19. Mai 2023

# Inhaltsverzeichnis

| 1. | Zusammenfassung                                                      | 1  |

|----|----------------------------------------------------------------------|----|

|    | 1.1. Zusammenfassung                                                 | 1  |

|    | 1.2. Abstract                                                        | 1  |

| 2. | Einleitung                                                           | 3  |

| 3. | Grundlagen                                                           | 5  |

|    | 3.1. Mercury XU5                                                     | 5  |

|    | 3.2. Xilinx Developer Tools                                          | 6  |

|    | 3.3. Embedded Linux auf dem Zynq UltraScale+                         | 7  |

|    | 3.4. Das AXI-Protokoll                                               | 8  |

|    | 3.5. Unterarten des AXI-Protokolls                                   | 11 |

|    | 3.6. Der AXI-GPIO-Core                                               | 12 |

| 4. | Anforderungsanalyse                                                  | 14 |

|    | 4.1. Übergeordnetes System                                           | 14 |

|    | 4.2. Stakeholderanalyse                                              | 15 |

|    | 4.3. Zusammenfassung des Anforderungen                               | 18 |

| 5. | Konzept                                                              | 20 |

|    | 5.1. Die Xilinx Entwicklungsumgebung                                 | 20 |

|    | 5.2. Das AXI-Interface                                               | 21 |

|    | 5.3. Das AXI-Subordinate                                             | 21 |

|    | 5.4. Der AXI-Manager                                                 | 23 |

|    | 5.5. Das Linux-Betriebssystem                                        | 23 |

|    | 5.6. Validierung der Datenkommunikation                              | 24 |

| 6. | Implementierung                                                      | 26 |

|    | 6.1. Erstellung der Entwicklungsumgebung                             | 26 |

|    | 6.2. Erstellung eines Logik-Moduls                                   | 27 |

|    | 6.3. Implementierung der AXI-Kommunikation mit dem AXI-GPIO          | 27 |

|    | 6.4. Generierung des Linux-Boot-Image                                | 30 |

|    | 6.5. Programmierung des Processing Systems ohne Linux-Betriebssystem | 31 |

|    | 6.6. Programmierung des Processing-Systems mit Linux-Betriebssystem  | 35 |

|    | 6.7. Messung der Funktionalität und Performance des AXI-Interface    | 37 |

|    |                                                                      |    |

|    | 6.8. Messung des zeitlichen Unterschieds beim Hardwarezugriff mit und ohne |    |

|----|----------------------------------------------------------------------------|----|

|    | Linux-Betriebssystem                                                       | 38 |

| 7. | Auswertung                                                                 | 40 |

|    | 7.1. Funktionalität des AXI-Interface                                      | 40 |

|    | 7.2. Performance der AXI-Kommunikation                                     | 45 |

|    | 7.3. Der Einsatz des Linux-Betriebssystems                                 | 51 |

| 8. | Fazit                                                                      | 53 |

| 9. | Ausblick                                                                   | 55 |

| 10 | Literaturverzeichnis                                                       | 57 |

| A. | Appendix                                                                   | 62 |

| В. | Eidesstattliche Erklärung                                                  | 66 |

# 1. Zusammenfassung

# 1.1. Zusammenfassung

Für die Implementierung einer Magnetstromregelung wurde die Entwicklungsplattform Mercury XU5 von Enclustra in Betrieb genommen. Auf dem System on Chip wurde zwischen dem FPGA und dem Processing-System mit Linux-Betriebssystem eine Datenkommunikation mit dem AXI-Interface aufgebaut. Die wichtigste Anforderung war die Evaluation der zeitlichen Performance dieser Übertragung, da diese der Echtzeitanforderung der Regelung unterliegt. Die Datenkommunikation wurde mit dem AXI-GPIO-IP-Core von Xilinx aufgebaut. Es wurde eine Software geschrieben, die den AXI-GPIO-Core aus dem Linux-Betriebssystem heraus auslesen und beschreiben kann. Die Performance der Datenübertragung wurde mit dem Integrated-Logic-Analyzer von Xilinx gemessen. Dabei stellte sich heraus, dass diese auf dem AXI4-Lite-Interface basierende Kommunikation für die Anwendung innerhalb der Magnetstromregelung zu langsam ist. Es wurde außerdem ein weiterer Ansatz implementiert, der unter der Nutzung des vollen AXI4-Interfaces die Daten in Bursts überträgt. Dabei konnte eine deutliche Verbesserung der Übertragungsgeschwindigkeit festgestellt werden. Allgemein stellt die Arbeit eine funktionierende Datenkommunikation und einen Ansatz für die Verbesserung deren Übertragungsgeschwindigkeit mit Burst-Transaktionen bereit.

# 1.2. Abstract

For the implementation of a magnet-current-control, the development platform Mercury XU5 by Enclustra was set up. A data communication was established on the System on Chip between the FPGA and the Processing-System running a Linux operating system. The main requirement was the evaluation of the timing performance of the data transmission, as it has to meet the real-time requirement of the control loop. The data communication was built by using the AXI GPIO IP core from Xilinx. A Software was written, that reads from and writes to the AXI GPIO core within the Linux operating system. The performance of the data communication was measured by using the Integrated Logic Analyzer from Xilinx. The result was, that the performance of the communication, based on the AXI4-Lite interface is too slow for an application in the magnet-current-control. A second approach was implemented, that uses the full AXI4-Interface and transmits data

in bursts. The approach led to a significant improvement of transfer speed. In general the thesis provides a working data communication and an approach for the improvement of its transfer speed by using burst transactions.

# 2. Einleitung

Das Deutsche Elektronen Synchrotron DESY ist die größte Beschleuniger-Anlage Deutschlands. Der dort gebaute Beschleuniger PETRA III ist seit 2014 eine der brillantesten Röntgenlichtquellen der Welt. Seit einigen Jahren werden nun jedoch die Beschleuniger auf der ganzen Welt weiter ausgebaut. Das Ziel des Ausbaus sind Röntgenlichtquellen 4. Generation. Diese neue Technologie soll den Röntgenstrahl noch weiter fokussieren, sodass auch Strukturen im Nanobereich aufgelöst werden können. Auch DESY ist in den Umbau zu Röntgenlichtquellen 4. Generation eingestiegen und möchte mit dem neuen Beschleuniger PETRA IV ein 3D-Röntgenmikroskop der Superlative bauen. Das PE-TRA IV-Projekt hat das Ziel den PETRA III-Beschleuniger in eine "ultra-low-emittance"-Röntgenlichtquelle umzubauen. Die Emittanz ist charakteristisch für einen Beschleuniger, da sie von den Störgrößen, die auf die Elektronen im Speicherring einwirken, abhängig ist. Das Ziel ist es den Röntgenstrahl annähernd auf das Beugungslimit fokussieren zu können. Das Beugungslimit beschreibt den kleinsten Abstand, den zwei Objekte zueinander haben dürfen, um noch als zwei separate Objekte von einem Röntgenstrahl mit diskreter Wellenlänge aufgelöst werden zu können. Für Energien von bis zu 10 keV soll PETRA IV eine Auflösung nahe dem Beugungslimit erreichen und damit einen extrem kohärenten Röntgenstrahl erzeugen können. Um bei Energien von bis zu 10 keV das Beugungslimit zu erreichen wird eine Emittanz von kleiner gleich 10 pm rad benötigt. Die vertikale Emittanz von PETRA III beträgt 10 pm rad. Die horizontale Emittanz liegt mit 1300 pm rad jedoch deutlich über dem für die Erreichung des Beugungslimits benötigtem Wert. Das Ziel von PETRA IV ist es eine horizontale Emittanz von 10 bis 20 pm rad zu erhalten.

Um dies zu erreichen wird der gesamte Beschleuniger PETRA III umgebaut. Es werden neue Experimentierhallen, neue Beamlines und ein neues Magnetsystem entwickelt und gebaut. In PETRA IV sollen 2562 Magneten und 700 Korrektur-Magneten eingebaut werden. Eine solche Menge an Magneten erfordert außerdem eine hohe Anzahl an Netzteilen für die Magnetstromversorgung. Die Regelkomponenten für die Überprüfung dieser werden vom DESY selbst entwickelt, da diese zu den sogenannten "accuracy-defining components" gehören. Die Kontrolle der Netzteile und die Beobachtung sämtlicher Regelparameter soll über Ethernet vorgenommen werden.<sup>1</sup>

Für die Umsetzung dieser unterschiedlichen Funktionalitäten wie die Implementierung

von Regelungen, die Datenkommunikation über Server und das Nutzen von Ethernet-Schnittstellen innerhalb eines Anwendungsgebiets werden häufig System-on-Chips (SoC) verwendet. Bei einem SoC handelt es sich um die Kombination von Software und Hardware. Die Software ist im CPU-Subsystem untergebracht. Das CPU-Subsystem enthält einen oder mehrere CPU-Kerne, einen On-Chip-Speicher und externe Speicher. Es enthält außerdem Kommunikationsprotokolle wie USB und Ethernet. Die Hardwarekomponente enthält den FPGA (Field Programmable Gate Array). Dabei handelt es sich um Halbleiter-Gerät, dessen Funktion durch programmierbare Logikbausteine konfigurierbar ist. 2-4 Hersteller wir AMD Xilinx oder Intel bieten jeweils eine Reihe von SoCs für unterschiedlichste Anwendungsgebiete, wie Industrie, Medizin, Automobil und Luftfahrt an. 7

Diese Arbeit ist Teil eines großen Projekts zur Neuentwicklung der Magnetstromversorgung für den Beschleuniger Petra IV. Mit dem Ziel die Auflösung des Röntgenstrahls an physikalische Grenzen zu treiben, gilt es in jeder Entwicklungsstufe innovative Technologien zu finden und zu entwickeln. In dieser Arbeit soll die Plattform für die Implementierung der digitalen Magnetstromregelung in Betrieb genommen und vorbereitet werden. Die Aufgabe dieser Arbeit ist die Entwicklung einer Datenkommunikation zur Übertragung der Regelparameter aus dem FPGA des SoCs an den Prozessor. Diese Datenkommunikation soll dabei den speziellen Anforderungen dieses Projekts entsprechen und sich flexibel in die Entwicklung der Magnetstromregelung eingliedern.

# 3. Grundlagen

# 3.1. Mercury XU5

Mercury XU5 ist ein Processing-System der Firma Enclustra. Das Board bietet neben einem System-on-Chip (SoC) weitere Hardware-Komponenten wie DDR4-SDRAM (Double Data Rate 4 - Synchronous Dynamic Random Access Memory), eMMC (embedded Multi Media Card) und QSPI (Quad Serial Peripheral Interface) Flash, Gigabit-Ethernet-PHY (PHYsical Layer) und USB-3.0-PHY.<sup>8</sup>

Um das Mercury XU5 als vollständige Entwicklungsumgebung nutzen zu können, kann es mit einem Baseboard von Enclustra, beispielsweise dem Mercury+ ST1 kombiniert werden.<sup>9</sup>

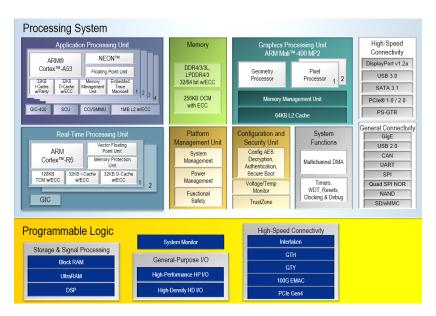

${\it Abb.}$  3.1. Blockdiagramm des Zynq UltraScale+ mit Processing-System und Programmable-Logic $^{10}$

Die Hauptkomponente ist der Zynq Ultrascale+ MPSoC (Multiprozessor-System-on-Chip) von Xilinx. Dieser besteht aus einem Processing-System (PS) und einer Programmable-Logic (PL) (siehe Abb. 3.1).

Das Processing-System ist mit einer Application-Processing-Unit (APU) basierend auf einem quad-core ARM (Advanced RISC Machines) Cortex A53 und einer Real-Time-Processing-Unit (RPU) basierend auf einem dual-core ARM Cortex RF5 ausgestattet.

Die Hauptkomponente der PL-Einheit ist der FPGA. Die PL-Einheit besitzt jedoch auch

eigene Peripheriemodule wie einen 100-GB-Ethernet-PHY. 11-13

### 3.1.1. PS-PL-AXI-Interface

Der Zynq UltraScale+ bietet mehrere General-Purpose-Interconnect-Blöcke für den Daten-Transfer zwischen Processing-System und Programmable-Logic. Für die Verbindung von PL und PS gibt es unter anderem das High-Performance PS-PL-AXI (Advanced eXtensible Interface)-Interface M\_AXI\_HPM\_FPD, welches die Programmable-Logic mit der Full-Power-Domain des Processing-System verbindet. Über dieses kann das Processing-System große Datenmengen zur Programmable-Logic transferieren. Der Interconnect-Block vergibt für diese AXI-Transaktionen (siehe Abschnitt 3.4.3) jeweils IDs, welche die Kohärenz der Daten während des Transfers garantieren.

Für das Debuggen von Applikationen, die eine PS-PL-Kommunikation beinhalten, gibt es einen Debug-Cross-Trigger. <sup>13</sup>

# 3.2. Xilinx Developer Tools

Zur Entwicklung von Designs und der Programmierung des System on Chips von Xilinx gibt es die Xilinx Developer Tools. Die zwei größten Software-Pakete daraus sind die Vivado Design Suite und die Vitis Unified Software Platform.<sup>14</sup>

# 3.2.1. Die Vivado Design Suite

Die Vivado Design Suite ist ein Kombination aus verschiedenen Features zur Erstellung, Implementierung und Validierung von FPGA-Designs. Die Vivado Integrated Design Environment (IDE) bietet eine graphische Nutzeroberfläche für die Entwicklung von Designs. 15 Dort können Quell-Dateien in verschiedenen Hardware-Description-Languages geschrieben werden oder für die gewünschte Funktionalität ein IP-Core eingebunden werden. IP steht für Intellectual Property und beschreibt die Zusammenfassung von fertigen Subsystemen in direkt anwendbaren Cores. 3,16 Diese können mit dem IP-Integrator-Tool<sup>17</sup> aus dem Vivado-IP-Katalog ausgewählt und in das FPGA-Design eingebunden werden. Das FPFA-Design wird in der IDE mit Hardware Description Languages auf Register-Transfer-Ebene beschrieben. Vivado beinhaltet Synthese-Tools, die fertige Designs auf Register-Transfer-Ebene in eine Repräsentation auf Gate-Ebene, also eine Beschreibung durch weniger abstrakte, logische Gatter, umwandeln.  $^{3,18}$  Durch die Synthese entstehen Netzlisten, die als Eingangsprodukt für die Implementierung genutzt werden. Die Implementierung besteht aus der Optimierung der Logik, Platzierung von logischen Zellen und dem Routen von Verbindungen zwischen diesen Zellen.<sup>19</sup> Nach der Implementierung kann der Bitstream erzeugt werden. Mit dieser .bit-Datei wird der FPGA mit dem erstellten Design programmiert.<sup>20</sup> Das Design kann in Form einer HardwareSpecification-Datei, oder auch .xsa-Datei (Xilinx Shell Archive) exportiert werden, um in Vitis auf Basis des FPGA-Designs Software zu erstellen.<sup>21</sup>

### 3.2.2. Die Vitis Unified Software Platform

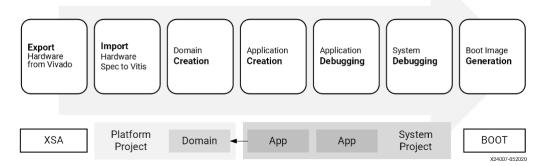

Die Vitis Unified Software Platform fasst alle Software-Entwicklungs-Tools von Xilinx zusammen. Mit der Vitis Integrated Design Environment (IDE) können Software-Applikationen für Xilinx-Embedded-Prozessoren entwickelt werden. Die Entwicklung von Sotware für SoCs geschieht über das Platform-Projekt und das System-Projekt (siehe Abb. 3.2).

Abb. 3.2. Vitis Workflow mit Platform-Projekt und System-Projekt<sup>21</sup>

Das Platform-Projekt beinhaltet die Hardware-Informationen und wird auf Basis der aus Vivado exportieren .xsa-Datei erstellt. Innerhalb des Platform-Projekts kann nun ein System-Projekt erstellt werden, in welchem wiederum Application-Projekte erstellt werden können. Ein Apllication-projekt enthält die Quell- und Header-Dateien für das Projekt. Durch die Kompilierung des Application-Projekts wird eine binäre Output-Datei erstellt, die .ELF-Datei. Diese kann auf dem Prozessor ausgeführt werden.<sup>21</sup>

# 3.3. Embedded Linux auf dem Zynq UltraScale+

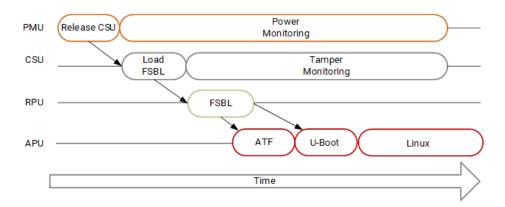

Der Zynq UltraScale+ bootet im Multi-Stage-Boot-Modus. Während des Bootvorgangs des Systems erfüllen mehrere Komponenten unterschiedliche Aufgaben und bereiten jeweils die Umgebung für die folgende Komponente vor. Der Zynq UltraScale+ bietet verschiedene Boot-Devices von denen gebootet werden kann: JTAG (Joint Test Action Group), SD-Speicherkarte (Secure Digital Memory Card), QSPI-Flash, eMMC-Flash. Zu Beginn des Boot-Vorgangs (siehe Abb. 3.3) wird anhand der Device-Mode-Pins der eingestellte Boot-Modus ausgelesen. Die Configuration-Security-Unit (CSU) kopiert den First-Stage-Boot-Loader (FSBL) vom Boot-Device in den On-Chip-Random-Access-Memory (OCM). Die APU führt den FSBL aus und initialisiert somit den RAM-Controller. Der FSBL lädt den Second-Stage-Boot-Loader (SSBL) in den RAM. Bei einem Embedded Linux auf dem Zynq UltraScale+ handelt es sich bei dem SSBL um den Boot-Loader

*Abb.* 3.3. Bootvorgang auf dem Zynq UltraScale+<sup>22</sup>

U-Boot.<sup>23,24</sup> Der FSBL konfiguriert außerdem die PL mit dem Bitstream. Der U-Boot Boot-Loader lädt den Linux-Kernel, den Devicetree und andere Dateien in den RAM und führt den Linux-Kernel aus. Der Linux-Kernel konfiguriert dann weiterführend die Peripheriemodule und das User-Space-Root-File-System und führt die Init-Applikation aus. Die Init-Applikation führt wiederum User-Space-Applikationen aus.<sup>11,22,25,26</sup>

### 3.3.1. Der Devicetree

Der Devicetree ist eine Struktur, die für das Betriebssystem nicht-detektierbare Hardware beschreibt. Die Hardware-Systeme werden in der Devicetree-Spezifikation auch Devices genannt. Im Devicetree gibt es jeweils Einträge für diese Devices, die in einer baumartigen Struktur angeordnet sind. So ein Eintrag wird auch Node genannt. Jede Node legt sogenannte Properties für das Device fest, welche bestimmte Eigenschaften des Gerätes beschreiben.<sup>27,28</sup>

# 3.4. Das AXI-Protokoll

Das AXI (Advanced eXtensible Interface)-Protokoll ist ein Interface-Protokoll aus dem AMBA (Advanced Microcontroller Bus Architecture)-Standard von ARM. Dieser spezifiziert Protokolle für die Kommunikation auf SoCs.<sup>29</sup>

Das AXI-Protokoll legt zwei Arten von Interfaces fest: das AXI-Manager-Interface und das AXI-Subordinate-Interface. Eine AXI-Verbindung besteht immer zwischen diesen beiden Interfaces. Damit zwei Komponenten über das AXI-Protokoll kommunizieren können, muss eine Komponente ein AXI-Manager-Interface und die andere Komponente ein AXI-Subordinate-Interface aufweisen.<sup>30</sup>

Im weiteren Verlauf der Arbeit werden mit den Begriffen AXI-Manager und AXI-Subordinate auch die Komponenten, die diese Interfaces beinhalten gemeint.

# 3.4.1. Die Kanäle des AXI-Interfaces

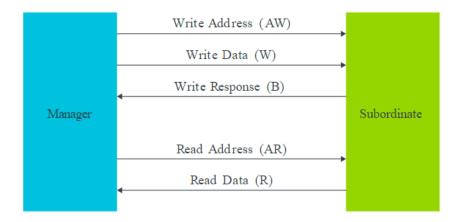

Das AXI-Interface definiert fünf Kanäle: Drei Kanäle für einen Schreibzugriff und zwei Kanäle für einen Lesezugriff (siehe Abb. 3.4). Für beide Zugriffe gibt es jeweils einen Adress-Kanal und einen Datenkanal. Der AXI-Manager sendet vor dem Senden der Daten die zu beschreibende oder auszulesende Adresse und weitere Kontrollsignale über den Adresskanal (AW bzw. AR) zum AXI-Subordinate. Diese Aktion wird als Request bezeichnet.

Bei einem Lesezugriff sendet das AXI-Subordinate die Daten über den separaten Datenkanal (R) von der angefragten Adresse zum AXI-Manager. Über denselben Kanal sendet das Subordinate eine Leseantwort, die den Abschluss des Lesevorgangs signalisiert. Bei einem Schreibzugriff werden die Daten über den Datenkanal (W) zum AXI-Subordinate geschrieben. Das Subordinate schreibt die erhaltenen Daten dann an die angefragte Adresse.

Da die Kanäle unidirektional sind und über den Datenkanal (W) nur Daten vom Manager zum Subordinate geschrieben werden können, benötigt der Schreibvorgang einen weiteren Kanal (B). Auf diesem teilt das Subordinate mit der Schreibantwort dem Manager mit, dass der Vorgang korrekt beendet wurde. 30,31

Abb. 3.4. Kanäle des AXI-Interface zwischen AXI-Manager und AXI-Subordinate<sup>30</sup>

# 3.4.2. Der AXI-Handshake

Jede Kommunikation auf einem AXI-Kanal beruht auf dem AXI-Handshake-Prinzip. Dieser Handshake wird zwischen dem AXI-Manager und dem AXI-Subordinate mittels der Signale READY und VALID ausgeführt. Das VALID-Signal wird von der Quelle auf HIGH gesetzt, wenn die zu schreibenden Daten korrekt und zum Schreib- bzw. Lesevorgang bereit sind. Die Quelle setzt das READY-Signal auf HIGH, wenn sie bereit ist neue Daten zu empfangen. Sowohl AXI-Manager, als auch AXI-Subordinate können Quelle und Ziel sein, je nachdem, ob es sich um einen Schreib- oder Lesevorgang handelt. Beim

Schreibvorgang ist der Manager die Quelle und beim Lesevorgang ist es das Subordinate. Wenn beide Signale HIGH sind kommt es zum sogenannten Transfer. Ein Transfer ist im AMBA-AXI-Protokoll als einzelner Informationsaustausch auf einem Kanal über einen einzigen READY-VALID-Handshake definiert.<sup>31,32</sup>

### 3.4.3. Die AXI-Transaktion

Die gesamte Kommunikation zwischen Manager und Subordinate, die einen Adresskanal und einen Datenkanal benötigt, über den ein oder mehrere Datentransfers geschehen, wird Transaktion genannt.

Der Ablauf von mehreren Datentransfers in einer Transaktion wird als Burst bezeichnet. Im Burst-Modus ist es möglich, dass nach einem einzigen Adresstransfer mehrere Datentransfers folgen. Dazu sendet der AXI-Manager nur die Adresse für den ersten Datentransfer und das AXI-Subordinate berechnet die Adressen für die darauffolgenden Datentransfers.

Für die Burst-Transaktion gibt es drei Kontrollsignale, die während des Requests an das AXI-Subordinate gesendet werden. Das Signal AWBURST/ARBURST gibt an, wie die Adressen der nachfolgenden Datentransfers berechnet werden. Das Signal AWLEN/ARLEN gibt die Anzahl der Datentransfers an. Die maximale Anzahl an Bytes, die pro Datentransfer übertragen wird, wird von dem Signal AWSIZE/ARSIZE angegeben. 31,32

### 3.4.4. Das AXI-Interconnect

Um zwei Komponenten über das AXI-Protokoll miteinander zu verbinden, wird ein AXI-Interconnect benötigt. Dabei handelt es sich um eine weitere Komponente, die mindestens ein Manager- und mindestens ein Subordinate-Interface besitzt. Das Interconnect wird jeweils über das AXI-Manager- und AXI-Subordinate-Interface mit den anderen beiden Komponenten verbunden<sup>30</sup> (siehe Abb. 3.5).

Das Interconnect zwischen der AXI-Manager-Komponente und der AXI-Subordinate-Komponente übernimmt in der Datenkommunikation verschiedene Aufgaben. Das AXI-Protokoll unterstützt die Kommunikation zwischen zwei Komponenten, die einen unterschiedlich großen Adressraum haben. Bei der Datenübertragung zwischen solchen Komponenten muss das Interconnect die fehlerfreie Übertragung gewährleisten.

Ein Interconnect kann mit mehreren Managern und Subordinates verbunden sein. Es muss den korrekten Ablauf der Transaktionen regeln, damit die Transaktion jeweils mit den zusammengehörigen Komponenten geschieht.

Interconnects machen es außerdem möglich, dass Manager mehrere Anfragen hintereinander losschicken können. Dafür enthalten die Kanäle des Interfaces das sogenannte Transaction-Identifier-Signal. Dadurch kann der Manager eine weitere Transaktion beginnen, bevor die vorherige abgeschlossen ist. Das Interconnect ordnet die angeforderten

**Abb. 3.5.** Verbindung einer AXI-Manager-Komponente und einer AXI-Subordinate-Komponente mit einem AXI-Interconnect<sup>30</sup>

Transaktionen anhand der ID und garantiert so die korrekte Beendigung jeder Transaktion.<sup>31</sup>

# 3.5. Unterarten des AXI-Protokolls

Der AMBA-Standard spezifiziert unter anderem drei Arten von AXI-Interfaces: AXI4, AXI4-Lite und AXI4-Stream. AXI4-Lite ist eine Unterart von AXI4 und implementiert nicht alle Signale des AXI-Protokolls. Der wichtigste Unterschied zu AXI4 ist, dass das AXI4-Lite-Interface keine Bursts unterstützt. Die Datenübertragung mit diesem Interface ist auf einen Datentransfer pro Transaktion beschränkt. Das AXI4-Interface dagegen kann bis zu 256 Datentransfers pro Transaktion ausführen.<sup>33</sup>

# 3.5.1. Memory-Mapped-Protokolle

Bei AXI4 und AXI4-Lite handelt es sich um Memory-Mapped-Protokolle. Diese Protokolle zeichnen sich dadurch aus, dass sie vor einem Datentransfer eine Adresse an das Subordinate senden. Die Daten werden in einem bestimmten Bereich des Speichers, der sogenannten Memory-Map gespeichert<sup>33</sup> (siehe Abschnitt 3.6.1). Bei einem Burst-Transfer wird nicht der Memory-Map-Speicher genutzt, sondern der interne Speicher.<sup>34</sup>

### 3.5.2. Das AXI-Stream-Interface

Das AXI4-Stream-Interface ist kein Memory-Mapping-Protokoll. Es verwendet nur einen unidirektionalen Kanal, auf dem Daten vom AXI-Manager zum AXI-Subordinate gesendet werden können. Dabei kann das AXI4-Stream-Interface Bursts von uneingeschränkter Länge streamen. Da es das Senden der Adresse und weiterer Kontrollsignale einspart, kann es hohe Übertragungsgeschwindigkeiten erreichen.<sup>33</sup>

# 3.6. Der AXI-GPIO-Core

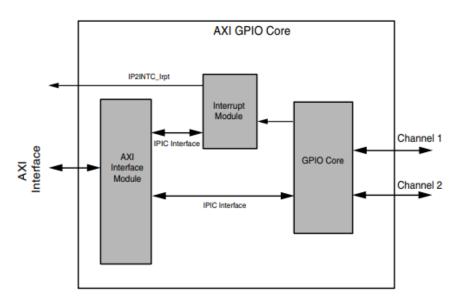

AMD Xilinx hat das AXI-Interface adaptiert und in mehreren IP-Cores umgesetzt.<sup>33</sup> Der AXI-GPIO ist ein IP-Core von Xilinx. Er bildet ein Interface zwischen General Purpose In– und Outputs und dem AXI4-Lite-Interface. Der IP-Core besteht aus drei Komponenten, einem AXI-Interface-Modul, einem GPIO-Core und einem Interrupt-Modul (siehe Abb. 3.6).

Das AXI-Interface-Modul verbindet den GPIO-Core mit dem AXI-Subordinate-Interface des AXI-GPIO-Cores über das AXI4-Lite-IP-Interface (IPIF).<sup>35</sup>

Der GPIO-Core kann Interrupt-Signale an den Prozessorkern senden. Wenn ein Interrupt an einem der Eingangs-Ports des GPIO-Cores auftritt, wird dieses Signal zum Interrupt-Modul gesendet. Das Interrupt-Modul besitzt die entsprechenden Register, um Interrupts global und lokal zu aktivieren und den Status der Interrupts zu verwalten. <sup>36</sup>

Abb. 3.6. Blockdiagramm des AXI-GPIO-IP-Cores<sup>36</sup>

### 3.6.1. Der GPIO-Core

Der GPIO-Core stellt zwei Kanäle mit einer Breite von 32 Bit zur Verfügung. Diese sind jeweils einzeln konfigurierbar und können als Ein- der Ausgänge genutzt werden. Um beide Kanäle nutzen zu können, muss der Dual-Channel-Modus aktiviert werden. Wie in Abbildung 3.7 zu erkennen besitzen beide Kanäle jeweils zwei Register: das GPIO\_DATA-Register und das GPIO\_TRI-Register (3-State-Register).

Bei einem Schreibzugriff auf den GPIO-Core werden die Daten vom Eingang des Cores im GPIO\_DATA-Register gespeichert. Bei einem Lesezugriff werden die Daten aus dem Register am Ausgang des GPIO-Cores zur Verfügung gestellt.

Mithilfe des GPIO\_TRI-Registers können alle 32 möglichen Ports individuell als Ein-

| Base Address + Offset (hex) | Register<br>Name | Access<br>Type | Default<br>Value (hex) | Description                         |

|-----------------------------|------------------|----------------|------------------------|-------------------------------------|

| C_BASEADDR + 0x00           | GPIO_DATA        | Read/Write     | 0x0                    | Channel 1 AXI GPIO Data Register    |

| C_BASEADDR + 0x04           | GPIO_TRI         | Read/Write     | 0x0                    | Channel 1 AXI GPIO 3-state Register |

| C_BASEADDR + 0x08           | GPIO2_DATA       | Read/Write     | 0x0                    | Channel 2 AXI GPIO Data Register    |

| C_BASEADDR + 0x0C           | GPIO2_TRI        | Read/Write     | 0x0                    | Channel 2 AXI GPIO 3-state Register |

Abb. 3.7. Register des GPIO-Cores<sup>36</sup>

oder Ausgang konfiguriert werden.

Das AXI4-Lite-Interface des AXI-GPIO-Cores ist ein Memory-Mapping-Interface. Die Register befinden sich in einem bestimmten Bereich im Speicher, der sogenannten Memory Map. Die Adresse dieses Bereichs wird durch das Attribut C\_BASEADDR festgelegt. Die Register befinden sich an festen Offsets dieser Basisadresse. Die Register von solchen Peripherie-Modulen wie dem GPIO-Core werden als Memory-Mapped-I/O (MMIO) bezeichnet. Diese Art von Speicher wird auch oft als Device Memory bezeichnet, dabei handelt es sich um Speicher für Peripheriemodule. 33,36

# 4. Anforderungsanalyse

# 4.1. Übergeordnetes System

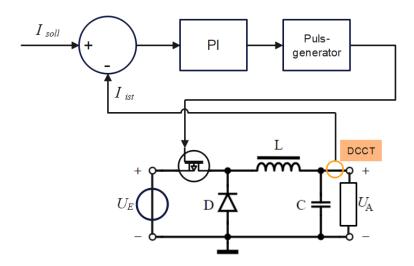

Die Magneten des Beschleunigers werden von Leistungsnetzteilen mit Strom versorgt. Da die induzierten Magnetfelder hochgenaue Anforderungen erfüllen müssen, muss dieser Strom präzise¹ geregelt werden (siehe Abb. 4.1). Dazu wird der Strom am Magneten mit einem hochpräzisen Stromsensor, einem DCCT-Sensor³7 (Direct-Current Current Transformer) gemessen. Nach der Strommessung wird das Signal mittels eines ADCs digitalisiert und in die digitale Magnetstromregelung eingespeist. Dort wird zunächst die Abweichung des erfassten Ist-Stroms vom Soll-Strom berechnet. Diese Abweichung wird einem PI-Regler zugeführt, welcher eine Stellgröße ausgibt und diese an einen Pulsgenerator weiterleitet. Dieser generiert aus der Stellgröße ein Pulssignal mit dem Tastverhältnis  $\alpha$ , welches an den MOSFET des Tiefsetzstellers angelegt wird. Der MOSFET wird entsprechend des Pulssignals geschaltet und es ergibt sich somit die benötigte Stromstärke  $I = \frac{\alpha \cdot U_{\rm E}}{R_{\rm Last}}$  am Magneten.

**Abb. 4.1.** Übergeordnetes System Magnetstromregelung mit PI-Regler, Pulsgenerator, DCCT-Sensor und Tiefsetzsteller<sup>38</sup>

Zur Umsetzung der in Abbildung 4.1 gezeigten Regelung wird im Beschleuniger PETRA III ein SoC von Altera<sup>39</sup> genutzt. Im Rahmen der Neuentwicklung der digitalen Magnetstromregelung für den Beschleuniger PETRA IV soll ebenfalls ein SoC genutzt werden,

<sup>&</sup>lt;sup>1</sup>Abweichung vom Sollwert < 10 ppm

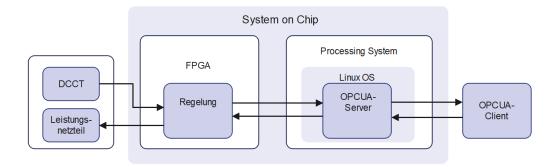

um diese darauf zu implementieren. Die Stromregelung soll dabei auf dem FPGA des SoCs implementiert werden, da so eine höhere Schnelligkeit der Regelung erreichbar ist. Die Ausgangswerte des Stromsensors sollen dort eingelesen werden und dienen als Eingang für den Regelkreis. Um die Ausgangsdaten der Regelung für Benutzer\*innen sichtbar zu machen, soll auf dem Prozessorkern ein Server implementiert werden. Für die Implementierung dieses Servers wurde der Standard OPCUA<sup>40</sup> gewählt, um die Übertragung von Informationen auf dem ganzen DESY-Gelände zu vereinheitlichen. Auf dem Prozessorkern soll ein Betriebssystem installiert werden, das als Grundlage für den OPCUA-Server und den Zugriff auf die Daten im FPGA dient.

Von der Messung des Magnetstroms bis zur Ausgabe der Regelungsparameter in einem Clientprogramm spannt sich somit, wie in Abbildung 4.2 zu sehen eine Kette der Datenkommunikation auf.

Abb. 4.2. Funktionale Kette der Datenkommunikation

# 4.2. Stakeholderanalyse

Die funktionale Kette der Datenkommunikation bildet verschiedene Funktionen ab, welche in den Verantwortungsbereichen unterschiedlicher Stakeholder liegen. Aus der Stakeholder-Analyse ergeben sich die Anforderungen an die aufzustellende Datenkommunikation.

# 4.2.1. Entwickler der Magnetstromregelung auf dem FPGA

Aus der Analyse des ersten Stakeholders gehen die funktionalen Anforderungen an die Datenkommunikation hervor (siehe Tabelle 4.2). Die Regelung befindet sich aktuell noch in der Entwicklungsphase, daher ist die Art der Implementierung noch nicht eindeutig festgelegt. Sie soll entweder vollständig auf dem FPGA implementiert oder teilweise auf den Prozessor ausgelagert werden.

Um die Flexibilität für die Entwicklung der Regelung zu bewahren, soll während dem Entwurf der Datenkommunikation davon ausgegangen werden, dass ein Teil der Regelung auf den Prozessorkern ausgelagert wird und die Datenkommunikation den zeitlichen Anforderungen der Regelung genügen muss.

Die Regelung selbst unterliegt einer harten Echtzeitanforderung, welche bei der Implementierung der Datenkommunikation beachtet werden muss. Der Takt der Regelung beträgt 132 kHz. Dieser Wert muss genauestens eingehalten werden, damit die Schaltfrequenz andere Systeme nicht stört. Im Falle einer zum Teil auf den Prozessorkern ausgelagerten Regelung, muss die Datenkommunikation zwischen FPGA und Prozessorkern ebenfalls diesen Echtzeitanforderungen genügen. Die zu verarbeitenden Signale müssen vom FPGA zum Prozessorkern gesandt, dort entsprechend verarbeitet und zurück zum FPGA gesendet werden. Zum aktuellen Stand der Entwicklung liegen noch keine genaueren Informationen über die zeitliche Performance der Regelung selbst vor. Es wird lediglich als Schätzwert vorgegeben, dass die Kommunikation nicht mehr als 1/20 des Taktes der Regelung in Anspruch nehmen soll. Damit muss die Datenkommunikation zwischen FPGA und Prozessorkern für den Hin- und Rückweg insgesamt schneller als  $\frac{1}{20} \cdot \frac{1}{132kHz} \approx 0,38~\mu s$  sein.

Innerhalb eines jeden Taktes der Regelung muss eine bestimmte Datenmenge zwischen FPGA und Prozessorkern hin und her gesendet werden. Der Prozessorkern benötigt vom FPGA die aktuellen Strom- und Spannungswerte und Statuswerte. An den FPGA werden Sollwerte, Statuswerte und weitere Regelparameter gesendet. Diese Werte müssen jeweils pro Regelungstakt zum Prozessorkern gesendet, dort verarbeitet und dem Regelkreis auf dem FPGA wieder zur Verfügung gestellt werden. Zum aktuellen Stand der Entwicklung ist noch nicht bekannt wie viele Daten, in welcher Dimension jeweils pro Takt versendet werden müssen. Es wurden Schätzwerte, wie in Tabelle 4.1 zu sehen für den Entwurf der Datenkommunikation vorgegeben. Diese Schätzwerte enthalten einige Datenworte der Größe 32 Bit und 16 Bit, welche Stromwerte, Spannungswerte oder andere größere Daten der Berechnung bzw. Regelung repräsentieren. Außerdem wird der Gebrauch von vielen 1-Bit-großen Datenworten für Status- und Steuersignale vermutet.

| Anzahl der zu übertragenden Daten | Größe der Datenwörter in Bit |

|-----------------------------------|------------------------------|

| 10                                | 32                           |

| 5                                 | 16                           |

| 50                                | 1                            |

Tab. 4.1: Pro Regelungstakt zu übertragendes Datenvolumen

Die beschriebenen Anforderungen des Stakeholders sollen in der zu entwickelnden Datenkommunikation umgesetzt werden. Dazu sollen geeignete Kommunikationsinterfaces gefunden werden. Die zeitliche Performance der aufzustellende Datenkommunikation soll, insbesondere bezüglich der teilweisen Auslagerung der Regelung auf den Prozessorkern, untersucht werden.

| Stakeholder          | Entwickler der Magnetstromregelung auf dem FPGA           |

|----------------------|-----------------------------------------------------------|

|                      | • Flexibilität und Erweiterbarkeit der Datenkommunikation |

|                      | • Implementierung und Validierung verschiedener           |

|                      | Kommunikationsinterfaces                                  |

| Anforderungen an die | • Implementierung der Datenkommunikation für teilweise    |

| Datenkommunikation   | Auslagerung der Regelung auf den Prozessor                |

| Datenkonimunikation  | • Echtzeitanforderung an Datenkommunikation <0,38 μs      |

|                      | • Festgelegtes Datenvolumen pro Regelungstakt             |

|                      | • Untersuchung der zeitlichen Performance der             |

|                      | Datenkommunikation                                        |

Tab. 4.2: Stakeholderanalyse - Entwickler der Magnetstromregelung auf dem FPGA

# 4.2.2. Entwickler der allgemeinen Magnetstromversorgung

Aus der Analyse des zweiten Stakeholders gehen die nicht-funktionalen Anforderungen hervor (siehe Tab. 4.3). Diese ergeben sich im Wesentlichen aus der Tatsache, dass ein Beschleuniger ein Großprojekt ist, welches viele materielle und finanzielle Ressourcen beansprucht. Da die zuverlässige Funktion der Anlage von den verbauten Komponenten abhängig ist, muss garantiert werden, dass diese auch auf lange Zeit die gewünschte Funktionalität liefern. Das obsolet werden von Softwarekomponenten könnte in diesem Fall zur Gefährdung der zuverlässigen Funktion der Gesamtanlage führen. Aus diesem Grund soll es sich bei dem Betriebssystem auf dem Prozessorkern um eine Linuxversion handeln. In der Vergangenheit sei es oft zu Problemen mit erzwungenen Updates von Closed-Source-Betriebssystemen gekommen. Der vollständig vorliegende Source-Code ermöglicht außerdem eine auf das spezielle System zugeschnittene Konfigurierung. Jedoch stellte sich zu Beginn des Projekts die Frage, ob und wie gut sich die gewünschte Funktionalität auch ohne Betriebssystem auf dem SoC umsetzen lässt. Daher soll bei der Entwicklung die Implementierung und Nutzung mit und ohne Betriebssystem durchgeführt und evaluiert werden.

In der bisherigen Magnetstromregelung wurde als Hardware-Description-Language  $AHDL^{41}$  verwendet. Für die neue Magnetstromregelung soll die relativ neue Sprache SystemVerilog<sup>42</sup> verwendet werden.

Mit diesen beiden Anforderungen soll vor allem garantiert werden, dass die Anlage auch im Verlaufe der nächsten Jahre betriebsfähig ist und nicht aufgrund veralteter Betriebssysteme und Programmiersprachen funktionsunfähig wird.

Die Programmiersprache für die Software auf dem Processing System soll C++ sein, da der Code des OPCUA-Servers, der später dort implementiert werden soll ebenfalls in C++ geschrieben wurde. Die objektorientierte Programmiersprache eignet sich außerdem sehr gut für die Anwendung in einem solch großen Projekt wie diesem. Die Abstraktion erlaubt, dass verschiedene Teile der Software von verschiedenen Teams erstellt und

später zusammengestellt werden können.

| Stakeholder                                | Entwickler der allgemeinen Magnetstromversorgung |

|--------------------------------------------|--------------------------------------------------|

| Anforderungen an die<br>Datenkommunikation | • Betriebssystem: Linux                          |

|                                            | • HDL: SystemVerilog                             |

|                                            | • Programmiersprache: C++                        |

Tab. 4.3: Stakeholderanalyse: Entwickler der allgemeinen Magnetstromversorgung

# 4.2.3. Projektleiter der Magnetstromversorgung

Der dritte Stakeholder (siehe Tab. 4.4), der Projektleiter der Magnetstromversorgung muss garantieren, dass der finanzielle und zeitliche Rahmen des Projekts eingehalten wird. Aufgrund der aktuellen Marktlage der letzten Jahre gab es oft Beschaffungsprobleme von elektronischen Komponenten. Für die Neuentwicklung der Magnetstromversorgung soll daher sichergestellt werden, dass die Gruppe nicht abhängig von einer Plattform ist. Die Magnetstromregelung von PETRA III wurde mit einem SoC von Altera umgesetzt. Für die Neuentwicklung soll nun neben Altera auch ein SoC von Xilinx in Betrieb genommen und so eine mögliche Ausweichoption geschaffen werden. Zu diesem Zweck soll das SoC-Modul Mercury XU5 von Enclustra in Betrieb genommen und hinsichtlich des Einsatzes im beschriebenen System (siehe Abschnitt 4.1) untersucht werden.

| Stakeholder          | Projektleiter der Magnetstromversorgung                   |

|----------------------|-----------------------------------------------------------|

| Anforderungen an die | • Entwicklungsplattform: Mercury XU5 mit Zynq UltraScale+ |

| Datenkommunikation   | MPSoC von AMD Xilinx                                      |

Tab. 4.4: Stakeholderanalyse: Projektleiter der Magnetstromversorgung

# 4.3. Zusammenfassung des Anforderungen

Aus der Stakeholder-Analyse gehen die Anforderungen für diese Bachelorarbeit hervor. Zwischen FPGA und Processing-System auf der Platform Mercury XU5 ist eine Datenkommunikation zu implementieren. Dazu soll ein geeignetes Kommunikationsinterface gefunden, implementiert und evaluiert werden. Das Interface soll bidirektional Daten zwischen den beiden Einheiten übertragen. Dabei müssen große Datenmengen innerhalb von 0,38 µs vom Processing-System ausgelesen und wieder zum FPGA geschrieben werden können. Bei der Hardware-Description-Language soll es sich um SystemVerilog handeln.

Auf dem Prozessorkern ist ein Linux-Betriebssystem zu installieren. Auf diesem soll eine Software die Lese- und Schreibbefehle zum FPGA ausführen. Dabei soll die Programmiersprache C++ genutzt werden. Während des gesamten Arbeitsprozesses sollen

die Unterschiede zwischen der Implementierung des Interfaces mit und ohne Linux-Betriebssystem untersucht werden. Die aufgestellte Datenkommunikation soll bezüglich Der Eignung für die teilweise Auslagerung der Regelung auf den Prozessorkern auf ihre zeitliche Performance untersucht werden.

# 5. Konzept

Um die Aufgabenstellung zu erfüllen, soll eine Datenkommunikation entworfen und implementiert werden, die im Hinblick auf den Einsatz im besprochenen System (siehe Abschnitt 4.1) bewertet werden soll. Für die Implementierung soll nun ein Konzept entworfen werden, welches zum Ziel hat die besprochenen Anforderungen zu erfüllen.

# 5.1. Die Xilinx Entwicklungsumgebung

Im Rahmen der Bachelorarbeit soll die Plattform Mercury XU5 in Betrieb genommen und die Xilinx-Umgebung als mögliche Ausweichoption für spätere Projekte untersucht werden. Daher sollen für die Entwicklung der Datenkommunikation die Developer Tools von Xilinx genutzt werden.

Mit der Vivado Design Suite und dem dazugehörigen IP-Integrator soll das FPGA-Design erstellt und synthetisiert werden. Für das Software-Design soll das Tool Vitis Unified Software Platform genutzt werden. Mit dem zuvor in Vivado generierten Hardware-Specification-File können dort auf Basis des FPGA-Designs Platform-Projekte erstellt werden. So kann in daraufhin erstellten Application-Projekten auf die Hardware zugegriffen werden. Für das Application-Projekt ist als Grundlage ein C++-Projekt auszuwählen. So werden beim Build des Application-Projekts die C++-Bibliotheken automatisch eingebunden. In Vitis kann für Bare-Metal-Projekte ein Boot-Image erstellt werden,<sup>21</sup> sodass das fertige Projekt inklusive Bitstream und C-Code aus Vitis heraus auf den SoC geladen werden kann.

Für die Inbetriebnahme mit Linux ist das Konzept ähnlich. Das Boot-Image wird separat mit der Enclustra Build Environment erstellt (siehe Abschnitt 5.5). Bei dem in Vitis zu erstellenden Platform-Projekt muss lediglich Linux als Betriebssystem ausgewählt werden. Beim Build des Application-Projekts wird dann von Vitis eine .ELF-Datei erstellt. Dies ist eine ausführbare Datei und kann in das Linux-Filesystem auf dem Prozessorkern geladen und dort ausgeführt werden.

Für das Laden von solchen Linux-Applications auf den Prozessorkern soll aufgrund der Schnelligkeit Ethernet genutzt werden. Dies hat den Vorteil, dass während dem Testen von Software die SD-Karte (siehe Abschnitt 5.5) nicht ständig zwischen SoC und Entwicklungs-PC hin- und her gesteckt werden muss. Des Weiteren wird für die Ent-

wicklung ein Windows-PC verwendet. Daher soll für den Transfer die Software Win-SCP<sup>43</sup> genutzt werden. Diese ermöglicht es von einem Windows-PC über die IP-Adresse eine remote Verbindung zum SoC aufzubauen und Dateien zu senden.

# 5.2. Das AXI-Interface

Zwischen FPGA und Prozessorkern soll ein fortlaufender Datenaustausch stattfinden. Dazu muss ein Kommunikationsinterface zwischen diesen beiden Einheiten aufgebaut werden, mit welchem Daten in beide Richtungen übertragen werden können. Xilinx bietet für den Austausch von Daten zwischen einem Manager und einem Subordinate das AXI4-Interface an. Das AXI-Interface teilt sich in drei Unterarten auf: AXI4-Stream, AXI4 und AXI4-Lite.

AXI4-Stream ist das schnellste Interface, da es im Gegensatz zu den beiden anderen ohne Memory-Mapping arbeitet und so das Übertragen einer Adressphase einspart. Jedoch ist AXI4-Stream nur unidirektional nutzbar und kommt daher für den bidirektionalen Austausch zwischen FPGA und Prozessorkern nicht in Frage.

AXI4 und die vereinfachte Version AXI4-Lite arbeiten mithilfe von Memory-Mapping und weisen daher eine etwas niedrigere Übertragungsgeschwindigkeit, als AXI4-Stream auf. Die Übertragung der Adressphase hat jedoch den Vorteil, dass sie bidirektional Daten übertragen können.

AXI4-Lite beinhaltet nur einen Teil der Kontrollsignale des AXI-Protokolls. Es ist daher nur zur Ausführung von einem Datentransfer pro Transaktion fähig. Jedoch nimmt es weniger Platz in einem FPGA-Design ein und ist einfacher in dieses einzubinden. Das AXI4 (full)-Interface unterstützt alle Kontrollsignale des AXI-Protokolls und ist daher detaillierter zu konfigurieren. Dies geht mit höherer Performance aber auch einem komplexeren FPGA-Design einher. Es ist außerdem dazu in der Lage mehrere Datenwörter innerhalb einer Transaktion zu übertragen.

Für den Aufbau der Datenkommunikation zwischen FPGA und Processing System soll zunächst das AXI4-Lite-Interface genutzt werden, da die Implementierung dessen sowohl im FPGA-Design als auch in der Software auf dem Processing System weniger komplex ist.

# 5.3. Das AXI-Subordinate

Das AXI-Interface wird zwischen einem AXI-Manager und einem AXI-Subordinate aufgebaut. Der AXI-Manager ist der Prozessorkern. Er sendet Lese- und Schreibbefehle an das AXI-Subordinate. Diese Befehle sollen Daten aus der Regelung auslesen und ihr Da-

ten zur Verfügung stellen. Es muss also ein Logikmodul auf dem FPGA erstellt werden, in welchem später die Regelung implementiert werden kann. Um die Funktionalität und Performance der Datenkommunikation feststellen zu können, soll in diesem Modul eine simple Logik aufgebaut werden. Diese Logik soll Daten vom Eingang des Subordinate erhalten, diese mit zwei multiplizieren und wieder an den Ausgang des Moduls legen. Die Logik soll deshalb so simpel sein, da die Performancemessungen der Datenkommunikation nicht durch etwaige Zeitverzögerungen einer zu komplexen Beispiellogik beeinflusst werden sollen.

Damit das Modul als AXI-Subordinate vom AXI-Manager angesprochen werden kann, benötigt es ein AXI-Interface.

Xilinx bietet verschiedenen IP-Cores an, die zur Datenübertragung über das AXI-Interface entwickelt wurden. Zum einen gibt es für das Transferieren von Daten zwischen dem internen Speicher des SoC und dem FPGA den AXI-GPIO-IP-Core. Dieser dient als Interface zwischen General-Purpose-Ein- und Ausgängen eines Peripheriemoduls und dem AXI4-Lite-Interface und nimmt die Rolle des AXI-Subordinate ein.

Der AXI-Manager kann somit die Register des AXI-Subordinates, also des AXI-GPIO auslesen und beschreiben. Die Ein- und Ausgänge des IP-Cores, bei denen es sich nicht um AXI-Interface-Ports handelt, werden mit den Ein- und Ausgängen des Logik-Moduls verbunden. So kann die Software auf dem Prozessorkern über den AXI-GPIO-IP-Core mit der Logik auf dem FPGA kommunizieren.

Das AXI-GPIO-Modul kann im Dual-Channel-Modus konfiguriert werden. Ein Channel wird mit dem Eingang, der zweite Channel mit dem Ausgang des Logik-Moduls verbunden. Dies dient sowohl der Übersicht im FPGA-Design, als auch in der Software. Bei der Nutzung mehrerer AXI-GPIOs kann somit eine Zugehörigkeit von bestimmten Ports bzw. Größen zueinander geschaffen werden, indem sie mit demselben AXI-GPIO verbunden sind.

Ein weiterer IP-Core von Xilinx, welcher Daten vom Systemspeicher zu Peripheriemodulen überträgt, ist der AXI-DMA. Dieser kann Daten über ein Memory-Mapped-AXI-Interface vom Processing-System empfangen oder zu diesem senden. Über ein Memory-Mapped-to-Stream-Interface werden diese Daten dann zu einem Peripheriemodul geschrieben bzw. über ein Stream-to-Memory-Mapped-Interface von diesem gelesen. Auf diese Weise können große Datenmengen direkt aus dem Hauptspeicher an das Peripheriemodul übertragen werden. Um auf dieser Art Daten an das Logik-Modul übertragen zu können, benötigt dieses ein AXI-Stream-Interface, mit welchem der DMA kommunizieren kann. Diese Übertragungsart beinhaltet die Konfigurierung vieler Komponenten, wie dem AXI-DMA und dem Memory-Controller. Außerdem muss im Logik-Modul ein AXI-Wrapper geschrieben werden, damit zwischen den Komponenten eine AXI-Kommunikation stattfinden kann. Aus diesem Grund wird die Datenübertragung

mit dem AXI-DMA-IP-Core in dieser Arbeit nicht näher untersucht.

Als AXI-Subordinate wird an dieser Stelle daher der AXI-GPIO-IP-Core für den Aufbau der Datenkommunikation gewählt. Bei dieser Art der Datenkommunikation ist lediglich der AXI-GPIO-Core zu konfigurieren, welcher außerdem bereits ein Interface zwischen den Ein- und Ausgängen des Peripheriemoduls und dem AXI-Interface bietet.

# 5.4. Der AXI-Manager

Der Prozessor soll Daten vom AXI-Subordinate lesen, diese verarbeiten und Daten zurück zum AXI-Subordinate senden. Daher muss eine Software geschrieben werden, die auf dem Prozessorkern ausgeführt wird und von dort aus Lese- und Schreibbefehle an das AXI-Subordinate senden kann. Dazu muss die Software einen Zugriff auf das zuvor erstellte FPGA-Design haben, um in bestimmten Adressbereichen Daten zu lesen und zu schreiben. Das in dem FPGA-Design implementierte AXI-GPIO-Modul muss in der Software konfiguriert werden. Der Adressbereich des Moduls und die Datenrichtung der Channel muss festgelegt werden.

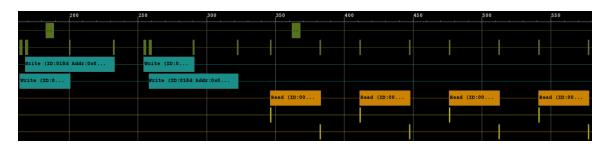

Da das AXI-Manager-Interface des Processing-Systems ein AXI4(-full)-Interface ist, soll auch das Schreiben von Daten im Burst-Modus und damit eine andere Art von Speicherzugriff, als beim AXI-GPIO-Core implementiert und getestet werden.

Für die Nutzung des AXI-GPIO-Moduls mit und ohne Betriebssystem müssen jeweils verschiedene Programme geschrieben werden. Der Zugriff ohne ein Betriebssystem auf die Register des Moduls geschieht mithilfe von Xilinx-Libraries.

Wird die Software in einem Betriebssystem ausgeführt, müssen Linux-Driver genutzt werden, um auf die Register zugreifen zu können. Die zu manipulierenden Register des AXI-GPIO-Moduls müssen zuvor in ein virtuelles Linux-Filesystems exportiert werden, um diese von der Software beschreiben zu können.

# 5.5. Das Linux-Betriebssystem

Auf dem Prozessorkern soll später ein OPCUA-Server laufen. Für dessen Implementierung wird ein Linux-Betriebssystem benötigt. Dieses soll auf dem SoC installiert werden. Xilinx bietet zwar auch an dieser Stelle Unterstützung durch ihre PetaLinux-Tools, <sup>46</sup> jedoch soll zur Erstellung des Embedded Linux an dieser Stelle das Tool Enclustra Build Environment (EBE) genutzt werden. Für den Build eines Embedded Linux-Systems werden hardwarespezifische Dateien wie beispielsweise Device-Tree-Files benötigt. Da es sich bei dem vorliegenden System um ein SoC von Enclustra handelt, ist dieses Tool zur ersten Inbetriebnahme des Boards mit Linux die bessere Wahl. Das Tool greift auf ein GitHub-Repository <sup>48</sup> zu, in welchem alle benötigten hardwarespezifischen Dateien

zur Generierung des Boot-Images für alle Enclustra Targets vorliegen. Die EBE erstellt auf Basis der hardwarespezifischen Dateien ein Boot-Image für das Booten des SoC in Linux. Das Target, der Boot-Modus und die benötigten Boot-Dateien sind in einer GUI einfach auszuwählen. Ein weiterer Vorteil ist die Anpassungsmöglichkeit an rekonfigurierte Hardware. Die Bitstream-Datei kann in der GUI einfach gegen selbst geschriebene Bitstream-Files ausgetauscht werden. Wenn im Nachhinein eine andere Linuxversion verwendet werden soll, kann das Image ausgetauscht und so in einer anderen Version gebootet werden.

Zunächst können so alle benötigten Dateien zum Booten in Linux für das Reference Design für die Mercury-XU5-ST1-Plattform<sup>49</sup> erstellt werden. Nach dem Hinzufügen von weiterer Hardware, wie dem AXI-GPIO-Modul muss das Device-Tree-File um diesen erweitert werden, damit vom Linux-Betriebssystem auch diese nicht detektierbare Hardware manipuliert werden kann.

Als Boot-Medium soll während der Entwicklung die SD-Karte verwendet werden. Diese bietet die Möglichkeit Dateien schnell auszutauschen und im SoC zu testen. Dies kann sich während der Entwicklung als sehr nützlich erweisen, da währenddessen aufgrund von Änderungen am FPGA-Design das Boot-Image ständig erneuert werden muss. Im späteren Betrieb eignen sich dann andere Boot-Modi wie beispielsweise QSPI-Flash besser, da dieser eine höhere Bootgeschwindigkeit aufweist<sup>50</sup> und SD-Karten eine beschränkte Lebensdauer besitzen.

# 5.6. Validierung der Datenkommunikation

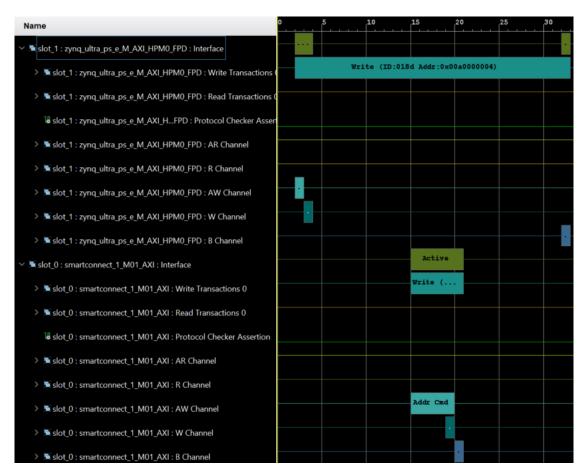

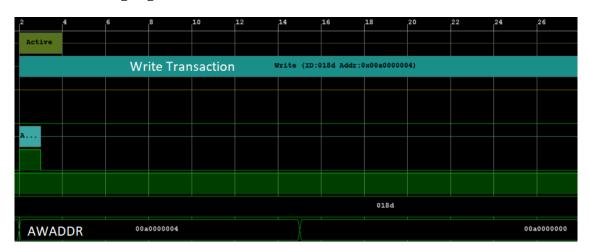

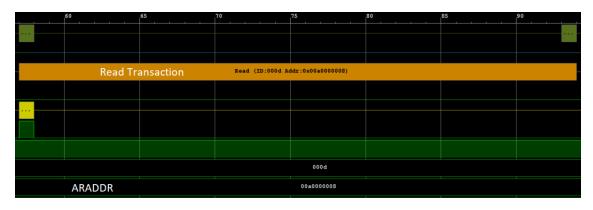

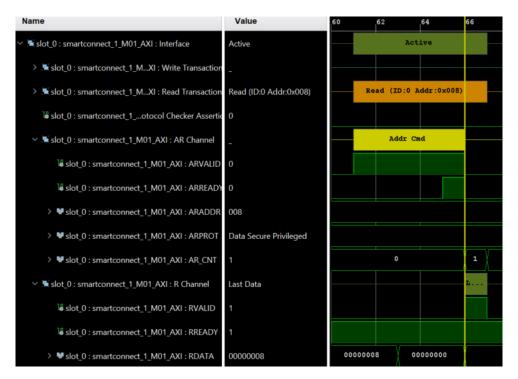

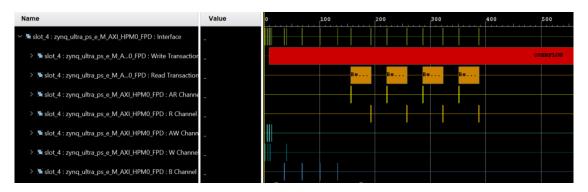

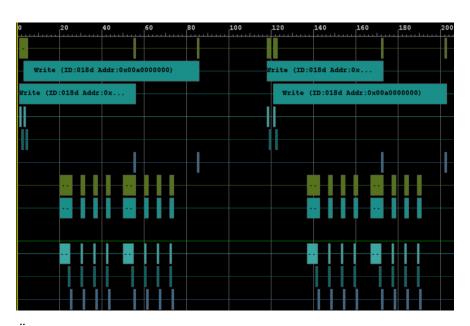

Um die entwickelte Datenkommunikation bewerten zu können, soll die Funktionalität und die Performance dieser gemessen werden. Zunächst soll die Funktion des AXI-Protokolls zwischen AXI-Manager und AXI-Subordinate verifiziert werden. Dazu soll der korrekte Ablauf der Adress- und Datenphasen und der Verlauf der Signale auf den fünf AXI-Kanälen untersucht werden. Für diesen Zweck soll das Tool Integrated-Logic-Analyzer<sup>51</sup> genutzt werden. Bei diesem handelt es sich um einen IP-Core von Xilinx, welcher in das zu untersuchende FPGA-Design eingefügt wird. Die zu untersuchenden Signale werden dazu an die Slots des ILA-Cores angeschlossen. Die Software kann anschließend von Vitis aus gestartet werden. In Vivado können im Hardwaremanager über ein Waveform-Fenster alle Signale beobachtet werden, die mit dem ILA-Core verbunden wurden. Die Messung muss dabei plattformübergreifend gestartet werden, da der Befehl des Hardwarezugriffs auf dem Prozessorkern geschieht, während sich das AXI-Subordinate auf dem FPGA befindet.

Um mit dem ILA-Core die Funktionalität des AXI-Interfaces zu verifizieren, muss der

ILA-Core jeweils an die Signale zwischen AXI-GPIO und SmartConnect und zwischen SmartConnect und Zynq-Processeing-System angeschlossen werden. Mit dieser Konfigurierung können die Signale des AXI-Interfaces entlang der gesamten Datenkommunikation zwischen AXI-Manager und AXI-Subordinate untersucht werden. Auch der zeitliche Verlauf der Signale des AXI-Protokolls kann mit dem ILA-Core beobachtet werden, da die x-Achse des Waveform-Windows den Takten des Clock-Signals des ILA-Cores entspricht. Daher muss der ILA-Core mit demselben Clock-Signal verbunden werden, wie das System, dass beobachtet werden soll.<sup>52</sup>

Außerdem soll der zeitliche Einfluss des Hardwarezugriffs vom Prozessor untersucht werden. Dabei soll besonders auf den Unterschied des Zugriffs mit und ohne Betriebssystem geachtet werden.

Zur Messung dieses Unterschieds wird im Logikmodul des FPGAs ein Counter implementiert, der die Taktzyklen während einer Lese- und Schreibtransaktion zählt. Diese Lese- und Schreibtransaktion wird dann auf dem Prozessorkern mit und ohne Linux-Betriebssystem ausgeführt.

# 6. Implementierung

Die Datenkommunikation zwischen Processing System und Programmable-Logic wird nun auf Grundlage des entworfenen Konzepts implementiert.

# 6.1. Erstellung der Entwicklungsumgebung

Zur Implementierung der entworfenen Datenkommunikation sollen die Xilinx Developer Tools verwendet werden. Der Entwurf des FPGA-Designs erfolgt mit der Vivado Design Suite. Um Hardwarekomponenten zu designen und das Logik-Modul zu schreiben, muss zunächst ein Projekt in Vivado erstellt werden, das auf der board-spezifischen Hardware des Mercury XU5 basiert. Für die Erstellung dieses Projekts wird das Reference Design von Enclustra genutzt. Das dazugehörige GitHub-Repository enthält die dazu nötigen TCL-Skripte und das Haupt-VHDL-Modul Mercury\_XU5\_ST1.vhdl,<sup>49</sup> welches den Mercury XU5 beschreibt. Die TCL-Skripte (Tool Command Language) erstellen mithilfe des VHDL-Moduls und weiteren Konfigurationsdateien ein Projekt, in dem die VHDL-Datei und ein Blockdesign der Hardware des Reference Designs vorliegt.

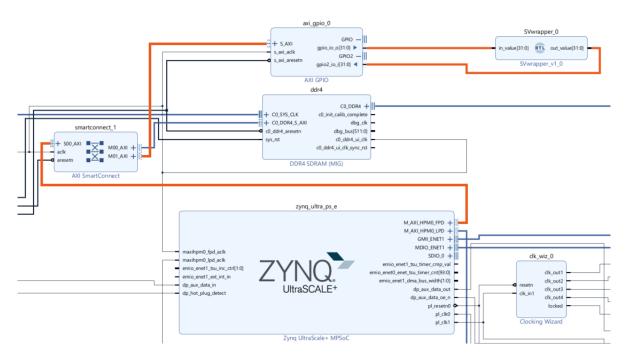

Die Hauptkomponente des Blockdesigns ist das Processing System, das durch den PS UltraScale+ Block (siehe Abb. 6.1) repräsentiert wird. Dieser besitzt bereits einige nach außen geführte Signale wie unter anderem Taktsignale und ein AXI-Manager-Interface.

Abb. 6.1. PS-UltraScale+ -Block aus dem Vivado-Blockdiagramm<sup>49</sup>

# 6.2. Erstellung eines Logik-Moduls

Die Regelung soll auf dem FPGA in SystemVerilog implementiert werden. Dazu wird eine weitere Quell-Datei zum Projekt hinzugefügt, in der später die Regelung implementiert werden kann. Um eine vollständige Kommunikation aufzubauen, wird an dieser Stelle stellvertretend für die Regelung eine simple Logik implementiert, die die Eingangsdaten mit zwei multipliziert und wieder ausgibt.

Die genutzt Version Vivado 2022.1 unterstützt im Allgemeinen die Synthese von System-Verilog, jedoch können mit System-Verilog keine Top-Level-RTL-Module definiert werden. Daher wird zusätzlich ein Verilog-Wrapper geschrieben. Dahei handelt es sich um eine weitere Quell-Datei, die die zuvor geschriebene System-Verilog-Datei als Modul instanziiert. Die Ein- und Ausgänge des System-Verilog-Moduls werden dahei den Ein- und Ausgängen des Verilog-Wrappers zugeordnet. Im weiteren Verlauf der Arbeit wird die Gesamtheit dieser beiden Module als Logik-Modul bezeichnet.

# 6.3. Implementierung der AXI-Kommunikation mit dem AXI-GPIO

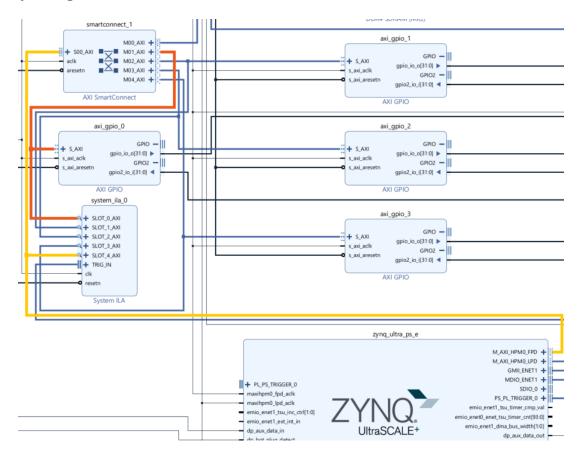

Das FPGA-Design enthält nun die beiden Komponenten, zwischen welchen die Datenkommunikation aufgebaut werden soll. Der Block des Processing Designs besitzt bereits ein AXI-Manager-Interface. Damit das Processing System mit dem Logik-Modul kommunizieren kann, benötigt dieses ein AXI-Subordinate-Interface. Daher wird der AXI-GPIO-IP-Core in das Blockdesign eingefügt. Dieser wird zunächst entsprechend der Anforderungen konfiguriert. Um beide GPIO-Kanäle nutzen zu können, wird der Dual-Channel-Modus freigeschaltet. Für die Datenbreite der Kanäle wird 32 Bit eingestellt. Der erste Kanal wird als Ausgang und der zweite Kanal als Eingang konfiguriert.<sup>53</sup> Die GPIO-Ports des AXI-GPIO-Cores werden mit den Ein- und Ausgängen des Logik-Moduls verbunden. Der Ausgang wird mit einem Eingang des Logik-Moduls verbunden, sodass das Processing-System über den AXI-GPIO-Core Daten an dieses senden kann. Der Eingang des AXI-GPIO-Cores wird mit dem Ausgang des Logik-Moduls verbunden. Auf diese Weise kann das Processing-System Daten von diesem auslesen. Für die Verbindung mit dem Processing System wird die Auto-Connect-Funktion von Vivado genutzt. 15 Beim Ausführen dieser Funktion werden das Taktsignal s\_axi\_aclk, das Resetsignal s\_axi\_aresetn und das AXI-Interface S\_AXI automatisch mit dem Processing System verbunden (siehe Abb. 6.2). Bei der automatischen Verbindung zwischen AXI-Manager und AXI-Subordinate wird ein AXI-Smartconnect im Blockdesign generiert. Dies ist eine neue Version des AXI-Interconnects, welche zwei Blöcke mit Managerund Subordinate-Interface miteinander verbindet.<sup>54</sup>

Abb. 6.2. Ausschnitt des Blockdiagramms mit Zynq UltraScale+, SmartConnect, AXI-GPIO-Core und Logik-Modul

Die Anforderungen an die Datenkommunikation sehen die Übertragung eines gewissen Datenvolumens innerhalb eines Regelzyklus vor. Daher muss auf der Seite des Subordinate eine Struktur geschaffen werden, die diesen Datensatz empfangen kann. Die Daten müssen über diese Struktur vom AXI-Manager wieder ausgelesen werden können. Ein einzelner AXI-GPIO-Core eignet sich dazu nicht. Der AXI-Manager könnte zwar viele Daten hintereinander an den AXI-GPIO-Core senden, jedoch besitzt dieser nur zwei GPIO-Ports. Diese sind mit dem Logik-Modul verbunden, welches die Daten vom AXI-GPIO-Core annehmen bzw. an diesen ausgeben soll. Bei den übertragenden Daten handelt es sich jedoch um verschiedene Größen (siehe Abschnitt 4.2.1), die getrennt voneinander abgespeichert werden müssen. Es müsste daher im Logik-Modul eine Logik implementiert werden, die die Daten von diesen zwei Ports annimmt und richtig sortiert abspeichern kann. Für Lesezugriffe müssten diese Daten ebenfalls koordiniert an die zwei GPIOs des AXI-GPIO-Core ausgegeben werden. Eine solche Logik wäre sehr unübersichtlich und unflexibel in der Anwendung.

Daher werden, wie in Abbildung 6.3 zu sehen, mehrere AXI-GPIO-Cores implementiert, sodass das Logik-Modul einen festen Eingang für jede zu sendende Größe hat. Jeder Einund Ausgang wird entsprechend mit einem GPIO-Port vom AXI-GPIO-Core verbunden.

Im SystemVerilog-Modul (Abb. 6.4) und im Verilog-Wrapper-Modul (Abb. 6.5) werden entsprechend Ein- und Ausgänge ergänzt.

**Abb. 6.3.** Ausschnitt des Blockdiagramms mit SmartConnect, vier AXI-GPIO-Cores und Verbindung zum Logik-Modul

```

25 :

30 module CommunicationSV(

26

31

27 '

32

input clk,

28

33

input logic [31:0] data in 1,

29

34

input logic [31:0] data in 2,

30

35

input logic [31:0] data_in_3,

31 !

36

input logic [31:0] data_in_4,

32

37

output logic [31:0] data_out_1 = 0,

33

38

output logic [31:0] data_out_2 = 0,

34

39

output logic [31:0] data_out_3 = 0,

35

40

output logic [31:0] data out 4 = 0

36 🖯

41

37

38

43 D

always @(posedge clk)

39

44 🖨

begin

40

45

data_out_1 <= data_in_1 * 2;

41

46

data_out_2 <= data_in_2 * 2;

42

47

data_out_3 <= data_in_3 * 2;

43

48

data_out_4 <= data_in_4 * 2;

44

49 🖨

45

50

46

51 endmodule

```

Abb. 6.4. SystemVerilog-Modul

```

23 module SVwrapper(

24

input wire clk in,

input wire [31:0] in_1,

input wire [31:0] in 2,

input wire [31:0] in 3,

input wire [31:0] in_4,

output wire [31:0] out_1,

output wire [31:0] out_2,

output wire [31:0] out_3,

output wire [31:0] out_4

CommunicationSV Instance_0

.clk(clk in),

.data in 1(in 1),

.data in 2(in 2),

.data_in_3(in_3),

.data_in_4(in_4),

.data_out_1(out_1),

.data_out_2(out_2),

.data_out_3(out_3),

.data_out_4(out_4)

47 🖨

48 endmodule

```

**Abb. 6.5.** Verilog-Wrapper für SystemVerilog-Modul

Um vom Processing System auf das zuvor generierte FPGA-Design zugreifen zu können, muss das Design in Vivado synthetisiert und ein Bitstream generiert werden. Die Hardware kann inklusive Bitstream in Form einer .xsa-Datei aus Vivado exportiert werden. Diese wird für die PS-Programmierung in Vitis benötigt. Der Bitstream wird außerdem nochmal separat aus Vivado exportiert, da dieser für die Erstellung eines Boot-Images

gebraucht wird.

# 6.4. Generierung des Linux-Boot-Image

Um das Processing-System mit einem Linux-Betriebssystem booten zu können, muss zuvor ein Boot-Image erstellt werden. Dazu wird das Tool Enclustra Build Environment genutzt. Es bietet ein Graphical User Interface (GUI) und ein Command Line Interface (CLI). In der GUI wird zunächst der Zynq UltraScale+, der Mercury XU5 und das Baseboard ST1 ausgewählt. Als Boot-Device wird die Multi Media Card (MMC) ausgewählt. In der Enclustra Build Environment können die zu erstellenden Boot-Dateien ausgewählt werden für den Fall, dass bei späteren Anpassungen nur bestimmte Dateien neu erstellt werden müssen. Für die erste Generierung des Boot-Images werden die Boot-Targets Linux, U-Boot und Buildroot<sup>55</sup> ausgewählt. Im nächsten Schritt wird der Bitstream des erstellten FPGA-Designs gegen die Default-Bitstream-Datei ausgetauscht. Mit diesen Einstellungen wird das Boot-Image generiert und die entstehenden Dateien werden in einen Output-Ordner abgelegt. Der Output-Ordner enthält unter anderem fünf Dateien, die für den Boot in einem Linux-Betriebssystem von der SD-Karte notwendig sind. Die Datei boot.bin enthält unter anderem den FSBL und den Bitstream. Die Datei Image enthält den Linux-Kernel<sup>26</sup> und die Datei rootfs.tar enthält das Linux-File-System. Außerdem werden die Datei devicetree.dtb und uboot.scr benötigt.

Auf der SD-Karte werden zwei Partitionen erstellt. Die erste Partition wird FAT-formatiert (File Allocation Table) und bildet die Boot-Partition, auf der die boot.bin-Datei, das Image, der Devicetree und die uboot.scr-Datei kopiert werden. Die zweite Partition wird ext4-formartiert und die rootfs.tar-Datei wird dorthin entpackt.<sup>48</sup>

Während der Implementierung stellte sich heraus, dass das Linux-File-System den zweiten Kanal eines AXI-GPIO-Cores zwar erkennen, aber nicht beschreiben oder auslesen kann. Daher wird das in Abschnitt 6.3 erstellte FPGA-Design so angepasst, dass die vier AXI-GPIO-Cores nur im Single-Channel-Modus betrieben werden. Zwei AXI-GPIO-Cores werden als Ausgang und die zwei anderen als Eingang genutzt.

### 6.4.1. Anpassung des Devicetree

Da im Vergleich zum Reference-Design, auf welchem die Default-Boot-Dateien basieren, Veränderungen im FPGA-Design vorgenommen wurden, muss der Devicetree dahingehend angepasst werden. Bei dem AXI-GPIO-IP-Core handelt es sich um für das Betriebssystem nicht-detektierbare Hardware, daher muss dieser dem Devicetree hinzugefügt werden. Unter der übergeordneten Node amba\_pl wird eine weitere Node für den AXI-GPIO-Core erstellt (siehe Abb. 6.6). Dieser Node muss als erstes die Adresse der Hardware zugewiesen werden. Für den AXI-GPIO-Core handelt es sich dabei um die Basisadresse des GPIO-Cores.

Der Eigenschaft #gpio-cells wird der Wert 2 zugewiesen. Dieser Wert gibt an, wie viele Attribute angegeben werden müssen, wenn auf diese AXI-GPIO-Node beispielsweise im Rahmen einer Child-Node verwiesen werden sollte. Der Eigenschaft compatible werden mehrere Strings übergeben, die die Kompatibilität mit anderen Devices ausdrücken und dem System dazu dienen, passende Driver für das Device zu finden. Der Node muss außerdem das Attribut gpio-controller zugewiesen werden, welches diesen als ein GPIO-Device kennzeichnet, welches mehrere GPIO-Signale beinhaltet. Die Eigenschaft reg legt die Adresse und die Länge des Adressbereiches für das Device fest. Dort wird die Basis-Adresse und außerdem die Differenz von High Address und Base Address aus dem Vivado-Address-Editor angegeben. Darunter folgen Eigenschaften, die der Konfiguration des AXI-GPIO-IP-Cores in Vivado entsprechen. 56

```

gpio@a0000000 {

\#gpio-cells = \langle 0x02 \rangle;

compatible = "xlnx,axi-gpio-2.0\0xlnx,xps-gpio-1.00.a";

gpio-controller;

reg = <0x00 0xa0000000 0x00 0x10000>;

xlnx,all-inputs = <0x00>;

xlnx,all-inputs-2 = <0x00>;

xlnx,all-outputs = \langle 0x01 \rangle;

xlnx,all-outputs-2 = <0x00>;

xlnx,dout-default = <0x00>;

xlnx,dout-default-2 = <0x00>;

xlnx,gpio-width = <0x20>;

xlnx,gpio2-width = <0x20>;

xlnx,is-dual = \langle 0x00 \rangle;

xlnx,tri-default = <0xffffffff;</pre>

xlnx,tri-default-2 = <0xffffffff;</pre>

};

```

Abb. 6.6. Node im Devicetree-Code für einen AXI-GPIO-Core

Auf diese Weise werden die vier im FPGA-Design erstellten AXI-GPIO-Cores dem Devicetree zugefügt (siehe vollständigen Devicetree-Code im Anhang).

# 6.5. Programmierung des Processing Systems ohne Linux-Betriebssystem

Auf Basis der zuvor erstellten Hardware-Specification-Datei wird in Vitis ein Platform-Projekt erstellt. Im Feld Operating System wird dabei standalone, also ohne Betriebssystem ausgewählt. Nachdem das Platform-Projekt kompiliert wurde, kann auf Basis dessen ein Application-Projekt erstellt werden. In diesem wird als Grundlage ein C++-Projekt ausgewählt.

# 6.5.1. Programmcode für Single-Data-Transfer-Transaktionen

Für den Zugriff auf die erstellte Hardware ohne Betriebssystem werden Bibliotheken von Xilinx genutzt. Die Header-Datei *xparameters.h.*<sup>57</sup> definiert Makros für Adressen und grundlegende Eigenschaften der Hardwaresysteme. Für den AXI-GPIO-IP-Core ist, wie in Abbildung 6.7 zu sehen, der Adressbereich, basierend auf dessen Basisadresse und Einstellungen wie Interrupts und Dual-Channel-Modus, dort festgelegt.

```

/* Canonical definitions for peripheral AXI_GPIO_0 */

#define XPAR_GPIO_0_BASEADDR 0xA0010000

#define XPAR_GPIO_0_HIGHADDR 0xA001FFFF

#define XPAR_GPIO_0_DEVICE_ID XPAR_AXI_GPIO_0_DEVICE_ID

#define XPAR_GPIO_0_INTERRUPT_PRESENT 0

#define XPAR_GPIO_0_IS_DUAL 1

```

Abb. 6.7. Definition von Makros für den AXI-GPIO-Core 0 in der Datei xparameters.h

Um Daten lesen und schreiben zu können, muss zu Beginn die zu beschreibende Hardware in der Software initialisiert werden. Dazu werden zunächst zwei Variablen vom Typ XGpio erstellt, die für den Eingang bzw. den Ausgang des AXI-GPIO-Cores stehen sollen (siehe Abb. 6.8, Zeile 14 f.). Bei dem Datentyp XGpio handelt es sich um eine Struktur, welche in der Header-Datei xgpio.h definiert wird und die Attribute BaseAddress, IsReady, InterruptPresent und IsDual besitzt. Der Header Xgpio.h definiert außerdem Funktionen um diese Struktur zu bearbeiten. Um den Attributen Werte zuzuweisen, wird die Funktion XGpio Initialize() angewandt (siehe Abb. 6.8, Zeile 20 f.). Der erste Übergabeparameter ist die Adresse der XGpio-Strukturen. Der zweite Parameter ist das Makro XPAR\_AXI\_GPIO\_x\_DEVICE\_ID, welches im Header xparameters.h definiert wird und angibt mit welchem AXI-GPIO die Struktur initialisiert werden soll. Daraufhin wird mit der Funktion XGpio\_SetDataDirection die Datenrichtung für die Struktur festgelegt, dessen Adresse als erste Parameter übergeben wird (siehe Abb. 6.8, Zeile 23 f.). Bei dem zweiten Parameter handelt es sich um den zu nutzenden Kanal des AXI-GPIOs. Der dritte Parameter legt die Datenrichtung fest, wobei 0 für Output und 1 für Input steht. Um Daten zu schreiben, wird die Funktion XGpio\_DiscreteWrite verwendet (siehe Abb. 6.8, Zeile 27). Diese erwartet ebenfalls als ersten Parameter die Adresse auf eine XGpio-Struktur und als zweiten Parameter den zu beschreibenden Kanal des AXI-GPIOs. Der dritte Übergabeparameter ist der zu schreibende Wert. Das Lesen von Daten geschieht mithilfe der Funktion XGpio\_DiscreteRead(). Diese erwartet als ersten Parameter die Adresse einer XGpio-Struktur und als zweiten Parameter die Kanalnummer. Die Funktion gibt die ausgelesenen Daten mit dem Rückgabewert an die Software zurück (siehe Abb. 6.8, Zeile 30 ff).

In Abbildung 6.8 ist die Konfigurierung und das Schreiben und Lesen von Werten bezüglich einem AXI-GPIO als Beispiel dargestellt. Mit den anderen drei AXI-GPIO-Cores wird genauso verfahren (siehe vollständigen Code im Anhang).

```

100 int main()

11 {

12

init platform();

13

14

XGpio input_0;

XGpio output_0;

15

16

int axi_0 = 0;

17

18

19

//configuration of AXI-GPIO 0

XGpio_Initialize(&input_0, XPAR_AXI_GPIO_0_DEVICE_ID);

20

21

XGpio_Initialize(&output_0, XPAR_AXI_GPIO_0_DEVICE_ID);

22

XGpio_SetDataDirection(&input_0,2,1);//instance, channel, direction(1:input, 0:output)

23

24

XGpio SetDataDirection(&output 0.1.0);

25

26

27

XGpio_DiscreteWrite(&output_0, 1, 1);

28

29

30

axi_0=XGpio_DiscreteRead(&input_0,2);

31

32

printf("axi_0: %i\n",axi_0);

33

cleanup_platform();

34

35

return 0;

37 }

```

**Abb. 6.8.** Konfigurierung des AXI-GPIO-Core 0 und Senden von Schreib- und Lesebefehlen

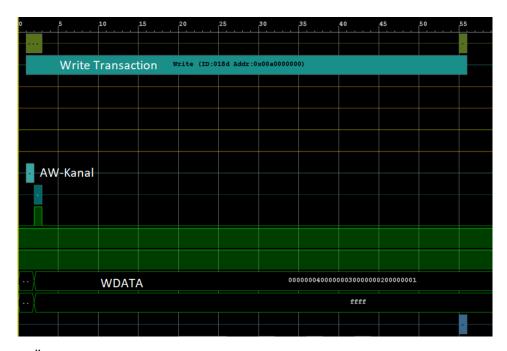

#### 6.5.2. Programmcode für Burst-Transaktionen

Der größte Unterschied zwischen Burst-Transaktion und Single-Transfer-Transaktionen ist der Speicherzugriff. Zuvor wurden die Daten in den Peripherie-Speicher geschrieben. Nun werden sie in den System-Speicher geschrieben. Die Technik des Memory-Caching, also das vorübergehende Speichern von Daten im Hauptspeicher, erlaubt einen schnelleren Zugriff auf die Daten.<sup>34</sup>

Diese Implementierung soll zum Austesten des Burst-Modes auf Seiten des Processing-Systems dienen, da dieses ein AXI4 (full)-Interface besitzt. Der AXI-GPIO-Core unterstützt aufgrund seines AXI4-Lite-Interfaces keine Burst-Transaktionen. Im Folgenden Programmcode wird ein Burst mit der Gesamtlänge 16 Byte, bestehend aus vier Integern (jeweils 4 Byte), zum AXI-GPIO-Core gesendet. Da die Kanäle des AXI-GPIOs nur 32 Bit groß sind, werden sie jeweils sofort überschrieben. Dieses Programm wird nur ausgeführt, um das Verhalten des Processing-Systems zu untersuchen und führt nicht zu validen Daten am AXI-Subordinate.

Zu Beginn des Programms wird zunächst der AXI-GPIO-Core initialisiert und die Datenrichtung festgelegt (siehe Abb. 6.9, Zeile 15 ff).

Um die Datenübertragung beim Lesen und Schreiben jeweils im System-Speicher durchzuführen, wird mit der Funktion malloc() Platz im Speicher, in der Größe der zu übertragenden Daten, reserviert. Der Schreib-Buffer wird mit vier Integern gefüllt, die innerhalb eines Bursts übertragen werden sollen (siehe Abb. 6.10).

Vor der Übertragung wird mit der Funktion Xil\_DcacheEnable() der Daten-Cache akti-

```

//Configuration of AXI-GPIO

XGpio output;

XGpio input;

XGpio input;

XGpio_Initialize(&output, XPAR_AXI_GPIO_@_DEVICE_ID);

XGpio_Initialize(&input, XPAR_AXI_GPIO_@_DEVICE_ID);

XGpio_SetDataDirection(&output, 1, 0);

XGpio_SetDataDirection(&input, 2, 1);

```

Abb. 6.9. Konfiguration des AXI-GPIO 0 für eine Burst-Transaktion

```

//Memory allocation for write and read data

int* write_buffer = (int*)malloc(4*sizeof(int));

if (write_buffer == NULL) {

27

printf("Failed to allocate memory.\n");

28

29

return -1;

30

31

int* read_buffer = (int*)malloc(4*sizeof(int));

32

if (read_buffer == NULL) {

printf("Failed to allocate memory.\n");

34

35

return -1;

36

37

//Filling the write_buffer with example data

38

39

write_buffer[0] = 1;

40

write_buffer[1] = 2;

write_buffer[2] = 3;

41

write_buffer[3] = 4;

42

```

**Abb. 6.10.** Reservierung von Speicher für Schreib- und Lese-Buffer für eine Burst-Transaktion

viert.<sup>58</sup> Die Datenübertragung geschieht durch das Kopieren von Daten aus einem Buffer in einen anderen mithilfe der Funktion memcpy()<sup>33</sup> (siehe Abb. 6.11). Diese erwartet drei Parameter. Der erste Parameter ist ein Pointer auf die Zieladresse, der zweite Parameter ist ein Pointer auf die Adresse der Quelle und der dritte Parameter gibt die Anzahl der insgesamt zu kopierenden Bytes an. Für das Schreiben von Daten wird der Schreib-Buffer als Quelle und der AXI-GPIO-Core als Ziel angegeben. Für das Lesen von Daten wird der AXI-GPIO-Core als Quelle und der Lese-Buffer als Ziel angegeben. In diesem Programm sollen vier Integer mit jeweils 32 Bit in einem Burst übertragen werden. Daher wird als dritter Parameter 4\*4Byte =16 Byte angegeben.

```

//Enabling Data Cache

Xil DCacheEnable();

47

//Write operation

int* src_addr_write = write_buffer;

50

int* dst_addr_write = (int*)(XPAR_AXI_GPIO_0_BASEADDR);

51

memcpy(dst_addr_write, src_addr_write, 16);

53

//Read operation

540

/*int* src_addr_read = (int*)(XPAR_AXI_GPIO_0_BASEADDR+ XGPIO_CHAN_OFFSET*1);

55

int* dst_addr_read = read_buffer;

memcpy(dst_addr_read, src_addr_read, 16);

```

Abb. 6.11. Datenübertragung mit der Funktion memcpy() für eine Burst-Transaktion

# 6.6. Programmierung des Processing-Systems mit Linux-Betriebssystem

Durch das Einstecken der zuvor erstellten SD-Karte mit dem Boot-Image und Anschluss des Boards an die Stromversorgung bootet der Mercury XU5 automatisch in Linux. Im Linux-Datei-System liegen die Applikationen und Hardwaresysteme vor. Die AXI-GPIO-Cores befinden sich im Ordner /sys/class/gpio. Dort liegen sie als Gpio-Chips vor. Jeder Gpio-Chip besitzt n Gpio-Signale, wobei n die Breite des AXI-GPIO-Kanals ist. Um die GPIO-Signale beschreiben und auslesen zu können, müssen diese in das Filesystem sysfs exportiert werden. Dabei handelt es sich um ein Filesystem, welches dazu dient, Devices und ihre Attribute in den User-Space zu exportieren. Dazu wird die Nummer n eines Gpio-Signals in die Datei export des Ordners /sys/class/gpio geschrieben. Im gleichen Ordner erscheint daraufhin ein weiterer Ordner für jedes exportierte Gpio-Signal. Dieser Ordner enthält Dateien für die Datenrichtung und den Wert des GPIO-Signals. Diese können beschrieben und ausgelesen werden. So kann mithilfe des sysfs über den User-Space auf die AXI-GPIO-Cores zugegriffen werden. <sup>59–61</sup>

Wie in Abbildung 6.12 zu sehen kann die Zugehörigkeit der einzelnen gpiochips zu den jeweiligen AXI-GPIO-Cores über die Datei label in jedem gpiochip-Ordner ermittelt werden. Es ist außerdem zu erkennen, dass die Nummern der vier gpiochips jeweils um 32 auseinander liegen. Dazwischen liegen jeweils 32 GPIO-Signale, die die einzelnen Bits repräsentieren.

```

# cat gpiochip480/label

a0000000.gpio

# cat gpiochip448/label

a0010000.gpio

# cat gpiochip416/label

a0020000.gpio

# cat gpiochip384/label

a0030000.gpio

# ■

```

Abb. 6.12. gpiochips und die zugehörigen Basisadressen der AXI-GPIO-Cores

Für das zuvor beschriebene Beschreiben und Auslesen der AXI-GPIO-Cores wird mithilfe der Xilinx Developer Tools eine ausführbare Datei erstellt. Dazu wird in Vitis auf Basis der Hardware-Specification-Datei ein Platform-Projekt erstellt. Dabei wird im Feld Operating System Linux anstatt standalone ausgewählt. Die Erstellung des Application-Projekts erfolgt identisch wie bei der Implementierung ohne Betriebssystem.

Im Programmcode muss zunächst die zuvor beschriebene Exportierung der GPIO-Signale in das sysfs-Filesystem vorgenommen werden (siehe Abb. 6.13, Zeile 22 f.). Daraufhin wird für jedes Signal die Datenrichtung festgelegt (siehe Abb. 6.13, Zeile 25 ff).

Zum Auslesen eines Wertes, der sich aus mehreren Bits, also mehreren GPIO-Signalen, zusammensetzt, wird die Funktion get\_gpio\_value() (siehe Abb. 6.14) genutzt. Diese bekommt als ersten Parameter die Nummer des Gpio-Chips übergeben, welche gleichzeitig

```

char system command export[50];

char system_command_direction[50];

//iteration through 4 AXI-GPIO-Cores = 4*32Bit

for(int i = 384; i <= 511; i ++){

//exporting the gpio signals into sysfs</pre>

20

sprintf(system_command_export, "echo %i > /sys/class/gpio/export",i);

system(system_command_export);