# Hochschule für Angewandte Wissenschaften Hamburg Hamburg University of Applied Sciences

# Bachelorthesis

Safa Camur Entwurf und Aufbau von DC/DC-Stellern

# Safa Camur Entwurf und Aufbau von DC/DC-Stellern

Bachelorthesis eingereicht im Rahmen der Bachelorprüfung im Studiengang Informations- und Elektrotechnik am Department Informations- und Elektrotechnik der Fakultät Technik und Informatik der Hochschule für Angewandte Wissenschaften Hamburg

Betreuender Prüfer: Prof. Dr. -Ing. Gustav Vaupel Zweitgutachter: Prof. Dr. -Ing. Michael Röther

Abgegeben am 24.04.2015

## Safa Camur

## Thema der Bachelorthesis

Entwurf und Aufbau von DC/DC-Stellern

## **Stichworte**

Tiefsetzsteller, Hochsetzsteller, Tief-/Hochsetzsteller

# Kurzzusammenfassung

Diese Bachelorarbeit befasst sich mit der Entwurf und Aufbau eines Tiefsetz-, eines Hochsetz- und eines invertierenden Tief-/Hochsetzstellers für den Praktikumsversuch im Labor für Energietechnik.

## Safa Camur

# Title of the paper

Design and Construction of DC/DC-Converters

# **Keywords**

step-down (buck), step-up (boost), step-up/step-down (buck/boost) converter

#### **Abstract**

The purpose of this report is the design and construction of a Step-Down-, Step-Up-and Step-Down/Step-Up-Converter.

# Inhaltsverzeichnis

| Та | Tabellenverzeichnis                        |    |  |  |

|----|--------------------------------------------|----|--|--|

| ΑŁ | Abbildungsverzeichnis                      |    |  |  |

| 1. | Einleitung                                 | 10 |  |  |

| 2. | Grundlagen                                 | 12 |  |  |

|    | 2.1. Sekundärgetaktete DC/DC-Steller       | 12 |  |  |

|    | 2.1.1. Der Tiefsetzsteller                 | 12 |  |  |

|    | 2.1.2. Der Hochsetzsteller                 | 15 |  |  |

|    | 2.1.3. Der Tief-/Hochsetzsteller           | 17 |  |  |

| 3. | Simulationen                               | 20 |  |  |

|    | 3.1. PORTUNUS                              | 20 |  |  |

|    | 3.2. Simulation des Tiefsetzstellers       | 20 |  |  |

|    | 3.3. Simulation des Hochsetzstellers       | 29 |  |  |

|    | 3.4. Simulation des Tief-/Hochsetzstellers | 34 |  |  |

| 4. | Entwurf und Umsetzung                      | 38 |  |  |

|    | 4.1. Entwurf der Schaltungen               | 38 |  |  |

|    | 4.1.1. CADSoft EAGLE                       | 38 |  |  |

|    | 4.1.2. Überspannungs- und Verpolungsschutz | 38 |  |  |

|    | 4.1.3. Mikrocontroller                     | 39 |  |  |

|    | 4.1.4. Der Tiefsetzsteller                 | 41 |  |  |

|    | 4.1.5. Der Hochsetzsteller                 | 45 |  |  |

|    | 4.1.6. Der Tief-/Hochsetzsteller           | 49 |  |  |

|    | 4.1.7. Überspannungsschutzschaltung        | 50 |  |  |

|    | 4.2. Mikrocontroller-Programmierung        | 52 |  |  |

|    | 4.2.1. Pulsweitenmodulation PWM            | 52 |  |  |

|    | 4.2.2. AD-Wandler                          | 54 |  |  |

| 5. | Verlustleistungen und Wirkungsgrade        | 55 |  |  |

|    | 5.1. Verluste an dem MOSFET                | 55 |  |  |

|    | 5.2. Verluste an der Diode                 | 57 |  |  |

Inhaltsverzeichnis 5

|    | 5.4.                                 | Wirkungsgrad des umgesetzten Tiefsetzstellers                                                                                                                                                                                                                                        | 57<br>59<br>60                                        |

|----|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| 6. |                                      | Versuchsdurchführung Versuchsdurchführung Tiefsetzsteller  6.1.1. Versuchsaufbau  6.1.2. Darstellung der $U_a$ - und $I_a$ -Kennlinien  6.1.3. Zeitliche Verläufe der $U_L$ , $I_L$ , $U_T$ , $I_T$ und $U_D$ , $I_D$ bei $U_e = 12V$ , $f_{Takt} = 18kHz$ und $R_{Last} = 10\Omega$ | 62<br>62<br>63<br>65                                  |

|    | 6.2.                                 | Versuchsdurchführung Hochsetzsteller                                                                                                                                                                                                                                                 | 70<br>70<br>71                                        |

|    | 6.3.                                 | $18kHz \text{ und } R_{Last} = 100\Omega \dots $                                                                                                                               | 74<br>79<br>79<br>80<br>83                            |

|    | Fazi                                 |                                                                                                                                                                                                                                                                                      | 92                                                    |

|    | hang                                 | urverzeichnis                                                                                                                                                                                                                                                                        | 93<br>94                                              |

| An | A.1.<br>A.2.                         | Abkürzungen                                                                                                                                                                                                                                                                          | <ul><li>95</li><li>95</li><li>96</li><li>97</li></ul> |

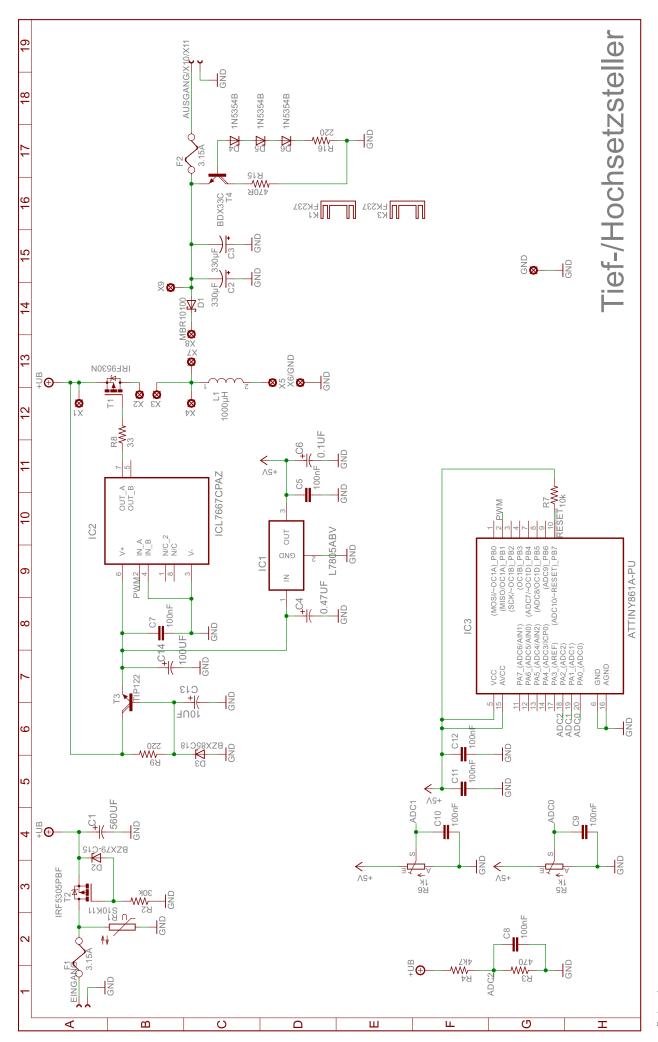

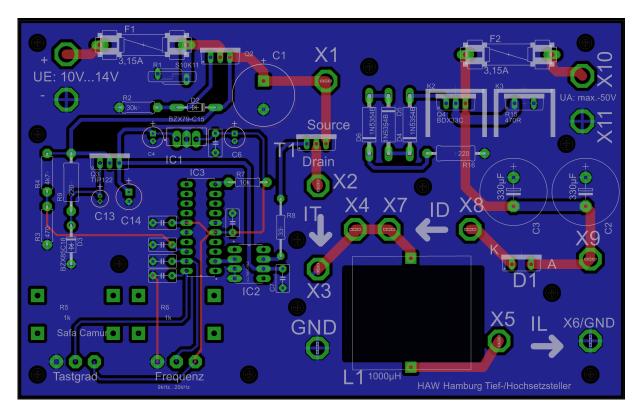

| An | B.1.<br>B.2.<br>B.3.<br>B.4.<br>B.5. | Schaltplan des Tiefsetzstellers                                                                                                                                                                                                                                                      | 99<br>99<br>101<br>101<br>103<br>103<br>105           |

# **Tabellenverzeichnis**

| 4.1. | Tabellarische Auflistung der zum Leistungsteil des Tiefsetzstellers gehören-                                                                                                                                            | 4.4      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 42   | den Bauelemente                                                                                                                                                                                                         | 41<br>44 |

|      | Tabellarische Auflistung der zum Leistungsteil des Hochsetzstellers gehörenden Bauelemente                                                                                                                              | 45       |

| 4.4. | Eckdaten des Hochsetzstellers                                                                                                                                                                                           | 48       |

| 4.5. | Tabellarische Auflistung der zum Leistungsteil des invertierenden Tief-/Hochsetzstellers gehörenden Bauelemente                                                                                                         | 49       |

| 4.6. | Eckdaten des invertierenden Tief-/Hochsetzstellers                                                                                                                                                                      | 50       |

| 5.1. | Gemessene Ein- und Ausgangsstrom für die Berechnung der Ein- und Ausgangsleistung und der Wirkungsgrad des Tiefsetzstellers bei einer Eingangsspannung von $12V$ , einer Ausgangsspannung von $6V$ und einer Schaltfre- |          |

|      | quenz von $18kHz$                                                                                                                                                                                                       | 57       |

| 5.2. | Gemessene Ein- und Ausgangsstrom für die Berechnung der Ein- und Ausgangsleistung und der Wirkungsgrad des Hochsetzstellers bei einer Eingangsspannung von 15V, einer Ausgangsspannung von 30V und einer Schaltfre-     |          |

|      | quenz von $18kHz$                                                                                                                                                                                                       | 59       |

| 5.3. | Gemessene Ein- und Ausgangsstrom für die Berechnung der Ein-<br>und Ausgangsleistung und der Wirkungsgrad des invertierenden Tief-<br>/Hochsetzstellers bei einer Eingangsspannung von $12V$ , einer Ausgangs-          |          |

|      | spannung von $-24V$ und einer Schaltfrequenz von $18kHz$                                                                                                                                                                | 60       |

| 6.1. | Theoretische- und gemessene Ergebnisse bei $f_{Takt} = 18kHz$ und $U_e = 12V$                                                                                                                                           | 64       |

| 6.2. | Theoretische und gemessene Ergebnisse bei $f_{Takt} = 18kHz$ , $R_{Last} = 100\Omega$ und $U_e = 15V$                                                                                                                   | 71       |

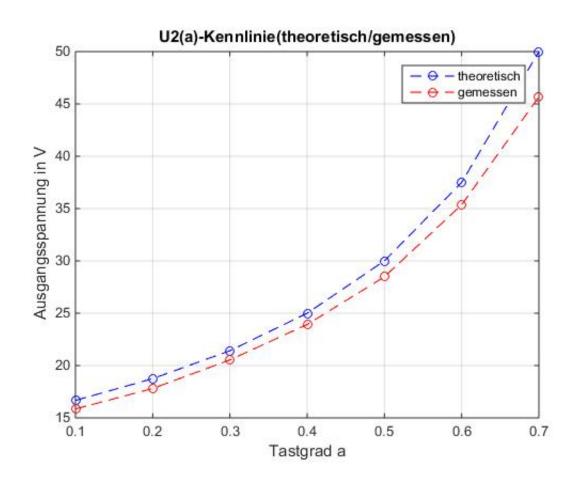

| 6.3. | Theoretische- und gemessene Ergebnisse des invertierenden Tief-                                                                                                                                                         |          |

|      | /Hochsetzstellers bei $f_{Takt} = 18kHz$ und $U_e = 12V$                                                                                                                                                                | 80       |

# Abbildungsverzeichnis

| 2.2. | Prinzipschaltung eines Tiefsetzstellers                                                                                                                                                                                                                                                                                                  | 12<br>15<br>17 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|      | Simulation des Tiefsetzstellers                                                                                                                                                                                                                                                                                                          | 21             |

| 3.3. | 18kHz, $d=0,5$                                                                                                                                                                                                                                                                                                                           | 23             |

| 3.4. | Simulation des Tiefsetzstellers; Verlauf der Drain-Source-Spannung (UDS.V, blau), der Diodenspannung (UD1.V, grün), der invertierte Induktivitätsspannung (L1.V*-1, rot), der Ausgangsspannung (Ca.V, schwarz) und der Eingangsspannung (Ue.TR, pink); $U_e = 12V$ , $R_{Last} = 10\Omega$ , $L1 = 1mH$ , $f_{Takt} = 18kHz$ , $d = 0.5$ | 25             |

| 3.5. | Simulation des Tiefsetzstellers; Verlauf des Induktivitäts- (L1.I, rot) und Kondensatorstroms (Ca.I, schwarz); $U_e=12V$ , $R_{Last}=10\Omega$ , $L1=1mH$ , $f_{Takt}=18kHz$ , $d=0.5$                                                                                                                                                   | 26             |

| 3.6. | Simulation des Tiefsetzstellers; Verlauf des Induktivitätsstroms (L1.I, rot) und Laststroms (RLast.I, schwarz) an der Lückgrenze; $U_e = 12V$ , $R_{Last} = 72\Omega$ , $L1 = 1mH$ , $f_{Takt} = 18kHz$ , $d = 0.5$                                                                                                                      | 27             |

| 3.7. | Simulation des Tiefsetzstellers; Verlauf des Induktivitätsstroms (L1.I, rot) und Laststroms (RLast.I, schwarz) im Lückbetrieb; $U_e=12V,R_{Last}=500\Omega,L1=1mH,f_{Takt}=18kHz,d=0.5$                                                                                                                                                  | 28             |

| 3.8. | Simulation des Tiefsetzstellers; Verlauf des Induktivitäts-, des Dioden,- und des Transistorstrom; $U_e=12V$ , $R_{Last}=10\Omega$ , $L1=1mH$ , $f_{Takt}=18kHz$ , $d=0.5$                                                                                                                                                               | 29             |

| 3.9. | Simulation des Hochsetzstellers                                                                                                                                                                                                                                                                                                          | 30             |

| 3.10 | .Simulation des Hochsetzstellers; Induktivitäts- und Laststrom an der Lück-                                                                                                                                                                                                                                                              |                |

|      | grenze; $(U_e = 15V, R_{Last} = 288\Omega, L1 = 1mH, f_{Takt} = 18kHz, d = 0, 5)$ .                                                                                                                                                                                                                                                      | 31             |

| 3.11 | .Simulation des Hochsetzstellers; Stromverlauf an der Induktivität bei Leit- und                     |    |

|------|------------------------------------------------------------------------------------------------------|----|

|      | Sperrphase des MOSFETs; ( $U_e = 15V$ , $R_{Last} = 100\Omega$ , $L1 = 1mH$ , $f_{Takt} = 100\Omega$ |    |

|      | 18kHz, d = 0, 5)                                                                                     | 32 |

| 3.12 | .Simulation des Hochsetzstellers; Dioden- und Kondensatorstrom; ( $U_e =$                            |    |

|      | $15V, R_{Last} = 100\Omega, L1 = 1mH, f = 18kHz, d = 0, 5) \dots \dots \dots$                        | 33 |

| 3.13 | .Simulation des Hochsetzstellers; Spannungsverläufe; ( $U_e = 15V, R_{Last} = 15V$                   |    |

|      | $100\Omega, L1 = 1mH, f_{Takt} = 18kHz, d = 0, 5)$                                                   | 34 |

| 3.14 | .Simulationsschaltung invertierenden Tief- und Hochsetzsteller                                       | 35 |

| 3.15 | .Simulation des invertierenden Tief-/Hochsetzsteller; Stromverlauf am Aus-                           |    |

|      | gangskondensator; $(U_e = 12V, R = 100\Omega, L1 = 1mH, f = 18khz, d = 0, 6)$                        | 36 |

| 3.16 | .Simulation des invertierenden Tief-/Hochsetzstellers; Spannungsverläufe;                            |    |

|      | $(U_e = 12V, R_{Last} = 100\Omega, L1 = 1mH, f_{Takt} = 18kHz, d = 0, 6)$                            | 37 |

| 4.1. | Überspannungs- und Verpolungsschutz                                                                  | 38 |

| 4.2. | Pin-Belegung des Atmel ATtiny861A [1]                                                                | 40 |

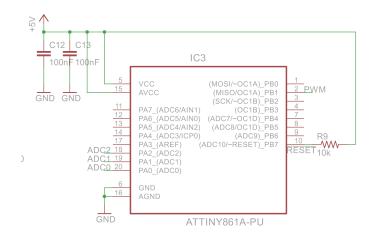

| 4.3. | Beschaltung des Mikrocontrollers                                                                     | 40 |

| 4.4. | 5V-Spannungsregler                                                                                   | 41 |

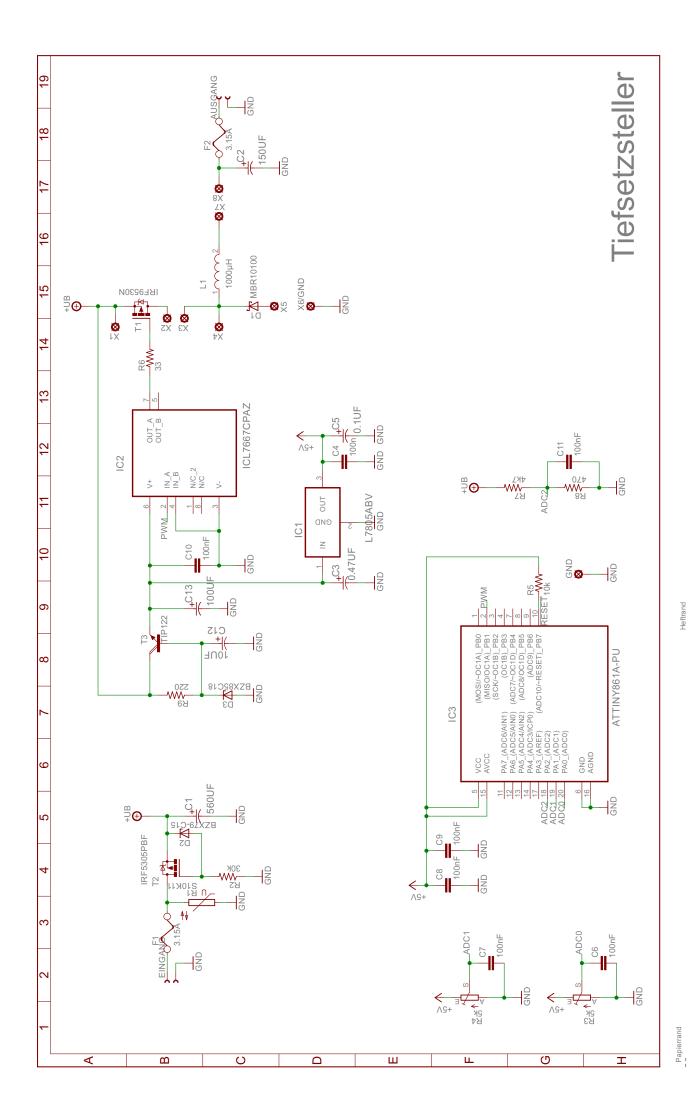

| 4.5. | Leistungsteil des Tiefsetzstellers                                                                   | 42 |

| 4.6. | Blockdiagramm des CMOS-Treiberbaustein ICL7667 des Herstellers intersil .                            | 43 |

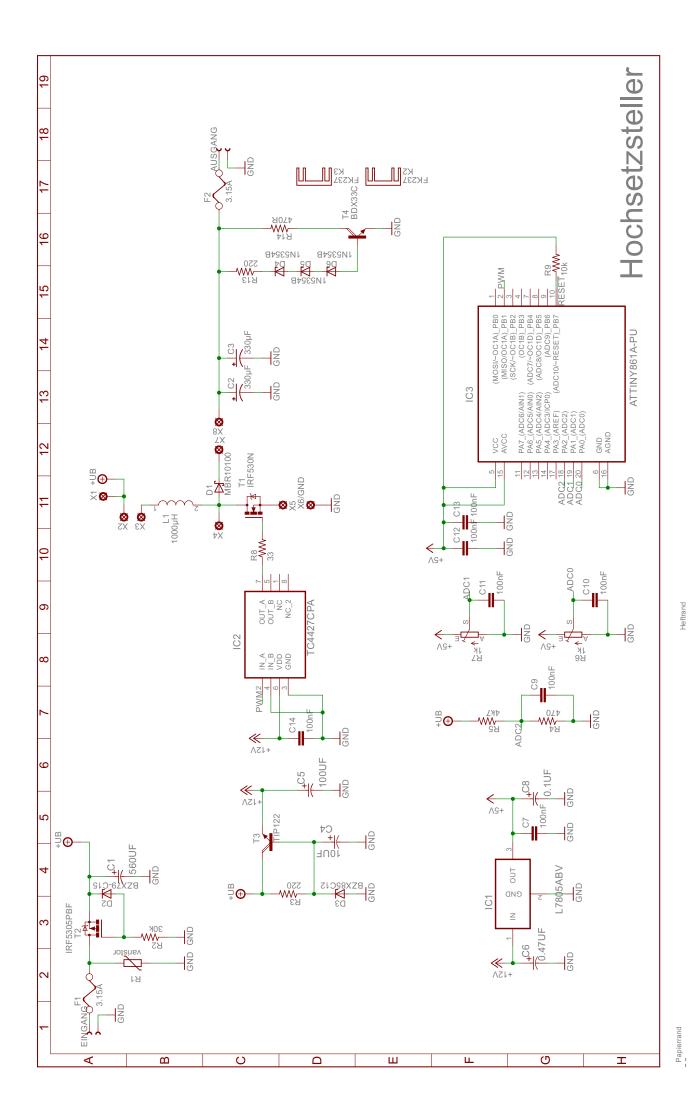

|      | Leistungsteil des Hochsetzstellers                                                                   | 46 |

| 4.8. | Blockdiagramm des nicht invertierenden CMOS-Treiberbausteins TC4427                                  |    |

|      | vom Hersteller Microchip                                                                             | 47 |

| 4.9. | Spannungsversorgung der IC-Bausteie                                                                  | 48 |

|      | Leistungsteil des invertierenden Tief-/Hochsetzstellers                                              | 49 |

| 4.11 | .Überspannungsschutzschaltung [13]                                                                   | 51 |

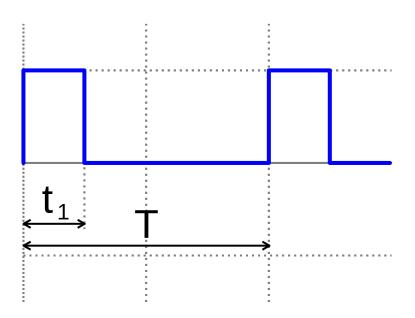

| 4.12 | .PWM-Verlauf, Tastgrad $d=rac{t_1}{T}$                                                              | 52 |

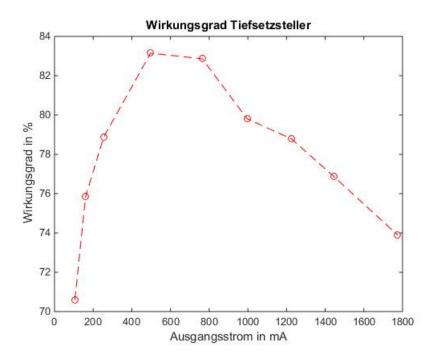

| 5.1. | Verlauf des Wirkungsgrades von dem realisierten Tiefsetzsteller bei einer Ein-                       |    |

|      | gangsspannung von $12V$ , einer Ausgangsspannung von $6V$ und einer Schalt-                          |    |

|      | frequenz von $18kHz$                                                                                 | 58 |

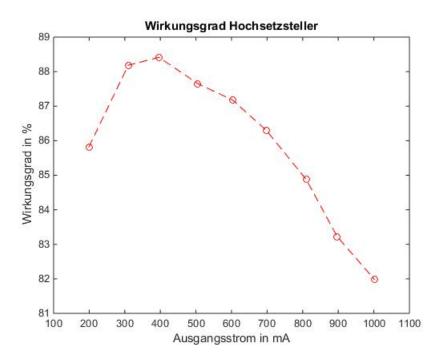

| 5.2. | Verlauf des Wirkungsgrades von dem realisierten Hochsetzsteller bei einer                            |    |

|      | Eingangsspannung von $15V$ , einer Ausgangsspannung von $30V$ und einer                              |    |

|      | Schaltfrequenz von $18kHz$                                                                           | 60 |

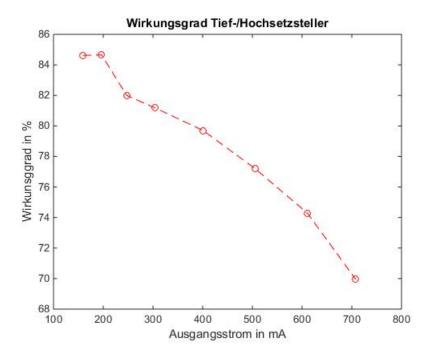

| 5.3. | Verlauf des Wirkungsgrades von dem realisierten Tief-/Hochsetzsteller bei ei-                        |    |

|      | ner Eingangsspannung von $12V$ , einer Ausgangsspannung von $-24V$ und                               | 64 |

|      | einer Schaltfrequenz von $18kHz$                                                                     | 61 |

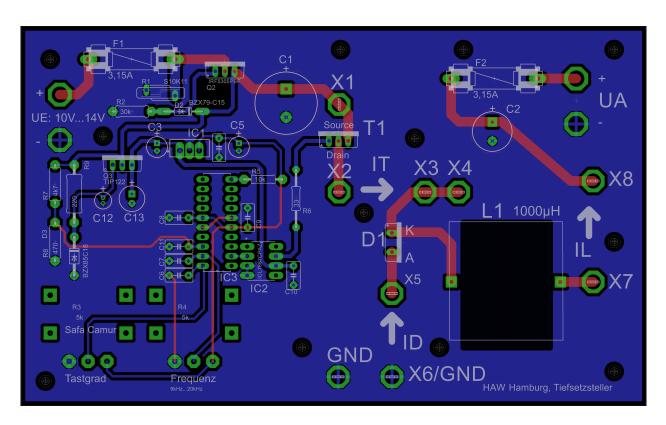

|      | Platine Tiefsetzsteller                                                                              | 63 |

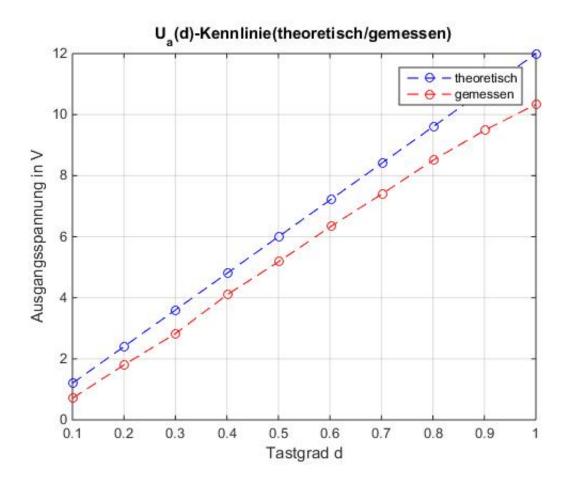

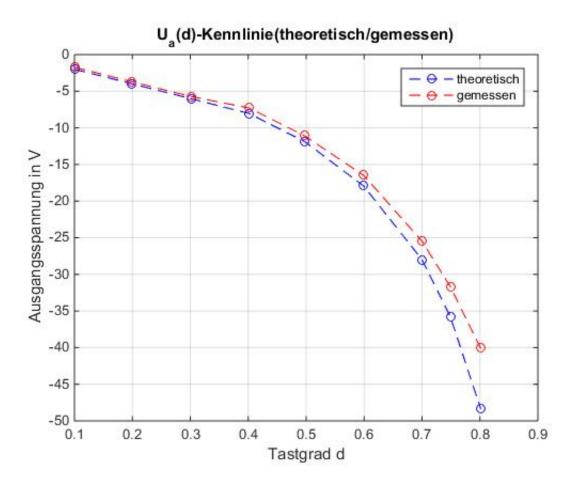

| 6.2. | Darstellung der $U_a(d)$ -Kennlinie(theoretisch/gemessen), ( $U_e = 12V$ , $f_{Takt} = 12V$          |    |

|      | $18kHz$ , $R_{l,ast} = 10\Omega$ )                                                                   | 64 |

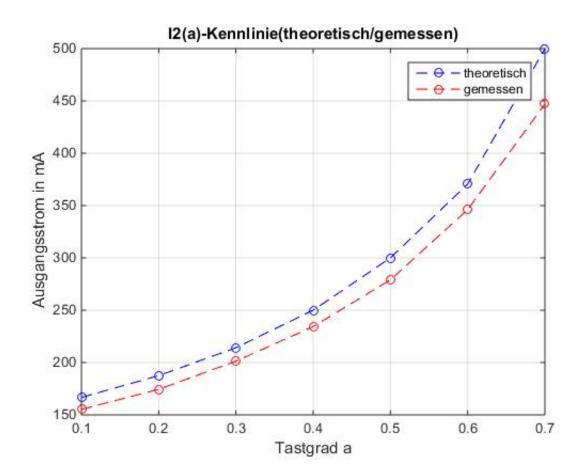

| 6.3. | Darstellung der $I_a(d)$ -Kennlinie(theoretisch/gemessen), ( $U_e = 12V$ , $f_{Takt} =$      |     |

|------|----------------------------------------------------------------------------------------------|-----|

|      | $18kHz$ , $R_{Last} = 10\Omega$ )                                                            | 65  |

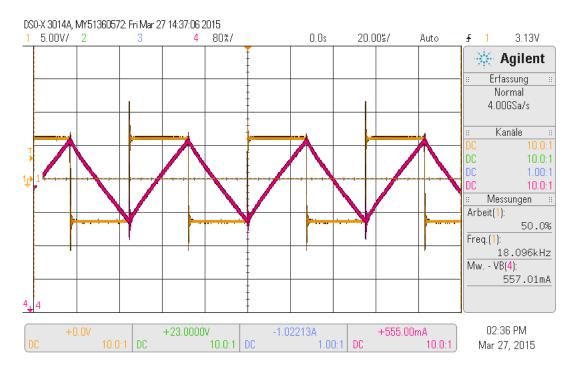

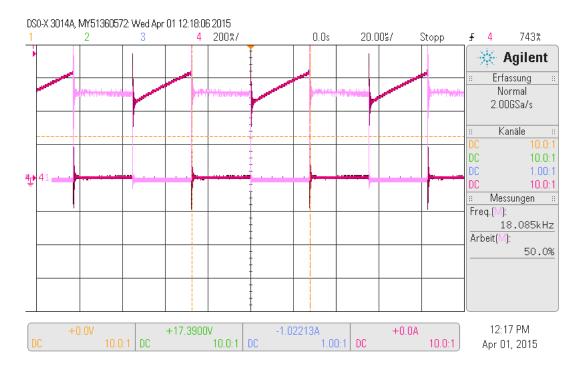

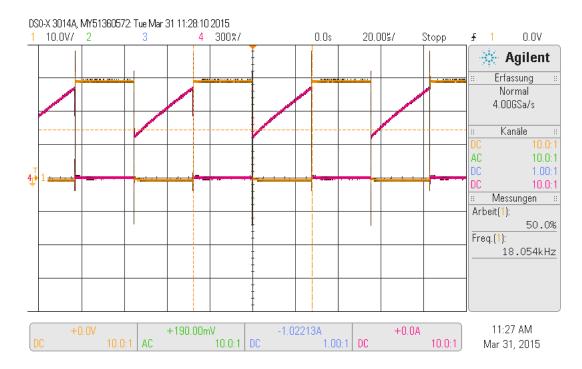

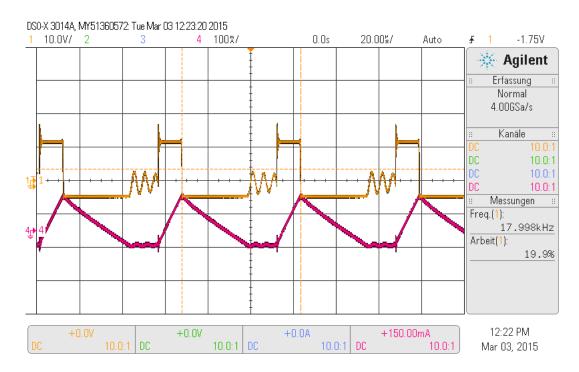

| 6.4. | Zeitlicher Verlauf von $U_L$ (gelb) und $I_L$ (rot) ( $I_{L,avg} = 557mA$ ) bei $d = 0, 5$ . | 66  |

|      | Zeitlicher Verlauf von $U_D$ (gelb) und $I_D$ (rot) bei $d=0,5$                              | 67  |

| 6.6. | Zeitlicher Verlauf von $U_T$ (violett) und $I_T$ (rot) bei $d=0,5$                           | 68  |

| 6.7. | Zeitlicher Verlauf von $I_L$ (rot) und $I_T$ (blau) bei $d=0,3\ldots\ldots\ldots$            | 69  |

| 6.8. | Zeitlicher Verlauf von $I_L$ (rot) und $I_D$ (blau) bei $d=0,3\ldots\ldots\ldots$            | 69  |

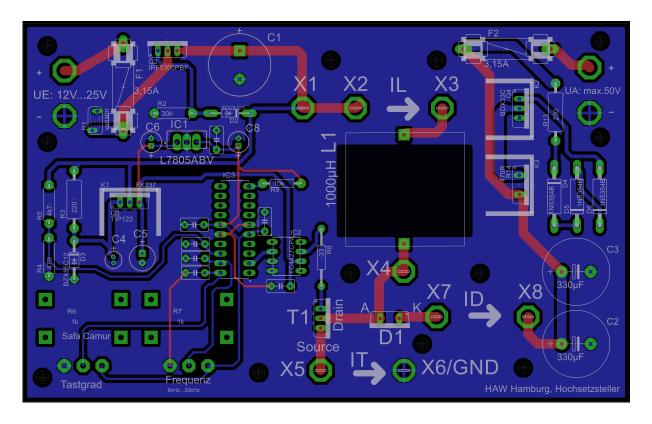

| 6.9. | Platine Hochsetzsteller                                                                      | 70  |

| 6.10 | . Darstellung der $U_a(d)$ -Kennlinie(theoretisch/gemessen), ( $U_e=15V$ , $f_{Takt}=$       |     |

|      | $18kHz$ , $R_{Last} = 100\Omega$ )                                                           | 72  |

| 6.11 | . Darstellung der $I_a(d)$ -Kennlinie(theoretisch/gemessen), ( $U_e=15V$ , $f_{Takt}=$       |     |

|      | $18kHz$ , $R_{Last} = 100\Omega$ )                                                           | 73  |

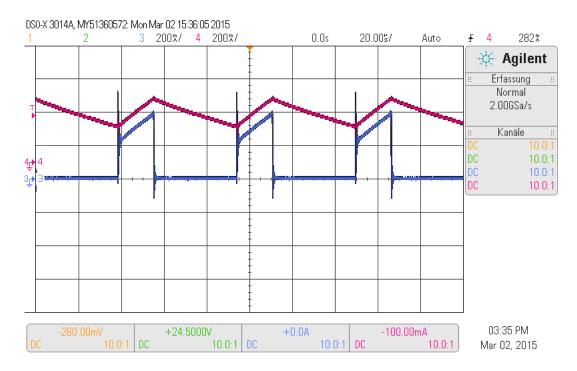

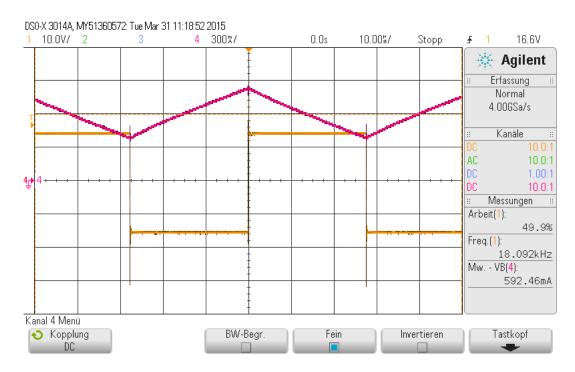

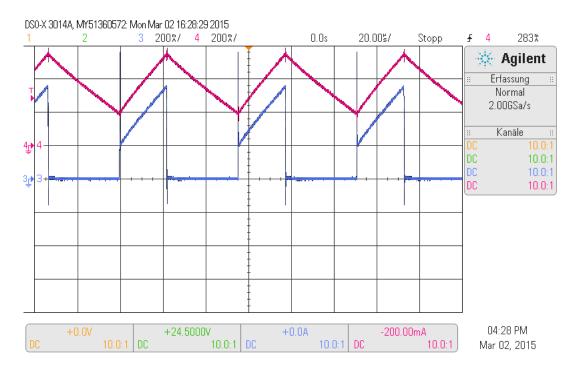

| 6.12 | .Zeitlicher Verlauf von $U_L$ (gelb) und $I_L$ (rot) ( $I_{L,avg} = 592,46mA$ ) bei $d=0,5$  | 74  |

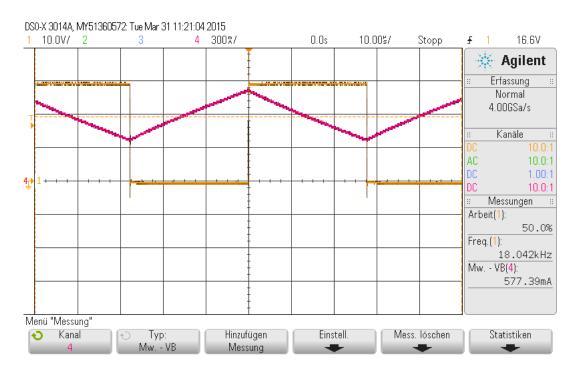

| 6.13 | .Zeitlicher Verlauf von $U_T$ (gelb) und $I_L$ (rot) ( $I_{L,avg} = 577,39 mA$ ) bei $d=0,5$ | 75  |

| 6.14 | .Zeitlicher Verlauf von $U_D$ (gelb) und $I_D$ (rot) bei $d=0,5$                             | 76  |

| 6.15 | .Zeitlicher Verlauf von $U_{\mathcal{T}}$ (gelb) und $I_{\mathcal{T}}$ (rot) bei $d=0$ , $5$ | 77  |

| 6.16 | .Zeitlicher Verlauf von $I_L$ (rot) und $I_T$ (blau) bei $d=0,4\ldots\ldots\ldots\ldots$     | 78  |

| 6.17 | .Zeitlicher Verlauf von $I_L$ (rot) und $I_D$ (blau) bei $d=0,4\ldots\ldots\ldots\ldots$     | 78  |

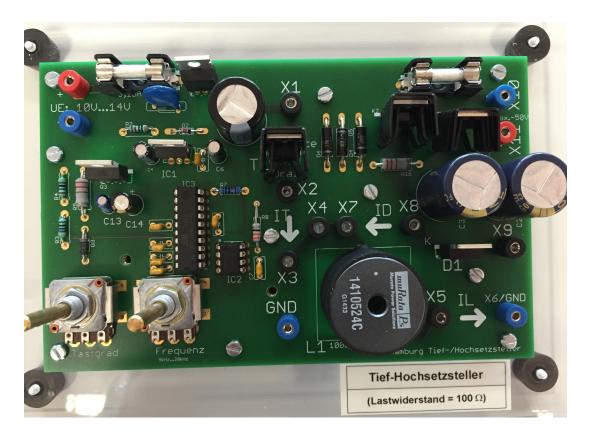

| 6.18 | .Platine Tief-/Hochsetzsteller                                                               | 79  |

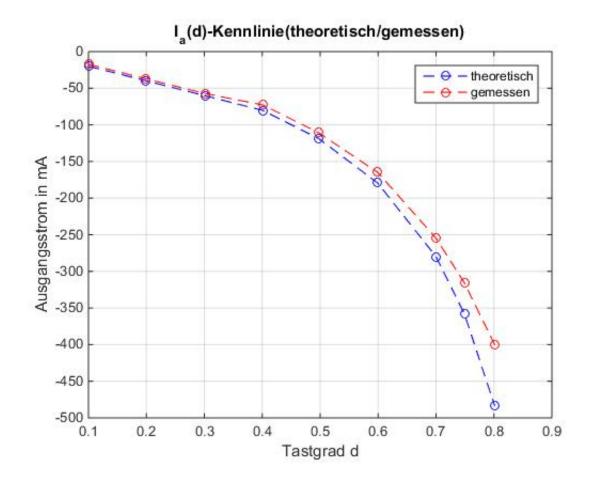

| 6.19 | . Darstellung der $U_a(d)$ -Kennlinie(theoretisch/gemessen), ( $U_e=12V$ , $f_{Takt}=$       |     |

|      | $18kHz$ , $R_{Last} = 10\Omega$ )                                                            | 81  |

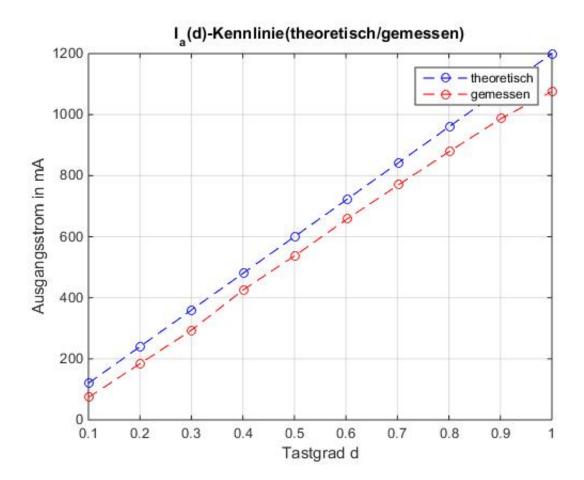

| 6.20 | . Darstellung der $I_a(d)$ -Kennlinie(theoretisch/gemessen), ( $U_e=12V$ , $f_{Takt}=$       |     |

|      | $18kHz$ , $R_{Last} = 10\Omega$ )                                                            | 82  |

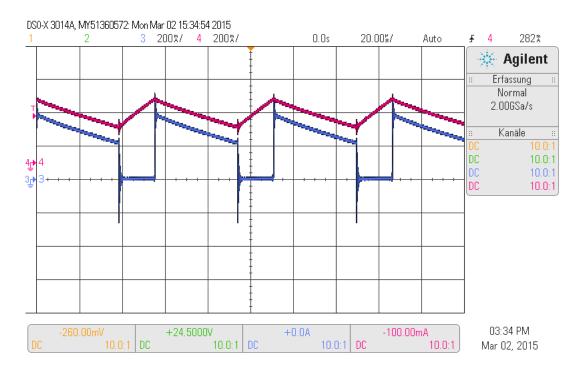

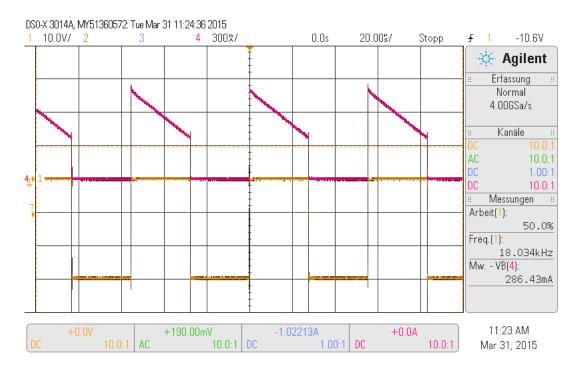

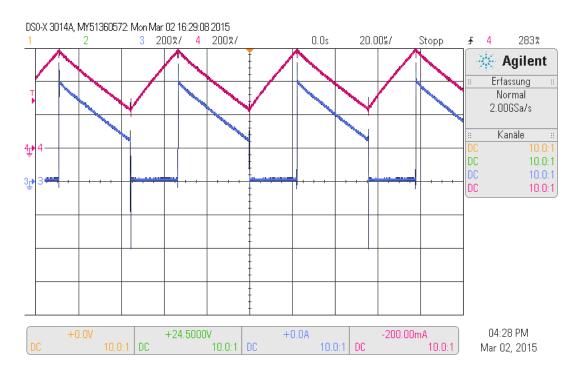

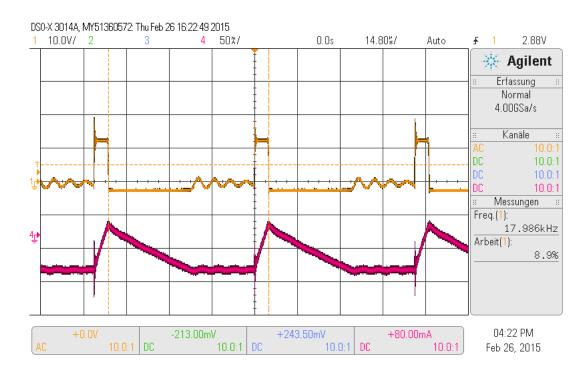

| 6.21 | .Zeitlicher Verlauf von $U_L$ (gelb) und $I_L$ (rot) bei $d=0$ , 2 (Lückbetrieb)             | 83  |

| 6.22 | .Zeitlicher Verlauf von $U_L$ (gelb) und $I_L$ (rot) bei $d=0$ , 089 (Lückbetrieb)           | 84  |

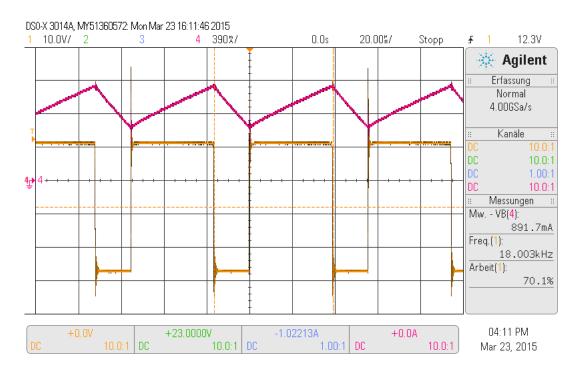

| 6.23 | .Zeitlicher Verlauf von $U_L$ (gelb) und $I_L$ (rot) ( $I_{L,avg} = 891,7mA$ ) bei $d=0,7$   | 85  |

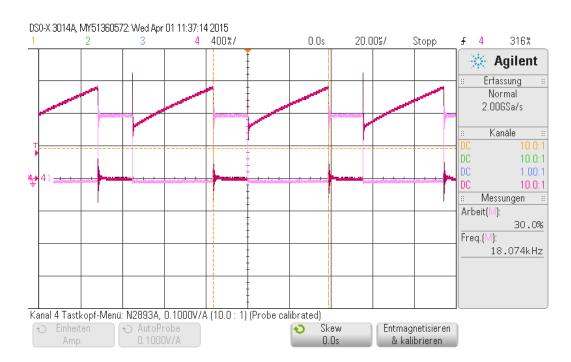

| 6.24 | .Zeitlicher Verlauf von $U_T$ (violett) und $I_T$ (rot) bei $d=0,2$ (Lückbetrieb)            | 86  |

| 6.25 | .Zeitlicher Verlauf von $U_T$ (violett) und $I_T$ (rot) bei $d=0,7$                          | 87  |

| 6.26 | .Zeitlicher Verlauf von $U_D$ (gelb) und $I_D$ (rot) bei $d=0,2$ (Lückbetrieb)               | 88  |

| 6.27 | .Zeitlicher Verlauf von $U_D$ (gelb) und $I_D$ (rot) bei $d=0,7$                             | 89  |

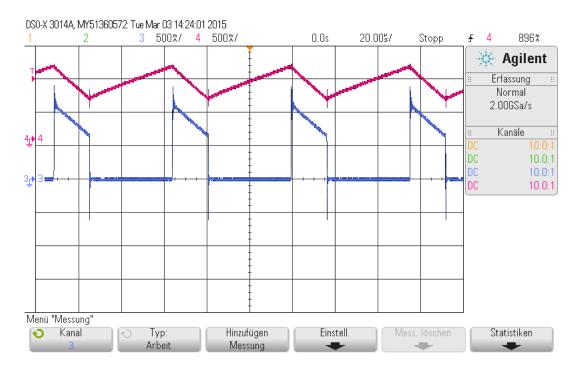

| 6.28 | .Zeitlicher Verlauf von $I_L$ (rot) und $I_D$ (blau) bei $d=0,7$                             | 90  |

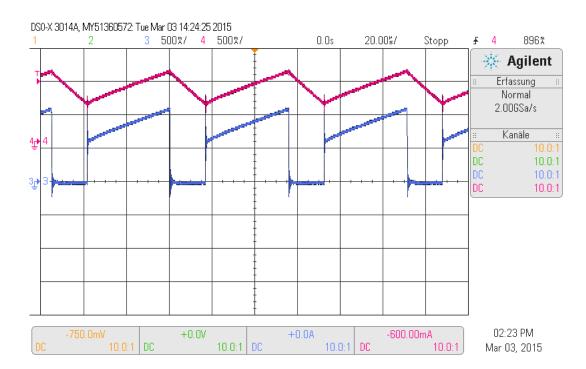

| 6.29 | .Zeitlicher Verlauf von $I_L$ (rot) und $I_T$ (blau) bei $d=0,7$                             | 91  |

|      | Layout des Tiefsetzstellers                                                                  | 101 |

| B.2. | Layout des Hochsetzstellers                                                                  | 103 |

| RЗ   | Layout des Tief-/Hochsetzstellers                                                            | 105 |

# 1. Einleitung

Die Gleichspannungssteller sind in der Elektrotechnik weit verbreitet. Sie kommen in alltäglichen Gebrauchsgegenständen wie Ladegeräten für Handys und Notebooks vor. Unter Verwendung eines Gleichspannungsstellers, auch DC/DC-Steller¹ genannt, wird der Betrag der Gleichspannung verändert. Es ist auch möglich, die Polarität der Gleichspannung zu verändern und den Eingang vom Ausgang galvanisch zu trennen.

Im Leistungsbereich bis etwa 100W [6] werden zweckmäßigerweise Tiefsetz-, Hochsetz- und Tief-/Hochsetzsteller eingesetzt, sofern es zulässig ist, dass keine Potentialtrennung zwischen Eingangs- und Ausgangsspannung möglich ist. Diese gehören zu der Gruppe von sekundärgetakteten DC/DC-Steller. Sie sind einfacher und kostengünstiger herzustellen. Ein sekundärgetakteter DC/DC-Steller besteht grundsätzlich aus einem Schalter, einer Induktivität, einem Kondensator und einer Diode. Zusätzlich ist noch eine Steuer- oder Regelschaltung erforderlich.

Für noch größere Leistungen oder wenn eine galvanische Trennung zwischen Ein- und Ausgang benötigt wird, werden primärgetaktete DC/DC-Steller eingesetzt. Die primärgetakteten DC/DC-Steller werden in dieser Arbeit nicht behandelt.

Um aus einer vorhandenen Gleichspannung eine kleinere Gleichspannung zu erzeugen, wird der Tiefsetzsteller eingesetzt. Der Hochsetzsteller hingegen wird verwendet, um aus einer Gleichspannung eine größere Gleichspannung zu erzeugen. Der invertierende Tief-/Hochsetzsteller erzeugt aus einer positiven Gleichspannung eine negative Gleichspannung. Der Betrag der Ausgangsspannung des invertierenden Tief-/Hochsetzstellers kann kleiner, größer oder gleich (beim idealen Fall) der Eingangsspannung sein.

Diese vorliegende Bachelorarbeit befasst sich mit dem Entwurf und Aufbau eines Tiefsetzstellers, eines Hochsetzstellers und eines invertierenden Tief-/Hochsetzstellers für den Praktikumsversuch im Labor für Energietechnik. Für die Ansteuerung des Schalters der jeweiligen DC/DC-Steller mit einem PWM-Signal, welches ein variablen Tastgrad und variabler Schaltfrequenz hat, wird ein Mikrocontroller verwendet.

Zunächst werden in den Kapiteln 2.1.1 bis 2.1.3 die theoretischen Grundlagen für das Verständnis der Arbeitsweise eines Tiefsetz-, eines Hochsetz-, und eines invertierenden Tief-/Hochsetzstellers zusammengefasst. Für die Simulationen wird das Simulationsprogramm

<sup>&</sup>lt;sup>1</sup>DC:Direct Current

1. Einleitung

PORTUNUS verwendet. Dazu werden zuerst die Bauteile der Schaltungen dimensioniert und anschließend die Strom und Spannungsverläufe simuliert. Die Simulationen dienen als Orientierungshilfe und zum besseren Verständnis beim Entwerfen, Dimensionieren und Optimieren der Schaltungen.

Anschließend wurden die Bauteile für die Schaltungen ausgewählt, die Schaltpläne und die Layouts der Platinen mit dem Programm EAGLE erstellt. Nach der Bestückung und Inbetriebnahme der DC/DC-Steller werden die Verlustleistungen untersucht und ein praktischer Versuch durchgeführt.

# 2.1. Sekundärgetaktete DC/DC-Steller

In diesem Abschnitt werden die Grundlagen des später umgesetzten Tiefsetz-, Hochsetzund Tief-/Hochsetzstellers behandelt.

#### 2.1.1. Der Tiefsetzsteller

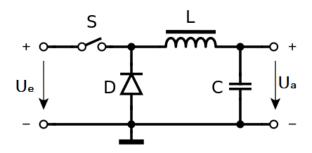

Der Tiefsetzsteller ( Abb. 2.1), auch Abwärtswandler genannt, wandelt eine höhere Gleichspannung in eine niedrige Gleichspannung um. Dies geschieht durch das Zu- und Abschalten der zu wandelnde Eingangsspannungsquelle. Bei geschlossenem Schalter S fließt ein Strom durch den Schalter, lädt die Induktivität L, den Kondensator C und führt Energie an den Verbraucher. Der Verbraucher wird dem Kondensator parallel zugeschaltet. Die Induktivität baut aufgrund des Stromflusses ein Magnetfeld auf und wirkt als magnetischer Energiespeicher. Beim Öffnen des Schalters entmagnetisiert sich die Induktivität über den Kondensator, den Verbraucher und über die Diode D und erzeugt eine Spannung mit umgekehrter Polarität. Die Induktivität fungiert nun als Spannungsquelle. Über die Veränderung der Ein- und Ausschaltzeit der Eingangsspannungsquelle wird die Höhe der Spannung am Kondensator eingestellt. [13][17]

Abbildung 2.1.: Prinzipschaltung eines Tiefsetzstellers

Bei der folgenden Funktionsbeschreibung der Schaltung in Abbildung 2.1 wird vereinfachend angenommen, dass der Schalter und die Diode keinen Spannungsabfall während der jeweiligen Einschaltphasen haben. Der ohmsche Widerstand der Induktivität und der Innenwiderstand des Kondensators werden ebenfalls vernachlässigt. Bei geschlossenem Schalter steigt der Strom durch die Induktivität nach dem Induktionsgesetz mit der Steilheit

$$\frac{\Delta I_{L,ein}}{t_{ein}} = \frac{U_e - U_a}{L} \tag{2.1}$$

an. Über die Induktivität liegt die Differenz zwischen Ein- und Ausgangsspannung an. Bei geöffnetem Schalter kehrt die Polarität der Spannung an der Induktivität um und der Strom durch die Induktivität nimmt mit der Steilheit

$$\frac{\Delta I_{L,aus}}{t_{aus}} = \frac{-U_a}{L} \tag{2.2}$$

ab. Im eingeschwungenen Zustand ist die Energieaufnahme während der Einschaltzeit  $t_{ein}$  und die Energieabgabe während der Ausschaltzeit  $t_{aus}$  gleich groß. Durch Gleichsetzen

$$\Delta I_L = \frac{(U_e - U_a)}{L} \cdot t_{ein} = \frac{U_a}{L} \cdot t_{aus}$$

(2.3)

ergibt sich für die Ausgangsspannung  $U_a$ :

$$U_a = \frac{t_{ein}}{t_{ein} + t_{aus}} \cdot U_e = \frac{t_{ein}}{T_{Takt}} \cdot U_e = d \cdot U_e$$

(2.4)

Durch geeignete Wahl des Tastgrades  $d=\frac{t_{ein}}{t_{ein}+t_{aus}}=\frac{t_{ein}}{\mathcal{T}_{Takt}}$  lässt sich die Höhe der Ausgangsspannung einstellen. Für den Ein- und Ausgangsstrom gilt über eine Leistungsbilanz zwischen Ein- und Ausgang:

$$P_e = U_e \cdot I_e = U_a \cdot I_a = P_a \tag{2.5}$$

Daraus resultiert unmittelbar die Beziehung:

$$\frac{U_e}{U_a} = \frac{I_a}{I_e} = \frac{1}{d} \tag{2.6}$$

Die Stromänderung in der Induktivität  $\Delta I_{\perp}$  ist für die Ein- und Ausschaltdauer betragsmäßig gleich groß. Daher wird für die Dimensionierung der Induktivität nur der Einschaltvorgang betrachtet:

$$L = \frac{U_e - U_a}{\Delta I_I} \cdot t_{ein} \tag{2.7}$$

Mit Gleichung 2.4 folgt:

$$L = \frac{(U_e - U_a) \cdot d \cdot T_{Takt}}{\Delta I_L} = \frac{(U_e - d \cdot U_e) \cdot d}{\Delta I_L \cdot f_{Takt}}$$

(2.8)

Damit erhält man eine Dimensionierungsgleichung für die Induktivität. Der durch die Last am Ausgang eingeprägte Strom  $I_a$  ist identisch mit dem zeitlichen Mittelwert des Stroms in der Induktivität  $\overline{I}_L$ . Bei einem Ausgangsstrom von

$$I_{a,min} < \frac{\Delta I_L}{2} \tag{2.9}$$

, wird der Strom in der Induktivität  $I_L$  zu jeder Periode zu Null. Man nennt dies den lückenden Betrieb. Dann stimmen die Gleichungen 2.1 bis 2.9 nicht mehr. Die maximale Schwankungsbreite des Stroms in der Induktivität  $\Delta I_{L,max}$  ergibt sich für den Tastgrad d=0,5. Nach Umformen der Gleichung 2.8 und mit Gleichung 2.9 gilt für den minimalen Ausgangsstrom  $I_{a,min}$  im ungünstigsten Fall:

$$I_{a,min}|_{d=\frac{1}{2}} \ge \frac{\Delta I_{L,max}}{2}|_{d=\frac{1}{2}} = \frac{(U_{e,max} - d \cdot U_{e,max}) \cdot d}{2 \cdot L \cdot f_{Takt}}|_{d=\frac{1}{2}} = \frac{U_{e,max} \cdot T_{Takt}}{8 \cdot L}$$

(2.10)

Somit kann die Induktivität auch mit der Gleichung 2.10 für ein gewünschter Mindestausgangsstrom dimensioniert werden. Der minimale Ausgangsstrom nimmt mit steigender Schaltfrequenz  $f_{Takt}$  ab. Die obere Grenze der Schaltfrequenz ergibt sich aus den Schaltverlusten des Schalters und Verlusten im Kernmaterial der Induktivität.

Durch den Kondensator C werden die Spannungsschwankungen geglättet. Wird der Schalter S geschlossen, entspricht die Ausgangsspannung etwa der Eingangsspannung, nachdem der Kondensator C komplett geladen ist. Die Mindestkapazität des Ausgangskondensators wird mit der Gleichung 2.11 dimensioniert.[?]

$$C \ge \frac{U_{e,max} \cdot T_{Takt}^2}{32 \cdot L \cdot \Delta u_a} \tag{2.11}$$

Erhöht man die Kapazität oder die Frequenz, so reduziert sich die Welligkeit noch weiter. Da die Frequenz quadratisch eingeht, würde eine Verdopplung der Frequenz die Restwelligkeit auf ein Viertel reduzieren. Der Nachteil einer Frequenzerhöhung sind die steigenden Schaltverluste, die in Kapitel 5 beschrieben werden.

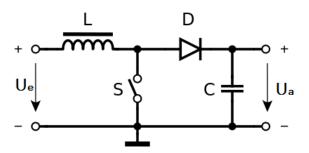

## 2.1.2. Der Hochsetzsteller

Der Hochsetzsteller (Abb. 2.2), auch Aufwärtswandler genannt, wandelt eine niedrige Gleichspannung in eine höhere Gleichspannung um. Bei geschlossenem Schalter S fließt der Eingangsstrom durch die Induktivität L. Es wird magnetische Energie gespeichert. Wenn der Schalter geöffnet wird, bleibt der Stromfluss in der Induktivität zunächst erhalten und die Polarität der Spannung an der Induktivität kehrt um. Die in der Induktivität gespeicherte Energie wird nun über die Diode D in den Kondensator C umgeladen. Die Eingangsspannung und die Spannung an der Induktivität addieren sich auf. Die sich im Kondensator einstellende Spannung ist dann die Eingangspannung plus die Spannung an der Induktivität. Schließt man ein Verbraucher an den Ausgang, dann wird der Kondensator wieder entladen und die Spannung an diesem Bauteil sinkt. Der Schaltvorgang wird so ständig wiederholt. Die Diode verhindert beim lückenden Betrieb das Entladen des Kondensators bei geöffnetem Schalter über die Eingangsspannungsquelle.[13][17]

Abbildung 2.2.: Prinzipschaltung eines Hochsetzstellers

Bei der folgenden Funktionsbeschreibung der Schaltung wird nicht lückender Betrieb angenommen,  $I_e \geq I_{e,min}$  und die Bauelemente als verlustfrei betrachtet. Während der Einschaltzeit  $t_{ein}$  des Schalters liegt über die Induktivität die Eingangsspannung  $U_e$  und der Strom durch die Induktivität steigt mit der Steilheit  $\frac{\Delta I_{L,ein}}{t_{ein}} = \frac{U_e}{L}$  an. Während der Ausschaltzeit  $t_{aus}$  des Schalters übernimmt die Diode den durch die Induktivität einprägten Strom. In dieser Zeit liegt über die Induktivität die Differenz zwischen Ein- und Ausgangsspannung und der Strom durch die Induktivität nimmt mit der Steilheit  $\frac{\Delta I_{L,aus}}{t_{aus}} = \frac{-(U_a - U_e)}{L}$  ab. Im eingeschwungenen Zustand gilt für die Stromänderung in der Induktivität:

$$\Delta I_L = \frac{U_e}{I} \cdot t_{ein} = \frac{U_a - U_e}{I} \cdot t_{aus}$$

(2.12)

Mit der Periodendauer  $T_{Takt} = t_{ein} + t_{aus}$ , der Taktfrequenz  $f_{Takt}$  und des Tastgrades  $d = \frac{t_{ein}}{T_{Takt}}$  lässt sich die von dem Tastgrad d abhängige Ausgangsspannung  $U_a$  berechnen:

$$U_a = \frac{1}{1 - d} \cdot U_e \tag{2.13}$$

Der Zusammenhang zwischen Ein- und Ausgangsstrom kann unter Vernachlässigung der Verluste über eine Leistungsbilanz zwischen Ein- und Ausgang bestimmt werden.

$$\frac{I_a}{I_e} = \frac{U_e}{U_a} = 1 - d \tag{2.14}$$

Der Mittelwert des Stroms in der Induktivität  $\overline{I_L}$  ist gleich dem Eingangsstrom  $I_e$  und ist immer größer oder gleich (bei einem Tastgrad d=0) des Ausgangsstromes  $I_a$ . Mit den Gleichungen 2.12 und 2.13 folgt für die Dimensionierung der Induktivität:

$$L = \frac{U_e \cdot d}{\Delta I_L \cdot f_{Takt}} = \frac{(1 - d) \cdot d \cdot U_a}{\Delta I_L \cdot f_{Takt}}$$

(2.15)

Bei

$$I_{e,min} < \frac{\Delta I_L}{2} \tag{2.16}$$

, wird der Strom in der Induktivität  $I_L$  zu jeder Periode zu Null und lückt. Dann sind die Gleichungen 2.12 bis 2.15 nicht mehr gültig. Da die Induktivität nur während der Ausschaltzeit Energie in den Ausgangskondensator pumpt und während der Einschaltzeit keinen Strom zum Ausgang liefern kann, kann man für den Ausgangsstrom schreiben:

$$I_a = \frac{t_{aus}}{T_{Takt}} \cdot I_e = (1 - d) \cdot I_e$$

(2.17)

Je größer die Differenz zwischen Ein- und Ausgangsspannung wird (je größer der Tastgrad), desto größer wird der Eingangsstrom. Für den Mindestausgangsstrom  $I_{a,min}$  der bei einem bestimmten Tastgrad nicht unterschritten werden darf, damit der Strom in der Induktivität nicht lückt, gilt:

$$I_{a,min} = \frac{t_{aus}}{T_{Takt}} \cdot I_e = \frac{\Delta I_L}{2} \cdot \frac{t_{aus}}{T_{Takt}} = \frac{\Delta I_L}{2} \cdot (1 - d) = \frac{(1 - d) \cdot U_e \cdot t_{ein}}{2 \cdot L} = \frac{(1 - d) \cdot U_e \cdot d}{2 \cdot L \cdot f_{Takt}}$$

(2.18)

Aus  $\frac{dI_{a,min}}{dd} = 0$  folgt, dass der Mindestausgangsstrom  $I_{a,min}$  für d = 0, 5 maximal wird. Somit gilt für den Mindestausgangsstrom im ungünstigsten Fall bei d = 0, 5 an der Lückgrenze:

$$I_{a,min} \ge \frac{U_{e,max} \cdot T_{Takt}}{8 \cdot I} \tag{2.19}$$

Die Induktivität kann somit auch für einen gewünschten Mindestausgangsstrom dimensioniert werden. Der Mindestkapazitätswert des Ausgangskondensators wird mit der Gleichung 2.20 dimensioniert [16].

$$C \ge \frac{T_{Takt} \cdot I_{a,max}}{\Delta U_a} \tag{2.20}$$

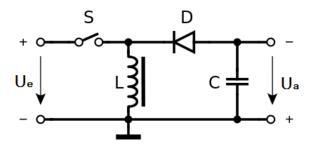

## 2.1.3. Der Tief-/Hochsetzsteller

Der invertierende Tief-/Hochsetzsteller (Abb. 2.3), auch Inverswandler genannt, wandelt eine positive Gleichspannung in eine negative Gleichspannung um. Der Betrag der Ausgangsspannung kann größer, kleiner oder gleich der Eingangsspannung sein. Bei geschlossenem Schalter S ist die Diode D in Sperrrichtung geschaltet. Es fließt ein Strom durch den Schalter und die Induktivität L. Die Induktivität nimmt zu diesem Zeitpunkt Energie auf und speichert sie. Nach dem öffnen des Schalters wirkt die Induktivität als Spannungsquelle mit umgekehrter Polarität. Am oberen Spulenanschluss ist nun die Spannung negativ gegenüber dem unteren Spulenanschluss. Die Diode ist nun. Der Induktivitätsstrom lädt den Kondensator C und speist den Verbraucher.[13][17]

Abbildung 2.3.: Prinzipschaltung eines Tief-/Hochsetzstellers

Bei der folgenden Funktionsbeschreibung der Schaltung wird nicht lückender Betrieb angenommen und die Bauelemente als verlustfrei betrachtet. Während der Einschaltzeit des Schalters liegt über die Induktivität die Eingangsspannung  $U_L$  und der Strom durch die Induktivität steigt mit der Steilheit  $\frac{\Delta I_{L,ein}}{t_{ein}} = \frac{U_e}{L}$  an. Während der Ausschaltzeit  $t_{aus}$  des Schalters übernimmt die Diode den Strom der Induktivität. In dieser Zeit liegt über die Induktivität die Spannung  $U_L = -U_a$  und der Strom durch die Induktivität nimmt mit der Steilheit  $\frac{\Delta I_{L,aus}}{t_{aus}} = \frac{U_a}{L}$  ab. Im eingeschwungenen Zustand ist die Energieaufnahme während der Einschaltzeit  $t_{ein}$  und die Energieabgabe während der Ausschaltzeit  $t_{aus}$  gleich groß. Für die Stromänderung in der Induktivität gilt:

$$\Delta I_L = \frac{U_e \cdot t_{ein}}{L} = \frac{U_a \cdot t_{aus}}{L}$$

(2.21)

Hieraus kann die Ausgangsspannung in Abhängigkeit vom Tastgrad d berechnet werden:

$$|U_a| = \frac{t_{ein}}{t_{aug}} \cdot U_e = \frac{d}{1 - d} \cdot U_e \tag{2.22}$$

Für den Zusammenhang zwischen den Ein- und Ausgangsstrom gilt unter Vernachlässigung der Verluste über eine Leistungsbilanz zwischen Ein- und Ausgang:

$$I_e = \frac{U_a}{U_e} \cdot I_a \tag{2.23}$$

Für  $t_{ein} < t_{aus}$  bzw. d < 0,5 ist der Betrag der Ausgangsspannung kleiner als der Betrag der Eingangsspannung. Dagegen ist für  $t_{ein} > t_{aus}$  bzw. d > 0,5 der Betrag der Ausgangsspannung größer als der Betrag der Eingangsspannung. Für  $t_{ein} = t_{aus}$  bzw. d = 0,5 sind die Beträge unter Vernachlässigung der Verluste gleich. Mit den Gleichungen 2.21 und 2.22 gilt für die Dimensionierung der Induktivität:

$$L = \frac{U_e \cdot t_{ein}}{\Delta I_L} = \frac{|U_a| \cdot (1 - d) \cdot t_{ein}}{d \cdot \Delta I_L} = \frac{|U_a| \cdot (1 - d)}{\Delta I_L \cdot f_{Takt}} = \frac{d \cdot U_e}{\Delta I_L \cdot f_{Takt}}$$

(2.24)

Die Energie wird wie beim Hochsetzsteller nur während der Ausschaltzeit  $t_{aus}$  des Schalters zum Ausgang übertragen. Daher kann man für den Zusammenhang zwischen den Induktivitätsstrom und dem Ausgangsstrom feststellen:

$$I_a = \frac{t_{aus}}{T_{Takt}} \cdot \bar{I}_L = (1 - d) \cdot \bar{I}_L \tag{2.25}$$

Im lückenden Betrieb wird der Strom in der Induktivität zu jeder Periode zu Null. Dies ist bei einem Induktivitätsstrom von

$$\bar{I}_L < \frac{\Delta I_L}{2} \tag{2.26}$$

der Fall. In diesem Fall stimmen die oben angegebenen Gleichungen nicht mehr. Für den Mindestausgangsstrom  $I_{a,min}$  bei einem bestimmten Tastgrad gilt:

$$I_{a,min} = \frac{\Delta I_L}{2} \cdot \frac{t_{aus}}{T_{Takt}} = \frac{\Delta I_L}{2} \cdot (1 - d) = \frac{(1 - d) \cdot d \cdot U_e}{2 \cdot L \cdot f_{Takt}}$$

(2.27)

Aus  $\frac{dI_{a,min}}{dd}=0$  folgt, dass der Mindestausgangsstrom  $I_{a,min}$  für d=0,5 maximal wird. Somit gilt mit der Gleichung 2.27 für den Mindestausgangsstrom im ungünstigsten Fall bei d=0,5 an der Lückgrenze:

$$I_{a,min}|_{d=\frac{1}{2}} \ge \frac{U_{e,max} \cdot T_{Takt}}{8 \cdot I} \tag{2.28}$$

Der Mindestkapazitätswert des Ausgangskondensators wird auch mit der Gleichung 2.20 dimensioniert [16].

## 3.1. PORTUNUS

Für die Simulationen wurde das Programm PORTUNUS benutzt. PORTUNUS ist ein Simulationstool der Firma Adapted Solutions GmbH. Es wird zur Simulation und Analyse von Schaltungen und Systemen der Elektro- und Elektroenergietechnik, Leistungselektronik und der elektrischen Antriebstechnik verwendet. Das Simulationstool PORTUNUS wird national und international in Industrieunternehmen und in Hochschulen eingesetzt. Im Rahmen dieser Arbeit wird die Version PORTUNUS PRO V5.2 verwendet.

Den Grundschaltungen der DC/DC-Steller in den Simulationen entsprechen von den simulierten Bauteilen etwa die umgesetzten Schaltungen. Die Treiberschaltungen in den Simulationen wurden bei den später umgesetzten DC/DC-Stellern durch fertige Treiberbausteine ersetzt. Die Simulationen dienten als Orientierungshilfe und zum Verständnisaufbau beim Entwerfen, Dimensionieren und Optimieren der Schaltungen.

Die MOSFETs und Dioden in den Simulationen wurden als neue SPICE-Modelle eingebunden, weil diese in PORTUNUS nicht vorhanden waren. Die SPICE-Parameter wurden aus den Herstellerseiten der Bauelemente übernommen.

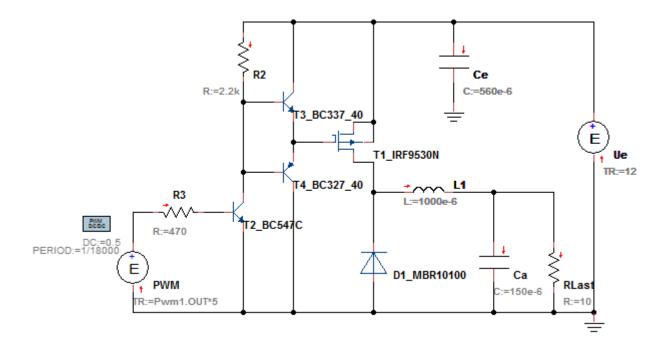

## 3.2. Simulation des Tiefsetzstellers

Der entworfene Tiefsetzsteller, der in Kapitel 4.1.4 beschrieben wird, hat einen Eingangsspannungsbereich von 10V bis 14V und einen Schaltfrequenzbereich von 9kHz bis 20kHz.

In Abbildung 3.1 wird die Simulationsschaltung des Tiefsetzstellers dargestellt. Die Induktivität dient als Energiespeicher und sollte so groß gewählt werden, dass der Strom durch die Induktivität nicht lückt. Der maximale Stromrippel  $\Delta I_{L,max}$  in der Induktivität tritt bei einem Tastgrad von d=0, 5 auf. Desweiteren ist die geringste Taktfrequenz  $f_{Takt,min}$  und die maximale Eingangsspannung  $U_{e,max}$  des Tiefsetzstellers von Bedeutung. Für die Bestimmung einer geeigneten Induktivität wird im ungünstigsten Fall  $\Delta I_{L,max}=400\,mA$  festgelegt. Bei

$\Delta I_{L,max} = 400 mA$  beträgt der Mindestausgangsstrom  $I_{a,min} = 200 mA$ . Daraus ergibt sich mit Gleichung 2.10 für die Induktivität:

$$L = \frac{U_{e,max} \cdot T_{Takt,min}}{8 \cdot I_{a,min}} = \frac{14V \cdot 9kHz^{-1}}{8 \cdot 200mA} = 972\mu H \approx 1mH$$

Die Induktivität muss also mindestens 1mH betragen.

Abbildung 3.1.: Simulation des Tiefsetzstellers

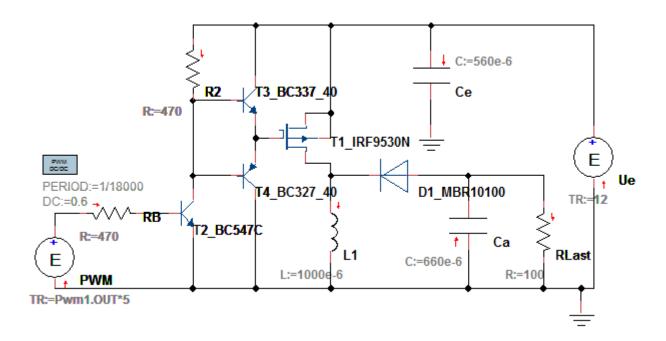

Der Schalter in der Grundschaltung wurde mit einem P-Kanal MOSFET IRF9530N realisiert. Die verwendete Diode ist eine Schottky-Diode MBR10100. Die Sperrzone der Schottky-Dioden basiert auf einen Metall-Halbleiter-Übergang und ist aus diesem Grund besonders dünn, so dass die Zeit für das Ausräumen der Ladungsträger minimal ist. Dadurch können sie mit höherer Geschwindigkeit arbeiten und haben sehr geringe Schaltverluste. Induktivität und die Kondensatoren sind in den Simulationen ideal und verursachen daher keine Verluste.

Das PWM-Modell mit der Spannungsquelle PWM (Abb. 3.1) generiert ein PWM-Signal. Für die Ansteuerung des P-Kanal MOSFETs wurde in der Simulation eine Gegentakt-Treiberschaltung verwendet. Wenn der Transistor T2 durchschaltet, sperrt T3 und T4 schaltet durch. Dadurch schaltet auch das MOSFET ein. Wird der Transistor T2 abgeschaltet, werden die Basen von T3 und T4 auf die positive Versorgungsspannung angehoben, so dass

T3 durchschaltet und T4 sperren kann. Das Gate von MOSFET bekommt über den niederohmigen Ausgang von T3 positive Spannung und schaltet ab.

Um die Ausgangsspannung zu glätten, wurde der Ausgangskondensator mit der Gleichung 2.11 dimensioniert. Für eine Ausgangswelligkeit in der Größenordnung von 10mV und eine maximale Eingangsspannung von 14V, ergibt sich ein Glättungskondensator von  $135\mu F$ .

$$C \ge \frac{U_{e,max} \cdot T_{Takt}^2}{32 \cdot L \cdot \Delta U_a} = \frac{14V \cdot (18kHz^{-1})^2}{32 \cdot 1000\mu H \cdot 10mV}$$

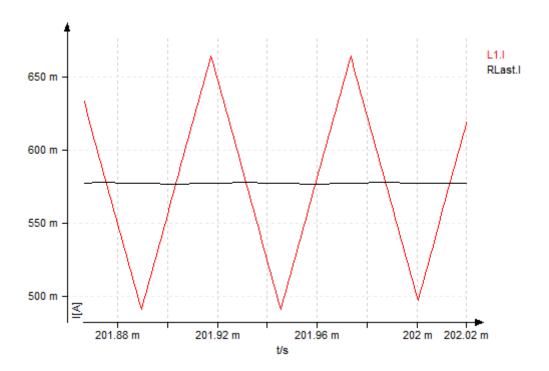

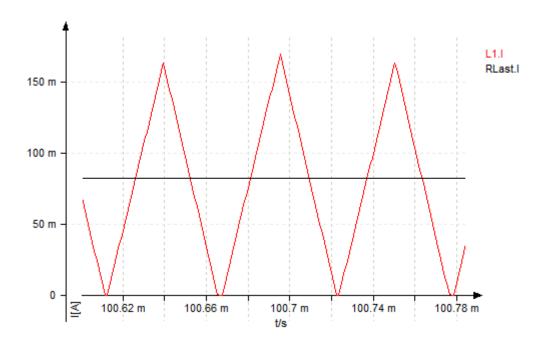

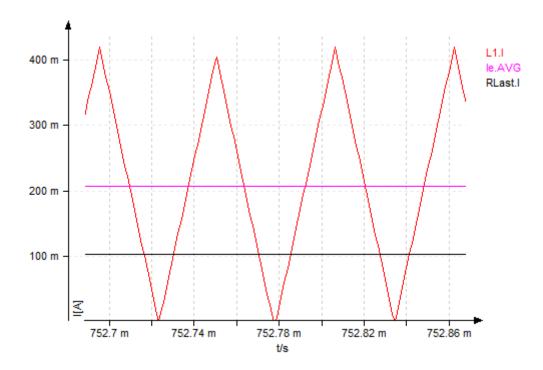

In Abbildung 3.2 wurde der Verlauf des Induktivitäts- und Laststroms im nicht lückenden Betrieb dargestellt. Die Eingangsspannung  $U_e$  wurde auf 12V, die Taktfrequenz  $f_{Takt}$  auf 18kHz, die Induktivität L1 auf 1mH und der Ausgangskondensator  $C_a$  auf  $150\mu F$  gewählt. Der Lastwiderstand wurde auf  $R_{Last}$  auf  $10\Omega$  und die Ein- und Ausschaltzeit des MOSFETs für den Tastgrad d=0, 5 eingestellt. Die rote Kurve (L1.I) stellt den Stromverlauf der Induktivität L1 dar. Entsprechend der anliegenden Spannung an der Induktivität im Durchlassbetrieb des MOSFETs steigt der Strom durch die Induktivität an. Die schwarze Kurve (RLast.I) stellt den Stromverlauf durch den Lastwiderstand dar. Dieser verhält sich proportional zur Spannung des Ausgangskondensators.

Abbildung 3.2.: Simulation des Tiefsetzstellers; Verlauf des Induktivitäts- (L1.I, rot) und Laststroms (RLast.I, schwarz);  $U_e=12V$ ,  $R_{Last}=10\Omega$ , L1=1mH,  $f_{Takt}=18kHz$ , d=0, 5

Der Stromrippel  $\Delta I_L = I_{L,max} - I_{L,min}$  beträgt laut Simulation etwa 167mA. Somit stimmt auch die Theorie mit dem Ergebnis der Simulation überein. Die Ausgangsspannung wurde in der Simulation auf etwa 6V gewandelt.

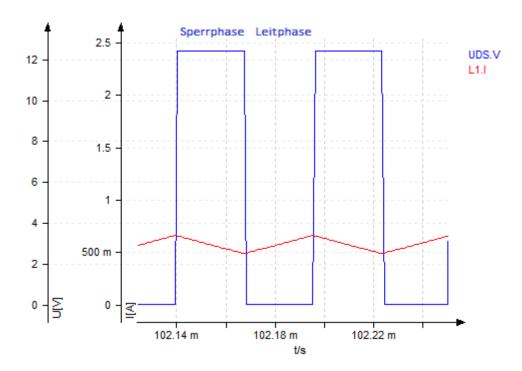

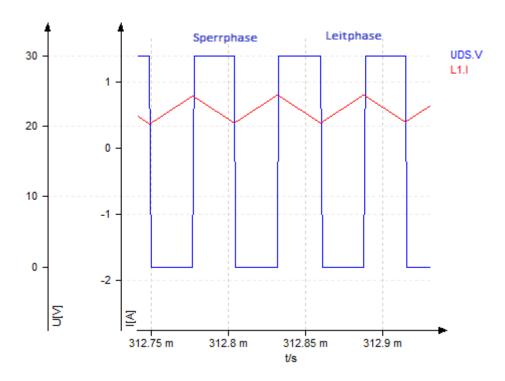

In Abbildung 3.3 erkennt man, dass der Strom in der Induktivität während der Einschaltzeit des MOSFETs ansteigt und während der Ausschaltzeit des MOSFETs abfällt, wie man es nach Gleichungen 2.1 und 2.2 erwartet.

Abbildung 3.3.: Simulation des Tiefsetzstellers; Verlauf des Induktivitätsstroms (L1.I, rot) bei Leit- und Sperrphase des MOSFETs (UDS.V, blau);  $U_e=12V$ ,  $R_{Last}=10\Omega$ , L=1mH,  $f_{Takt}=18kHz$ , d=0.5

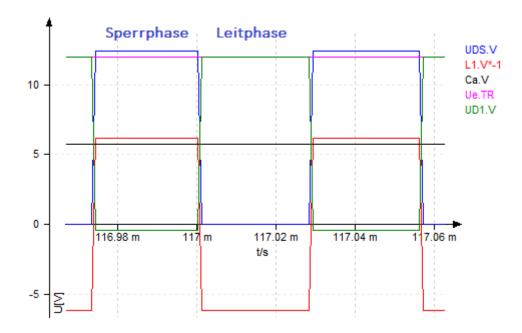

In Abbildung 3.4 werden die Spannungsverläufe dargestellt. Die schwarze Kurve (Ca.V) zeigt den Spannungsverlauf am Ausgangskondensator  $C_a$  bzw. an der Last  $R_{Last}$  und die rote Kurve (L1.V\*-1) den invertierten Spannungsverlauf an der Induktivität L1. Addiert man beide Kurven im Durchlassbetrieb des MOSFETs, ergibt sich die grüne Spannungskurve (UD1.V) (Spannung an der Diode). Die pinke Kurve (Ue.TR) ist die 12V konstante Gleichspannung der Eingangsspannungsquelle. Da parallel zum Ausgangskondensator ein Lastwiderstand angeschlossen und der Ladestrom des Kondensators nicht konstant ist, schwankt die Kondensatorspannung bzw. Lastspannung. Da diese Schwankung sehr klein ist, ist dies in Abbildung 3.4 nicht erkennbar. Bei leitendem MOSFET liegt die Eingangsspannung an der Diode (UD1.V, grün).

Im Sperrbetrieb des MOSFETs erzeugt die Induktivität eine so hohe Spannung, dass der Entmagnetisierungsstrom weiter fließen kann. In diesem Fall muss die Induktivität die Kondensatorspannung und die Durchlassspannung der Diode aufbringen.

Bedingt durch den Entmagnetisierstrom der Induktivität durch die Diode, muss der MOSFET zusätzlich zur Eingangspannung auch die Durchlassspannung der Diode sperren.

Abbildung 3.4.: Simulation des Tiefsetzstellers; Verlauf der Drain-Source-Spannung (UDS.V, blau), der Diodenspannung (UD1.V, grün), der invertierte Induktivitätsspannung (L1.V\*-1, rot), der Ausgangsspannung (Ca.V, schwarz) und der Eingangsspannung (Ue.TR, pink);  $U_e=12V$ ,  $R_{Last}=10\Omega$ , L1=1mH,  $f_{Takt}=18kHz$ , d=0.5

Die Abbildung 3.5 zeigt den Stromverlauf durch den Ausgangskondensator (Ca.I, grün), die Induktivität (L1.I, rot) und durch die Last (RLast.I, schwarz). Ist der Strom durch die Induktivität größer als der Laststrom, wird der Ausgangskondensator geladen und es fließt ein positiver Kondensatorstrom. Wenn der Strom durch die Induktivität kleiner als der Laststrom ist, wird der Ausgangskondensator entladen und der Kondensatorstrom ist negativ. Die schaltfrequente Schwankung des Induktivitätsstroms fließt durch den Ausgangskondensator. Daher muss bei der Auswahl des Ausgangskondensators auf ihre Wechselstrombelastbarkeit geachtet werden. Der dreieckförmige Induktivitätsstrom  $\Delta I_L$  erzeugt mit dem Innenwiderstand ESR des Ausgangskondensators eine Verlustleistung  $P_v = I_{C,eff}^2 \cdot ESR$ . Wegen der damit verbundenen Erwärmung darf nur ein begrenzter Wechselstrom durch den Kondensator fließen. [6]

Abbildung 3.5.: Simulation des Tiefsetzstellers; Verlauf des Induktivitätsstroms (L1.I, rot) und Kondensatorstroms (Ca.I, schwarz);  $U_e=12V$ ,  $R_{Last}=10\Omega$ , L1=1mH,  $f_{Takt}=18kHz$ , d=0.5

Die Abbildung 3.6 zeigt den Stromverlauf der Induktivität (L1.I, rot) an der Lückgrenze im ungünstigsten Fall. Der Stromfluss durch die Induktivität erreicht am tiefsten Punkt genau 0A. Wenn der Ausgangsstrom(RLast.I, schwarz) den Mindestausgangsstrom  $I_{a,min} = 83,33mA$  unterschreitet, beginnt der Induktivitätsstrom zu lücken und die Gleichungen für den nicht lückenden Betrieb sind nicht mehr gültig.

Abbildung 3.6.: Simulation des Tiefsetzstellers; Verlauf des Induktivitätsstroms (L1.I, rot) und Laststroms (RLast.I, schwarz) an der Lückgrenze;  $U_e=12V$ ,  $R_{Last}=72\Omega$ , L1=1mH,  $f_{Takt}=18kHz$ , d=0.5

In Abbildung 3.7 wurde der Lastwiderstand auf  $500\Omega$  gesetzt und der lückende Betrieb bei d=0, 5 simuliert. Die Ausgangsspannung wurde auf 9,7V gewandelt und die Beziehung  $U_a=U_e\cdot d$  ist nicht mehr gültig.

Abbildung 3.7.: Simulation des Tiefsetzstellers; Verlauf des Induktivitätsstroms (L1.I, rot) und Laststroms (RLast.I, schwarz) im Lückbetrieb;  $U_e=12V$ ,  $R_{Last}=500\Omega$ , L1=1mH,  $f_{Takt}=18kHz$ , d=0.5

In Abbildung 3.8 stellt die blaue Kurve (IT.I) den Stromverlauf des MOSFETs, die grüne Kurve (ID1.I) den Stromverlauf durch die Diode und die rote Kurve (L1.I +100mA Offset) den Stromverlauf durch die Induktivität dar. Während der Einschaltzeit des MOSFETs steigt der Induktivitätsstrom. Sperrt der MOSFET, kommutiert der Induktivitätsstrom vom MOSFET zur Diode. Der Induktivitätsstrom nimmt ab. Die Strombelastbarkeit des MOSFETs und der Diode muss also größer als der maximale Induktivitätsstrom sein.

Abbildung 3.8.: Simulation des Tiefsetzstellers; Verlauf des Induktivitäts-, des Dioden,- und des Transistorstrom;  $U_e=12V$ ,  $R_{Last}=10\Omega$ , L1=1mH,  $f_{Takt}=18kHz$ , d=0.5

# 3.3. Simulation des Hochsetzstellers

Der entworfene Hochsetzsteller, der in Kapitel 4.1.5 beschrieben wird, hat unter Vernachlässigung der Spannungsabfälle an dem Schalttransistor und an der Diode (in den jeweiligen Einschaltphasen) eine maximale Ausgangsspannung von 50V. Der Eingangsspannungsbereich des in Kapitel 4.1.5 umgesetzten Hochsetzstellers liegt zwischen 12V bis 25V und der Schaltfrequenzbereich erstreckt sich zwischen 9kHz und 20kHz.

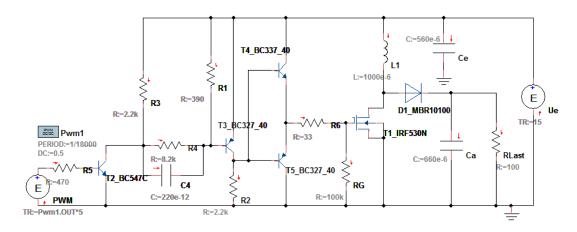

Die Simulationsschaltung von dem Hochsetzsteller wird in Abbildung 3.9 dargestellt. Bei dem Schalter handelt es sich um ein N-Kanal MOSFET IRF530N mit kleine Gate-Kapazität. Die beim Tiefsetzsteller gewählte Schottky-Diode MBR10100 mit  $U_{R,max}=100V$  und  $I_{Fav}=10A$  wurde auch hier eingesetzt.

Abbildung 3.9.: Simulation des Hochsetzstellers

Die Treiberschaltung wurde aus dem Buch "Schaltnetzteile in der Praxis" [6] entnommen. Wenn der Transistor T2 durchschaltet, bekommt T3 über R4 parallel zu C4 schnell Basisstrom und schaltet durch. Die Basen von T4 und T5 werden auf positive Versorgungsspannung angehoben, sodass T4 durchschalten kann. Das Gate des MOSFETs bekommt über den niederohmigen Ausgang von T3 positive Spannung und schaltet durch. Schaltet der Transistor T2 ab, wird der Transistor T3 über die positive Spannung an C4 binnen kurzem gesperrt. Der Transistor T5 bekommt nun über den Widerstand R2 Basisstrom. Das Gate des MOSFETs wird somit schnell mit Masse verbunden und der MOSFET schaltet aus.

Der maximale Stromrippel  $\Delta I_{L,max}$  bei einem Hochsetzsteller tritt bei einem Tastgrad d=0,5 auf. Desweiteren ist auch die maximale Ausgangsspannung  $U_{a,max}$  und die geringste Taktfrequenz  $f_{Takt,min}=9kHz$  von Bedeutung. Für L=1mH beträgt nach Gleichung 2.15 im ungünstigsten Fall der maximale Stromrippel  $\Delta I_{L,max}$  in der Induktivität:

$$\Delta I_{L,max} = \frac{U_{a,max} \cdot (1 - d) \cdot d}{L \cdot f_{Takt,min}} = \frac{50V \cdot (1 - 0, 5) \cdot 0, 5}{1mH \cdot 9kHz} = 1,4A$$

Die nachfolgende Simulationen wurden mit der Taktfrequenz von 18kHz, mit der Eingangsspannung von 15V, mit der Induktivität von 1mH und dem Tastgrad d=0,5 durchgeführt.

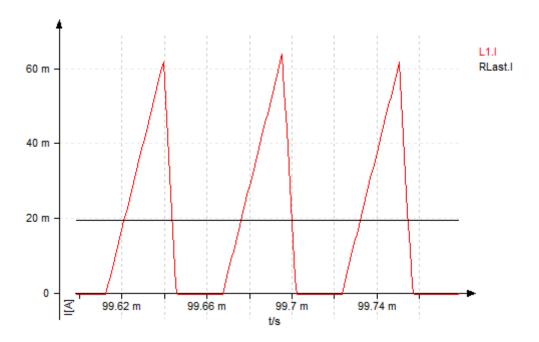

Bei der Simulation in Abbildung 3.9 wurde der Lastwiderstand auf  $288\Omega$  eingestellt und der Induktivitätsstrom (L1, rot) an der Lückgrenze simuliert. Bei einem Tastgrad d=0, 5 erreicht die Ausgangsspannung etwa den doppelten Wert der Eingangsspannung. Laut Gleichung 2.18 beträgt der Mindestausgangsstrom  $I_{a,min}$  an der Lückgrenze:

$$I_{a,min} = \frac{15V}{8 \cdot 1mH \cdot 18kHz} = 104mA$$

Der berechnete minimale Ausgangsstrom stellt sich also bei einem Lastwiderstand von  $R_{Last,grenze} = 288\Omega$  ein.

$$R_{Last,grenze} = \frac{30V}{104mA} = 288\Omega$$

Abbildung 3.10.: Simulation des Hochsetzstellers; Induktivitäts- und Laststrom an der Lückgrenze; ( $U_e=15V, R_{Last}=288\Omega, L1=1mH, f_{Takt}=18kHz, d=0,5$ )

Der Eingangsstrom (Ie.AVG, pink) ist der Mittelwert des Induktivitätsstroms. Wie die Gleichung 2.17 und die Simulation in Abbildung 3.10 zeigen, ist der Eingangsstrom  $I_e=208mA$  bei d=0, 5 doppelt so groß als der Ausgangsstrom  $I_a=104mA$ . Der Induktivitätsstrom schwankt zwischen  $I_{L,min}=0A$  und  $I_{L,max}=416mA$ .

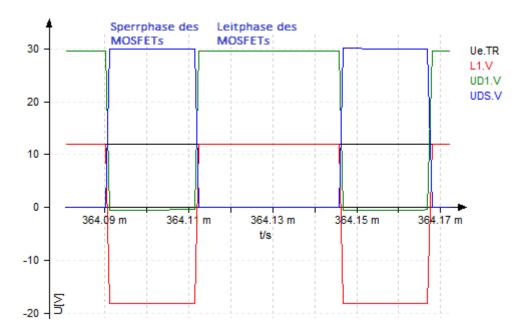

In Abbildung 3.11 ist der Verlauf des Induktivitätsstroms im nicht lückenden Betrieb zu sehen. Man erkennt, dass der Strom durch die Induktivität während der Leitphase des MOSFETs (UDS.V, blau) ansteigt und in der Sperrphase abfällt, (wie erwartet). Um die Schwankungsbreite zu reduzieren, kann man die Induktivität oder die Frequenz erhöhen. Allerdings werden die Schaltverluste an dem MOSFET mit steigender Frequenz größer und für eine höhere Induktivität vergrößert sich die Baugröße der Spule. Während der Sperrphase liegt über dem MOSFET etwa die Ausgangsspannung 30V als Sperrspannung an.

Abbildung 3.11.: Simulation des Hochsetzstellers; Stromverlauf an der Induktivität bei Leitund Sperrphase des MOSFETs;  $(U_e=15V,R_{Last}=100\Omega,L1=1mH,f_{Takt}=18kHz,d=0,5)$

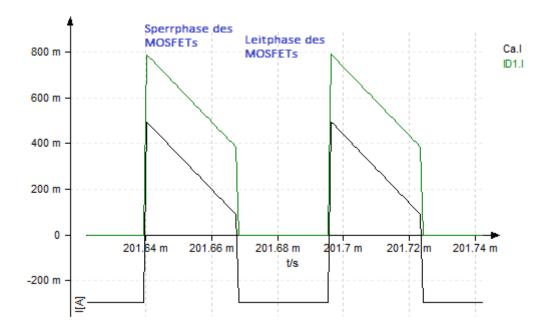

Der Stromverlauf durch den Ausgangskondensator (Ca.I, schwarz) wird in Abbildung 3.12 dargestellt. Die grüne Kurve (ID1.I) zeigt den Stromverlauf durch die Diode. Während der Leitphase des MOSFETs sperrt die Diode, der Kondensatorstrom wird negativ und übernimmt die Stromlieferung. Während der Sperrphase des MOSFETs lädt sich der Kondensator auf. Die Diode leitet den Induktivitätsstrom, der während dieser Phase sinkt. Der Strom in den Ausgangskondensator ist lückend.

Abbildung 3.12.: Simulation des Hochsetzstellers; Dioden- und Kondensatorstrom; ( $U_e = 15V, R_{last} = 100\Omega, L1 = 1mH, f = 18kHz, d = 0, 5$ )

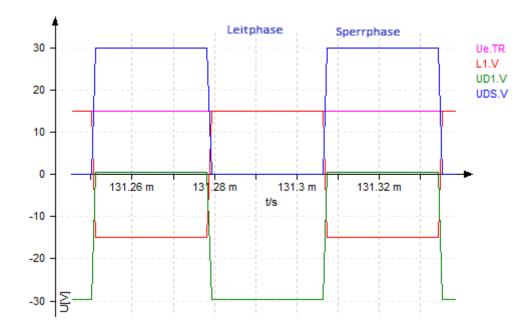

Die Abbildung 3.13 zeigt die Spannungsverläufe im eingeschwungenen Zustand. Die blaue Kurve (UDS.V) stellt den Spannungsverlauf an dem MOSFET dar. Dieser sperrt während der Sperrphase,- die um die Durchlasspannug der Diode verminderte Ausgangsspannung. Die pinke Kurve (Ue.V) ist die konstante Gleichspannung der Eingangsspannungsquelle und die rote Kurve (L1.V) der Spannungsverlauf an der Induktivität. Im Sperrbetrieb des MOSFETs kehrt die Polarität der Induktivitätsspannung um und über dem MOSFET fällt die Summe der Eingangs- und Induktivitätsspannung bzw. die Ausgangsspannung als Sperrspannung ab. Während der Leitphase des MOSFETs liegt die Ausgangsspannung als Sperrspannung über die Diode an.

Abbildung 3.13.: Simulation des Hochsetzstellers; Spannungsverläufe;  $(U_e = 15V, R = 100\Omega, L1 = 1mH, f_{Takt} = 18kHz, d = 0, 5)$

# 3.4. Simulation des Tief-/Hochsetzstellers

Der entworfene Tief-Hochsetzsteller, der in Kapitel 4.1.6 beschrieben wird, hat einen Eingangsspannungsbereich von 10V bis 14V und einen Schaltfrequenzbereich von 9kHz bis 20kHz.

Die Simulationsschaltung von dem invertierenden Tief-/Hochsetzsteller wird in Abbildung 3.14 dargestellt. Der Schalter in der Grundschaltung wurde mit einem P-Kanal MOSFET IRF9530N realisiert. Die beim Tiefsetzsteller und beim Hochsetzsteller eingesetzte Schottky-Diode MBR10100 wurde auch hier beim Tief-/Hochsetzsteller eingesetzt.

Abbildung 3.14.: Simulationsschaltung invertierenden Tief- und Hochsetzsteller

Für die folgende Simulationen wurde die Eingangsspannung auf 12V und die Taktfrequenz  $f_{Takt}$  auf 18kHz eingestellt. Die Induktivität L1 wurde auf 1mH, der Tastgrad auf d=0, 6 und der Lastwiderstand  $R_{Last}$  auf  $100\Omega$  gewählt.

Der Stromrippel  $\Delta I_L$  in der Induktivität wird mit steigendem Tastgrad größer. Der Mindestausgangsstrom  $I_{a,min}$  beträgt im ungünstigsten Fall (d=0,5) bei minimaler und maximaler Schaltfrequenz:

$$I_{a,min,9kHz} = \frac{U_{e,max} \cdot f_{Takt}}{8 \cdot L} = 194 mA$$

$$I_{a,min,20kHz} = \frac{U_{e,max} \cdot f_{Takt}}{8 \cdot I} = 87,5mA$$

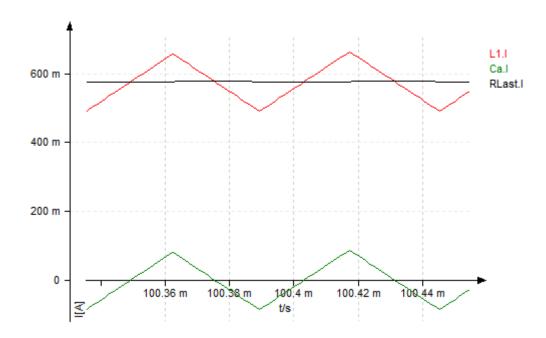

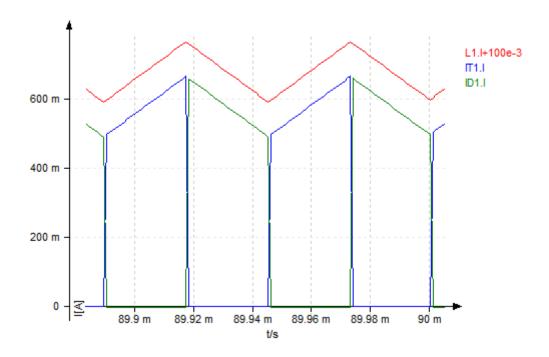

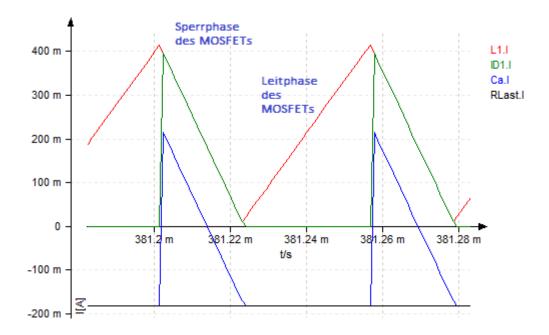

Die Abbildung 3.15 stellt die Stromverläufe dar. Sperrt der MOSFET, übernimmt die Diode (ID1.I, grün) den Induktivitätsstrom (L1.I, rot). Während der Leitphase des MOSFETs ist der Diodenstrom gleich null und der Ausgangskondensator (Ca.I, blau) liefert den Laststrom (RLast.I, schwarz). Beim Tief-/Hochsetzsteller wird die Energie nur in der Sperrphase des MOSFETs an den Ausgang abgegeben. Der in der Sperrphase in den Kondensator hineinfließende Strom (die blaue Kurve (Abb. 3.15)), erzeugt in der Realität an dem Innenwiderstand ESR des Ausgangskondensators einen Spannungsabfall. Während der Leitphase des MOSFETs liefert der Ausgangskondensator den Laststrom. Dieser erzeugt wieder einen

Spannungsabfall entgegengesetzter Polarität an dem Innenwiderstand des Kondensators. Beide Spannungsabfälle führen zur Erwärmung des Ausgangskondensators.

Abbildung 3.15.: Simulation des invertierenden Tief-/Hochsetzsteller; Stromverlauf am Ausgangskondensator; ( $U_e=12V$ ,  $R=100\Omega$ , L1=1mH, f=18khz, d=0,6)

In Abbildung 3.16 werden die Spannungsverläufe dargestellt. Die Ausgangsspannung wurde auf etwa 18V gewandelt. Während der Leitphase des MOSFETs liegt die Eingangsspannung an der Induktivität an und über die Diode liegt die Induktivitäts- und Ausgangsspannung bzw. die Eingangs- und Ausgangsspannung als Sperrspannung an. Während der Sperrphase kehrt die Polarität der Induktivitätsspannung um und über dem MOSFET liegt die Summe der Eingangs- und Induktivitätsspannung bzw. die Eingangs- und Ausgangsspannung als Sperrspannung an.

3. Simulationen 37

Abbildung 3.16.: Simulation des invertierenden Tief-/Hochsetzstellers; Spannungsverläufe;  $(U_e=12V,R_{Last}=100\Omega,L1=1mH,f_{Takt}=18kHz,d=0,6)$

# 4. Entwurf und Umsetzung

## 4.1. Entwurf der Schaltungen

#### 4.1.1. CADSoft EAGLE

Für die Erstellung der Schaltpläne und der Leiterplatten wurde die Version 6.5 von EAGLE verwendet. EAGLE ist ein EDA (Electronic Design Automation) Software-Paket aus dem Hause CADSoft. Vor Erstellung der Schaltpläne, musste einige Bauteile als neue Bauelemente erstellt werden. Die Schaltpläne und Layouts befinden sich im Anhang.

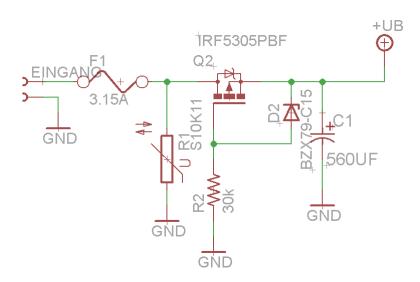

## 4.1.2. Überspannungs- und Verpolungsschutz

Für Überspannungs- und Verpolungsschutz am Eingang der jeweiligen DC/DC-Stellern wurde die Lösung in Abbildung 4.1 gewählt.

Abbildung 4.1.: Überspannungs- und Verpolungsschutz

39

Der Überspannungsschutz wurde mit einem Metalloxid-Varistor, abgekürzt MOV und vorgeschaltete Sicherung realisiert. Die Metalloxid-Varistoren (MOV) zeichnen sich durch ihr schnelles Ansprechverhalten aus. Sie sind spannungsabhängige Widerstände und verhalten sich bis zu einer gewissen Schwellenspannung unverändert. Ihr Widerstand verändert sich kaum bis zur Schwellenspannung. Ab der Schwellenspannung wird Ihr Widerstand näherungsweise exponentiell abnehmen und nur noch wenige Ohm betragen.[13] Damit steigt der Strom schnell an und löst die vorgeschaltete Sicherung aus. Die vorgeschaltete Sicherung hat einen deutlich geringeren Innenwiderstand. Daher bleibt der Spannungsabfall an der Sicherung vernachlässigbar klein.

Die Verpolungsschutz wird mit dem Einsatz eines P-Kanal MOSFET IRF5305 vom Hersteller International Rectifier erreicht. Der Drain-Anschluss des P-Kanal MOSFET wird mit der positiven Eingangsspannung, der Source-Anschluss mit dem Eingang der Betriebsspannung der zu schützenden Schaltung und das Gate mit dem Bezugspotential verbunden. Beim Anlegen einer korrekt gepolten positiven Spannung am Eingang der Schaltung leitet als erstes nur die Body-Diode des MOSFETs. Das Potential des Gates liegt auf Masse. Wenn genügend Strom durch die Body-Diode fließt, liegt an Drain und Source eine genügend hohe Spannung an und die Body-Diode (interne Freilaufdiode) wird überbrückt. Da auch die Spannung an der Source positiver ist als das Gate, leitet der MOSFET. Der Drain-Source-Widerstand wird niederohmig. Der für die Verpolungsschutz verwendete P-Kanal MOSFET hat einen deutlich geringeren Drain-Source-Widerstand  $R_{DS(on)}$  im vollständig durchgeschalteten Zustand. Somit bleibt auch der Spannungsabfall über den MOSFET sehr gering. Ist die Polarität der Eingangsspannung negativ, so sperren sowohl die Body-Diode als auch die Drain-Source-Strecke und die nachstehende Schaltung ist von der Eingangsspannung getrennt. Die Z-Diode BZX79-C15 begrenzt die Gate-Source-Spannung auf maximal 15V. Diese Art des Verpolungsschutzes hat den großen Vorteil, dass die Sicherung bei Verpolung nicht auslöst.

#### 4.1.3. Mikrocontroller

Für die Erzeugung eines PWM-Signals mit variablem Tastgrad und variabler Schaltfrequenz wird ein ATTiny861A Mikrocontroller aus dem Hause Atmel eingesetzt. Dieser weist die nötigen Funktionen wie PWM-Kanal und AD-Wandler mit einer Auflösung von 10-Bit auf. Der Mikrocontroller verfügt über einen internen 8*MHz*-Oszillator und eine PWM-Einheit als Hardware, die in Kapitel 4.2.1 näher beschrieben werden.

| PD                                 | IP/SOIC/TSS | OP                              |

|------------------------------------|-------------|---------------------------------|

|                                    |             | 1                               |

| (MOSI/DI/SDA/OC1A/PCINT8) PB0 .    | 1 20        | PA0 (ADC0/DI/SDA/PCINT0)        |

| (MISO/DO/OC1A/PCINT9) PB1          | 2 19        | PA1 (ADC1/DO/PCINT1)            |

| (SCK/USCK/SCL/OC1B/PCINT10) PB2    | 3 18        | PA2 (ADC2/INT1/USCK/SCL/PCINT2) |

| (OC1B/PCINT11) PB3                 | 4 17        | PA3 (AREF/PCINT3)               |

| VCC 🗆                              | 5 16        | ☐ AGND                          |

| GND .                              | 6 15        | AVCC                            |

| (ADC7/OC1D/CLKI/XTAL1/PCINT12) PB4 | 7 14        | PA4 (ADC3/ICP0/PCINT4)          |

| (ADC8/OC1D/CLKO/XTAL2/PCINT13) PB5 | 8 13        | PA5 (ADC4/AIN2/PCINT5)          |

| (ADC9/INT0/T0/PCINT14) PB6         | 9 12        | PA6 (ADC5/AIN0/PCINT6)          |

| (ADC10/RESET/PCINT15) PB7          | 10 11       | PA7 (ADC6/AIN1/PCINT7)          |

|                                    |             |                                 |

Abbildung 4.2.: Pin-Belegung des Atmel ATtiny861A [1]

Die Beschaltung des Mikrocontrollers (Abb. 4.3) besteht aus einer stabilen Versorgungsspannung von 5V, zwei Glättungskondensatoren, der möglichst nahe am Mikrocontroller angebracht sind und einem Pull-Up Widerstand für den Reset-Pin.

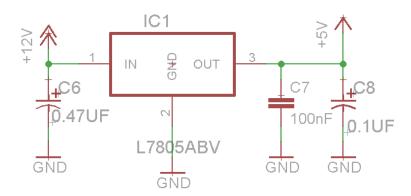

Abbildung 4.3.: Beschaltung des Mikrocontrollers

Der Festspannungsregler (Abb. 4.4) im TO-220 Gehäuse vom Hersteller STMICROELEC-TRONICS erzeugt eine konstante Gleichspannung von 5V und versorgt den Mikrocontroller und den AD-Wandler im Mikrocontroller. Neben den im Datenblatt des L7805ABV geforderten Elektrolytkondensatoren am Ein- und Ausgang sind zusätzlich noch zwei kleine Keramikkondensatoren den Elektrolytkondensatoren parallel geschaltet. Diese sollen durch ihren geringen Innenwiderstand hochfrequente Störsignale filtern. Die Elektrolytkondensatoren haben hingegen einen großen Innenwiderstand und sind für die niederfrequente Filterung ausgelegt. Da nur sehr wenig Strom durch den Festspannungsregler fließt, ist ein gesonderter Kühlkörper nicht nötig.

Abbildung 4.4.: 5V-Spannungsregler

Für die Steuerung des Tastgrades wurde am ADC-Kanal 0 des Mikrocontrollers ein linearer Potentiometer als Spannungsteiler angeschlossen und mit einer internen Referenzspannung von 5V verglichen und ausgewertet. Die eingelesenen Werte werden auf den Bereich [0-1] normiert und dienen somit als Vorgabe für den Tastgrad der MOSFET-Ansteuerung. Über ein weiteres Potentiometer, das als Spannungsteiler am ADC-Kanal 1 des Mikrocontrollers angeschlossen ist, kann die Schaltfrequenz eingestellt werden.

#### 4.1.4. Der Tiefsetzsteller

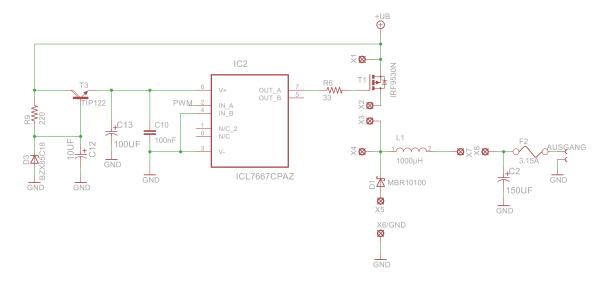

Der Leistungsteil des Tiefsetzstellers (Abb. 4.5) besteht aus dem MOSFET T1 als Schalter, der Speicherdrossel L1, der Schottky-Diode D1 und die Ausgangskapazität C2. Die eingesetzte Schottky-Diode MBR10100 hat eine geringe Sperrverzugsladung  $Q_{rr}$  und daher auch eine kleine Sperrverzugszeit  $t_{rr}$ , was eine schnelle Schaltzeit und sehr niedrige Schaltverlustleistung zur Folge hat.

| Bauelement                   | Bezeichnung/Beschreibung    | Hersteller             |

|------------------------------|-----------------------------|------------------------|

| T1 Schalttransistor (MOSFET) | IRF9530N, P-Kanal MOSFET    | Internation Rectifier  |

| L1 Induktivität              | 1410524C 1mH/2,4A           | Murata Power Solutions |

| D1 Schottky-Diode            | MBR10100                    | ON Semiconductor       |

| C1 Eingangskondensator       | EEUFR1J561S, $560\mu F/63V$ | Panasonic              |

| C2 Ausgangskondensator       | EEUFR1J151, $150\mu F/63V$  | Panasonic              |

| IC2 Treiber-IC               | ICL7667                     | intersil               |

Tabelle 4.1.: Tabellarische Auflistung der zum Leistungsteil des Tiefsetzstellers gehörenden Bauelemente

Abbildung 4.5.: Leistungsteil des Tiefsetzstellers

Die Messpunkte X2-X3, X5-X6 und X7-X8 auf der Platine werden mit einem Kabel verbunden, damit der Transistor-, der Dioden- und Induktivitätsstrom mit einer Stromzange gemessen bzw. oszilloskopiert werden kann.

Die Elektrolytkondensatoren am Ein- und Ausgang haben eine Spannungsfestigkeit von 63V. Beim Tiefsetzsteller belastet hauptsächlich die schaltfrequente Schwankung des Induktivitätsstroms den Ausgangskondensator. Die maximal zulässige Strombelastbarkeit  $I_{C,eff,max}$  des eingesetzten Ausgangskondensators beträgt laut Datenblatt 1,019A (bei  $105^{\circ}C,10kHz \leq f_{Takt} \leq 100kHz$ ).

Als Induktivität wurde das Produkt 1410524C von Murata Power Solutions aufgrund der hohen Induktivität 1mH (mit Kern), kleiner Bauform und der ausreichenden Strombelastbarkeit ausgewählt. Diese hat laut Datenblatt einen maximalen Strombelastbarkeit von 2,4A und einen Gleichstromwiderstand  $R_{DC}$  von  $277m\Omega$ . Der angegebene Strom von 2,4A ist ein maximaler Dauerstrom bei einem Temperaturanstieg von  $50^{\circ}C$  oder bei einem Induktivitätsabfall von 60%. Dadurch wird der Stromrippel  $\Delta I_L$  größer, was im schlimmsten Fall den MOSFET und die Diode zerstören kann. Der Strom in der Induktivität heizt am Gleichstromwiderstand  $R_{DC}$  der Induktivität und führt zu einer Verlustleistung.

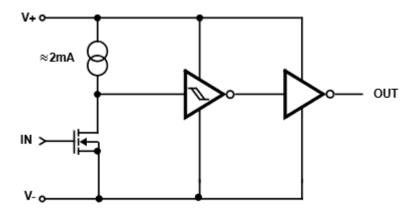

Da für die Ansteuerung des P-Kanal MOSFETs IRF9530N mit dem PWM-Signal eine Spannung von 5V und der Strom von max. 40mA, die der Mikrocontroller liefern kann nicht ausreicht wurde der invertierende CMOS-Treiberbaustein ICL7667 vom Hersteller intersil eingesetzt. Der ICL7667 stellt also die Schnittstelle zwischen dem Mikrocontroller und dem Leistungsteil dar. Er verstärkt das 5V Signal vom Mikrocontroller und kann kurzfristig bis zu 1,5A aufnehmen und abgeben. Das Blockdiagramm des CMOS-Treiberbausteins ICL7667 wird in Abbildung 4.6 dargestellt.

Abbildung 4.6.: Blockdiagramm des CMOS-Treiberbausteins ICL7667 des Herstellers intersil

Der P-Kanal MOSFET IRF9530N benötigt zum Durchschalten eine gegenüber Source negative Spannung und schaltet laut Datenblatt ab  $U_{GS}=-8V$  vollständig durch. Eine Spannung von 0V am Steuereingang IN des invertierenden CMOS-Treibers sorgt dafür, dass die Versorgungsspannung des Treibers mit dem Ausgang verbunden ist. Der MOSFET IRF9530N sperrt, weil am Gate bzw. am Ausgang des CMOS-Treibers OUT gegenüber Source etwa 0V anliegt. Eine positive Spannung am Steuereingang IN des invertierenden CMOS-Treibers bewirkt, dass die Masse mit dem Gate des MOSFETs verbunden ist. Somit liegt am Gate eine gegenüber Source negative Spannung an. Die Betriebsspannung am CMOS-Treiberbaustein wurde durch eine 18V-Z-Diode begrenzt.

#### Schaltzeiten an MOSFETs

Bei jedem Ein- und Ausschalten muss die Eingangskapazität  $C_{iss}(=C_{gs}+C_{gd})$  des MOS-FETs umgeladen werden, wozu für einen kurzen Zeitraum ein Gatestrom  $I_g$  erforderlich ist. Während der stationären Betriebszustände "Leitend" und "Sperrend" wird kein Gatestrom benötigt. Die Schaltzeit  $t_s$  wird durch die Zeit bestimmt, die man zum Umladen des Gates benötigt und ist bei gegebenem Gatestrom proportional zur Gesamtgateladung  $Q_g$ . Die Gateladung wird in den Datenblättern zusätzlich zur Eingangskapazität angegeben.[4]

$$t_{s} = \frac{Q_{g}}{I_{g}} \tag{4.1}$$

Die Ein- und Ausschaltzeiten werden in der Praxis durch einen zusätzlichen Gatewiderstand  $R_g$  begrenzt, weil die Zuleitungsinduktivität zum Gate und die Eingangskapazität  $C_{iss}$  zusammen einen Schwingkreis bilden kann. Der MOSFET kann dann während des Umschalt-

vorganges anfangen zu schwingen. Der Gatewiderstand soll die Schaltgeschwindigkeit begrenzen um diesen potentiellen Schwingkreis zu dämpfen. [4]

Der beim Tiefsetzsteller als Schalter eingesetzte MOSFET IRF9530N hat laut Datenblatt [10] bei einer  $U_{GS}=-10V$ ,  $I_{DS}=-8$ , 4A und  $U_{DS}=-80V$  eine maximale Gesamtgateladung  $Q_g$  von 58nC. Wenn das Gate mit 1, 5A umgeladen wird, ergibt sich nach Gleichung eine gesamte Schaltzeit  $t_s$  von 38ns.

$$t_s = \frac{Q_{g,IRF9530N}}{I_g} = \frac{58nC}{1,5A} = 38ns \tag{4.2}$$

Möchte man in 0,  $5\mu s$  schalten, 1% der gesamten Periodendauer  $T_{Takt}=18kHz^{-1}$ , ist ein Gatestrom von 116mA benötigt. Dieser Strom fließt nur für einen kurzen Zeitraum von max. 0,  $5\mu s$ .

$$I_{g,icl7667} = \frac{Q_{g,IRF9530N}}{t_s} = \frac{58nC}{0.5\mu s} = 116mA$$

(4.3)

Der Gatewiderstand  $R_g=33\Omega$  am MOSFET IRF9530N begrenzt den maximalen Treiberstrom auf  $I_{g,max}=\frac{\Delta U}{R_g}$ .  $\Delta U$  ist der Spannungshub am Gate. Der eingesetzte CMOS-Treiber kann also ausreichend schnell schalten.

#### Eckdaten des Tiefsetzstellers

Die Eckdaten des Tiefsetzstellers sind in Tabelle 4.2 dargestellt. Der maximale Eingangsstrom  $I_{e,max}$ ist nicht angegeben, weil der immer kleiner oder gleich (bei d=1) des Ausgangsstroms ist. Der maximale Ausgangsstrom muss kleiner als die maximale Strombelastbarkeit der Induktivität sein. Daher wurde als maximaler Ausgangsstrom 2,4A festgelegt.

| $U_{e,max} \leq U_e \leq U_{e,max}$          | $10V \le U_e \le 14V$         |

|----------------------------------------------|-------------------------------|

| I <sub>e,max</sub>                           | -                             |

| $U_{a,max}$                                  | -                             |

| I <sub>a,max</sub>                           | 2,4A                          |

| $f_{Takt,min} \le f_{Takt} \le f_{Takt,max}$ | $9kHz \le f_{Takt} \le 20khz$ |

| $d_{min} \leq d \leq d_{max}$                | $0 \le d \le 1$               |

Tabelle 4.2.: Eckdaten des Tiefsetzstellers

Der Eingangsspannungsbereich des Tiefsetzstellers wird auch vom Mikrocontroller überwacht und für den Fall, dass er unter- oder überschritten wird, schaltet der Mikrocontroller

das PWM-Signal ab, sodass am Ausgang des Tiefsetzstellers 0V anliegt. Der zulässige Schaltfrequenzbereich wird auch durch den Mikrocontroller begrenzt, sodass die minimale bzw. maximale Schaltfrequenz nicht überschritten wird.

#### 4.1.5. Der Hochsetzsteller

Beim Hochsetzsteller wurde der Schalter mit einem N-Kanal MOSFET IRF530N realisiert. Für die Ansteuerung des MOSFETs wurde der nichtinvertierende CMOS-Treiberbaustein TC4427 des Herstellers Microchip eingesetzt und schafft einen Ausgangsspitzenstrom von bis zu 1,5A.

| Bauelement                      | Bezeichnung/Beschreibung     | Hersteller             |

|---------------------------------|------------------------------|------------------------|

| T1 Schalttransistor (MOSFET)    | IRF530N (Leistungs-MOSFET)   | Internation Rectifier  |

| L1 Induktivität                 | 1410524C 1mH/2,4A            | Murata Power Solutions |

| D1 Schottky-Diode               | MBR10100                     | ON Semiconductor       |

| C1 Eingangskondensator          | EEUFR1J561S, $560\mu F/63V$  | Panasonic              |

| Ausgangskondensatoren C2 und C3 | EEUFC2A331S, $330\mu F/100V$ | Panasonic              |

| IC2 Treiber-IC                  | TC4427                       | Microchip              |

Tabelle 4.3.: Tabellarische Auflistung der zum Leistungsteil des Hochsetzstellers gehörenden Bauelemente

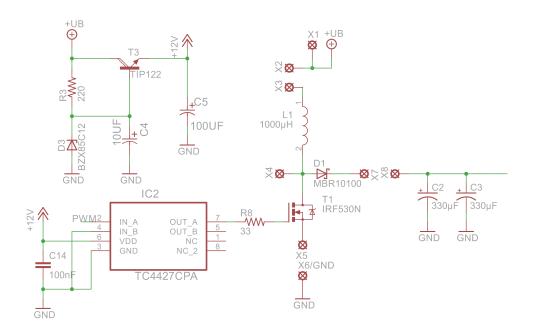

Abbildung 4.7.: Leistungsteil des Hochsetzstellers

Am Ausgang wurden zwei Elektrolytkondensatoren (Low ESR) mit je  $330\mu F/100V$  parallel geschaltet. Bei der Auswahl der Kondensatoren wurde darauf geachtet, dass ihr Innenwiderstand (ESR) nicht zu hoch ist. Zudem führt das Parallelschalten mehrerer Elektrolytkondensatoren zu einem kleineren Gesamtwiderstand und erhöht die zulässige Strombelastbarkeit des Kondensators.

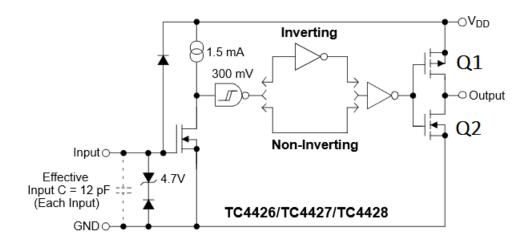

Da die Treiberleistung des eingesetzten Mikrocontrollers zur Ansteuerung des N-Kanal MOSFETs IRF530N nicht ausreicht, wurde der nichtinvertierende CMOS-Treiberbaustein TC4427 zwischen den PWM-Ausgang des Mikrocontrollers und das Gate gesetzt. Das Blockdiagramm des TC4427 ist in Abbildung 4.8 dargestellt. Der CMOS-Treiber wandelt die Kleinspannung 5V/0V des Mikrocontrollers in eine Großspannung  $V_{DD}/0V$  um. Die Spannung  $V_{DD}$  ist gleich der Betriebsspannung des CMOS-Treibers und beträgt hier konstant 12V. Ist das PWM-Signal am Eingang des Treibers "High" , wird die gemeinsame Gatespannung Q1 und Q2 auf "Low" gesetzt, Q1 sperrt und am Gate des N-Kanal MOSFETs IRF530N liegt die Spannung  $V_{DD}$ . Ist das PWM-Signal am Eingang des Treibers "Low" , wird das gemeinsame Gatespannung Q1 und Q2 auf "High" gesetzt und am Ausgang des Treibers liegt 0V an. Die MOSFETs Q1 und Q2 stellen Pull-up- und Pull-down-Ausgangstreiber für den CMOS-Treiber dar.

Abbildung 4.8.: Blockdiagramm des nicht invertierenden CMOS-Treiberbausteins TC4427 vom Hersteller Microchip

Der CMOS-Treiber TC4427 kann einen Spitzenstrom von bis zu 1,5A abgeben und aufnehmen mit welchem der beim Ein- und Ausschalten das Gate des MOSFETs IRF530N umlädt. Der  $33\Omega$  Widerstand am Gate des MOSFETs IRF530N begrenzt den maximalen Gatestrom  $I_{g,max}$  auf  $\frac{\Delta U}{33\Omega} = \frac{12V}{33\Omega} = 363 mA$ .

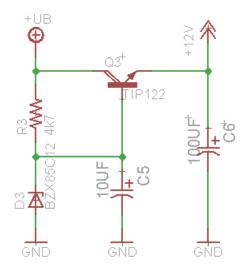

Für die Spannungsversorgung des Treibers wurde die Lösung in Abbildung 4.9 mit Darlington-Transistor TIP122 und 12V-Z-Diode BZX85C12 gewählt.[13] Der Vorwiderstand R3 wurde so dimensioniert, dass die Z-Diode noch genügend Strom bekommt und auch der Basisstrom des Darlington-Transistors bei maximalem Kollektorstrom noch ausreicht. Der Treiber-IC TC4427 hat eine maximale Betriebsspannung von 22V und wird mit dieser Lösung durch um die Basis-Emitter-Spannung des Darlington-Transistors verminderte Z-Spannung der Z-Diode begrenzt. Ein 5V-Festspannungsregler erzeugt auch aus dieser Spannung eine konstante Gleichspannung von 5V und versorgt den Mikrocontroller. Somit erstreckt sich der Eingangsspannungsbereich des Hochsetzstellers von 12V bis auf die Nennspannung des Varistors von 25V. Erhöht man die Eingangsspannung über 25V hinaus, wird die Nennspannung des Varistors überschritten.

Abbildung 4.9.: Spannungsversorgung der IC-Bausteine

#### Eckdaten des Hochsetzstellers

Die Eckdaten des Hochsetzstellers sind in Tabelle 4.4 zusammengefasst.

| $U_{e,max} \leq U_e \leq U_{e,max}$          | $12V \le U_e \le 25V$                       |

|----------------------------------------------|---------------------------------------------|

| $I_{e,max}$                                  | 2,4 <i>A</i>                                |

| $U_{a,max}$                                  | 50 <i>V</i>                                 |

| I <sub>a,max</sub>                           | _                                           |

| $f_{Takt,min} \le f_{Takt} \le f_{Takt,max}$ | $9kHz \le f_{Takt} \le 20khz$               |

| $d_{min} \leq d \leq d_{max}$                | $0 \le d \le d_{max} = 1 - \frac{U_e}{50V}$ |

Tabelle 4.4.: Eckdaten des Hochsetzstellers

Die Eingangsspannung des Hochsetzstellers wird vom Mikrocontroller überwacht und für den Fall, dass sie unter- oder überschritten wird, schaltet der Mikrocontroller das PWM-Signal ab, sodass am Ausgang des Hochsetzstellers die Eingangsspannung anliegt. Der maximale Tastgrad des PWM-Signals wird auch durch den Mikrocontroller auf  $d_{max}=1-\frac{U_e}{50V}$  begrenzt. Dadurch soll sichergestellt werden, dass der Hochsetzsteller nicht über 50V hinaus betrieben wird.

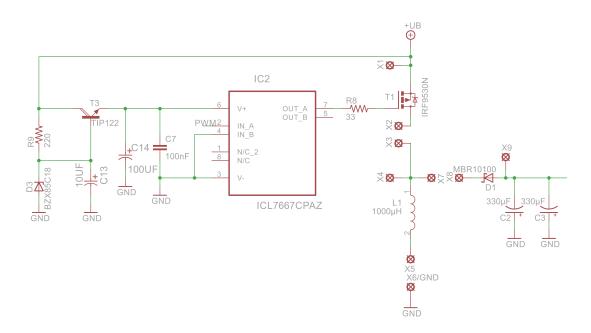

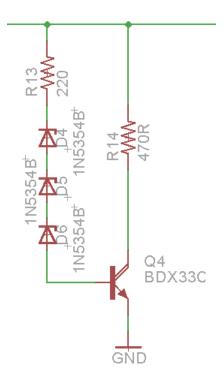

#### 4.1.6. Der Tief-/Hochsetzsteller

Der zum Leistungsteil des invertierenden Tief-/Hochsetzstellers gehörenden Bauelemente sind in Tabelle 4.5 dargestellt.

| Bauelement                      | Bezeichnung/Beschreibung             | Hersteller             |

|---------------------------------|--------------------------------------|------------------------|

| T1 Schalttransistor (MOSFET)    | IRF9530N (Leistungs-MOSFET)          | Internation Rectifier  |

| L1 Induktivität                 | 1410524C 1mH/2,4A                    | Murata Power Solutions |

| D1 Schottky-Diode               | MBR10100                             | ON Semiconductor       |

| C1 Eingangskondensator          | EEUFR1J561S, $560\mu F/63V$          | Panasonic              |

| Ausgangskondensatoren C2 und C3 | <b>EEUFC2A331S</b> , $330\mu F/100V$ | Panasonic              |