# Hochschule für Angewandte Wissenschaften Hamburg Hamburg University of Applied Sciences

# Bachelorthesis

Sener Sahin

Entwicklung einer Audiocodec-Platine und Audiosignalverarbeitung auf einem FPGA mit High-Level Synthese

# Sener Sahin

# Entwicklung einer Audiocodec-Platine und Audiosignalverarbeitung auf einem FPGA mit High-Level Synthese

Bachelorthesis eingereicht im Rahmen der Bachelorprüfung im Studiengang Informations- und Elektrotechnik am Department Informations- und Elektrotechnik der Fakultät Technik und Informatik der Hochschule für Angewandte Wissenschaften Hamburg

Betreuender Prüfer : Prof. Dr.Ing. Lutz Leutelt Zweitgutachter : Prof. Dr. Ulrich Sauvagerd

Abgegeben am 22. Juni 2018

## Sener Sahin

## Thema der Bachelorthesis

Entwicklung einer Audiocodec-Platine und Audiosignalverarbeitung auf einem FPGA mit High-Level Synthese

## **Stichworte**

Audiocodec, Codec, PCM3006, Signalverarbeitung, Platine, FPGA, VHDL, Xilinx Vivado, Xilinx Vivado HLS, High-Level Synthese

# Kurzzusammenfassung

In dieser Arbeit wird eine Audiocodec-Platine für das Labor für Digitaltechnik der Hochschule für Angewandte Wissenschaften (HAW) in Hamburg entwickelt und ein VHDL Programm für die Ansteuerung der Platine mit einem FPGA geschrieben. Zudem werden erste Erfahrungen mit der Software Vivado HLS von Xilinx gesammelt.

### Sener Sahin

## Title of the paper

Development of an Audiocodec-Board and signal processing on an FPGA with High-Level Synthesis

## **Keywords**

Audiocodec, Codec, PCM3006, Signal processing, PCB, FPGA, VHDL, Xilinx Vivado, Xilinx Vivado HLS, High-Level Synthesis

### **Abstract**

This bachelor thesis describes the development of an audiocodec pcb for the labour of digital technology on Hamburg University of Applied Sciences (HAW). For taht a vhdl application is developed to control the audiocodec pcb. Then first experience with the Xilinx Software Vivado HLS are collected.

# **Inhaltsverzeichnis**

| ΑŁ | kürz  | ungsverzeichnis                                | 7  |

|----|-------|------------------------------------------------|----|

| Та | belle | nverzeichnis                                   | 9  |

| ΑŁ | bildu | ungsverzeichnis                                | 10 |

| 1. | Einle | eitung                                         | 13 |

|    | 1.1.  | Motivation                                     | 13 |

|    | 1.2.  | Kapitelübersicht                               | 14 |

| 2. | Grui  | ndlagen                                        | 15 |

|    | 2.1.  | Bezugspegel in der Tontechnik                  | 15 |

|    | 2.2.  | Einfacher Verstärker                           | 15 |

|    |       | 2.2.1. Nicht-Inventierendes Betrieb            | 16 |

|    |       | 2.2.2. Inventierendes Betrieb                  | 16 |

|    |       | 2.2.3. Erweiterte Differenzverstärker          | 17 |

|    |       | 2.2.4. Multiple Feedback Filter                | 19 |

|    | 2.3.  | ModSys-Baseboard 2                             | 20 |

|    | 2.4.  | VHDL Grundschaltungen                          | 21 |

|    |       | 2.4.1. Flipflops                               | 21 |

|    |       | 2.4.2. Zähler/ Taktteiler                      | 22 |

|    |       | 2.4.3. Schieberegister                         | 23 |

|    |       | 2.4.4. Impulsverkürzung                        | 24 |

|    | 2.5.  | Digitale Filter und Zeitvariante Verzögerungen | 25 |

|    |       | 2.5.1. FIR-Filter                              | 25 |

|    |       | 2.5.2. Vibrato-Audioeffekt                     | 26 |

| 3. | Anfo  | orderungsanalyse                               | 28 |

|    | 3.1.  | Audiocodec                                     | 28 |

|    | 3.2.  | Platine                                        | 29 |

|    | 3.3.  | VHDL-Modell zur Codecansteuerung               | 30 |

|    | 3 4   | Audioeffekt mit HI S                           | 30 |

Inhaltsverzeichnis 5

| 4.  | Konzeption                                                               | 31        |

|-----|--------------------------------------------------------------------------|-----------|

|     | 4.1. Das Gesamtsystem                                                    | 31        |

|     | 4.2. Auswahl des Audiocodecs                                             | 32        |

|     | 4.3. Übersicht über PCM3006 Audiocodec und Schaltungslayout              | 34        |

|     | 4.4. Design der Platine                                                  | 37        |

|     | 4.4.1. Grundschaltung                                                    | 37        |

|     | 4.4.2. Pegelanpassung                                                    | 38        |

|     | 4.5. Ansteuerung des Audiocodecs                                         | 39        |

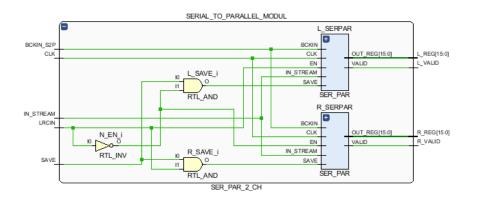

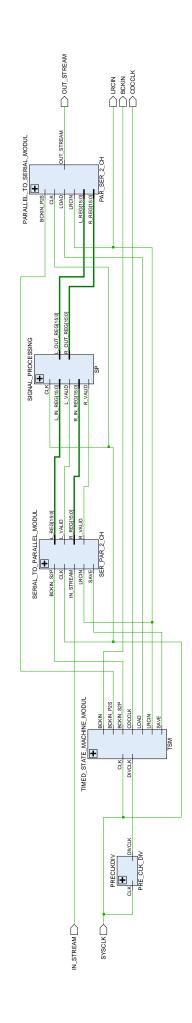

|     | 4.5.1. Serien-Parallel-Umsetzer-Modul                                    | 40        |

|     | 4.5.2. Signalverarbeitungsmodul                                          | 41        |

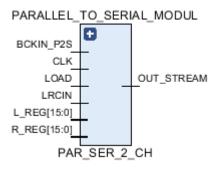

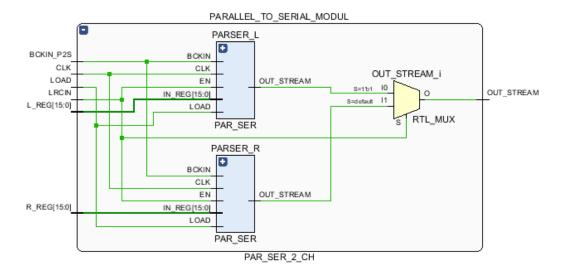

|     | 4.5.3. Parallel-Serien-Umsetzer-Modul                                    | 41        |

|     | 4.5.4. Taktteiler-Modul                                                  | 41        |

|     | 4.5.5. Timed-State-Machine                                               | 42        |

|     | 4.6. Konzept der Entwicklung eines Audioeffektes und High-Level Synthese | 43        |

| 5.  | Schaltungs- und Platinenentwurf                                          | 44        |

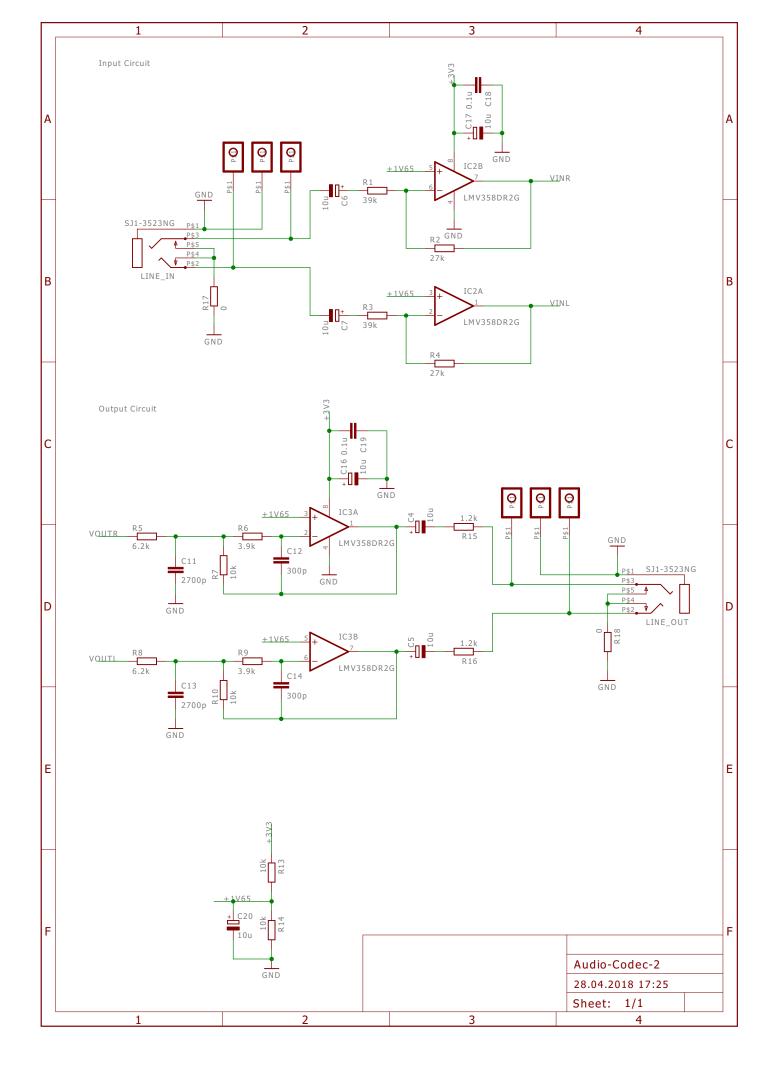

|     | 5.1. Schaltungsentwurf                                                   |           |

|     | 5.2. Platinenentwurf                                                     |           |

|     | 5.3. Evaluation der Platine                                              | 49        |

| 6.  | Digitale Schaltungsdesign                                                | <b>50</b> |

|     | 6.1. Taktteiler-Modul                                                    |           |

|     | 6.2. Timed-State-Machine-Modul                                           |           |

|     | 6.3. Serien-Parallel-Umsetzer-Modul                                      |           |

|     | 6.4. Parallel-Serien-Umsetzer-Modul                                      |           |

|     | 6.5. Evaluation des Basiscodes                                           |           |

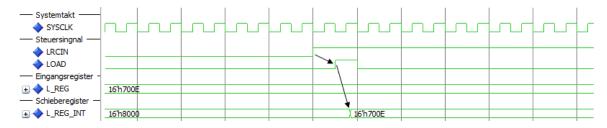

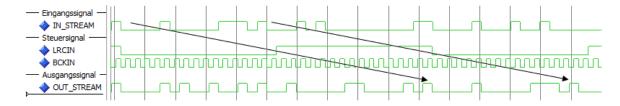

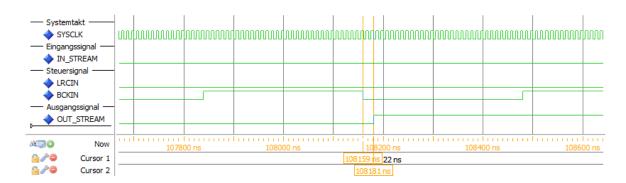

|     | 6.5.1. Zeitverhalten mit ModelSim                                        |           |

|     | 6.5.2. Simulation mit Vivado                                             |           |

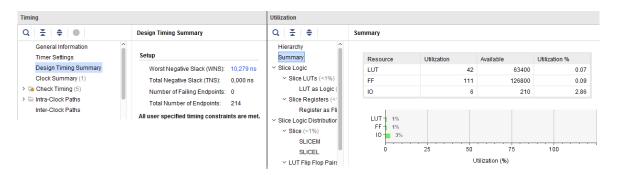

|     | 6.5.3. Evaluation der VHDL-Basisstruktur                                 | 61        |

| 7.  | Signalverarbietung mit High-Level Synthese                               | 66        |

|     | 7.1. FIR-Filter in VHDL                                                  | 66        |

|     | 7.2. FIR-Filter mit HLS                                                  | 68        |

|     | 7.3. Realisierung des Vibrato-Effektes mit HLS                           | 71        |

|     | 7.4. Evaluation von HLS                                                  | 75        |

| 8.  | Zusammenfassung                                                          | 77        |

| Lit | iteraturverzeichnis                                                      | 79        |

| Α.  |                                                                          |           |

|     | Timingdiagramm von PCM3006                                               | 81        |

| Inhaltsverzeichnis | 6 |

|--------------------|---|

|                    |   |

| В. |                                  |    |

|----|----------------------------------|----|

|    | Analoge und digitale Schaltungen | 82 |

|    | B.1. Audiocodec Board Layout     | 82 |

|    | B.2. RTL-Sicht der Basisstruktur | 85 |

| C. |                                  |    |

|    | Codes Listings                   | 87 |

# Abkürzungsverzeichnis

FPGA Field Programmable Gate Array

VHDL Very High Speed Integrated Circuit Hardware Description Language

**ADU** Analog-Digital-Umsetzer

**DAU** Digital-Analog-Umsetzer

**OpAmp** Operationsverstärker

ModSys-Board Modularsystem

I/O Input Output

MSB Bitwertigkeit, Most Significant Bit

MSB Bitwertigkeit, Least Significant Bit

FF Flipflop

**SYSCLK** Systemtakt

**CDCCLK** Codectakt

**BCKIN** Bit-Takt

**LRCIN** Wort-Takt

**FIR** finite impulse response

**HLS** High-Level Synthese

**I2C** Inter-Integrated Circuit

**I2S** Inter-IC Sound

**PWM** Pulsweitenmodulation

**PCM** Puls-Code-Modulation

IC Integrated Circuit

SPU Serien-Parallel-Umsetzer

Inhaltsverzeichnis 8

**PSU** Parallel-Serien-Umsetzer

**SNR** Rausch-Signal-Abstand

PCB Printed Circuit Board

# **Tabellenverzeichnis**

| 4.1. | Ausgewählte Audiocodec-Systeme | 32 |

|------|--------------------------------|----|

| 4.2. | Systemtakt Frequenzen [1]      | 36 |

# Abbildungsverzeichnis

| Nicht-Invertierende Grundschaltung mit einem Operationsverstärker          | 16                                                                                                     |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Invertierende Grundschaltung mit einem Operationsverstärker                | 17                                                                                                     |

| Differenzverstärkerschaltung mit einem Operationsverstärker und einem Kon- |                                                                                                        |

| densator am negativen Eingang                                              | 18                                                                                                     |

| Grundschaltung eines Multiple-Feedback-Filters                             | 19                                                                                                     |

| ModSys-Baseboard 2                                                         | 20                                                                                                     |

| Ein einzelner D-Flipflop                                                   | 21                                                                                                     |

| Ein Speicherblock von drei D-Flipflops (Register)                          | 22                                                                                                     |

| Schaltbild eines N-Bit Zählers[2]                                          | 22                                                                                                     |

| Ein linksschiebe Register[2]                                               | 23                                                                                                     |

| Blockschaltbild eines Serien-Parallel-Umsetzers                            | 24                                                                                                     |

| .Blockschaltbild eines Parallel-Serien-Umsetzers                           | 24                                                                                                     |

| .Digitale Schaltung einer Impulsverkürzung[2]                              | 25                                                                                                     |

| Blockschaltbild eines FIR-Filters[3]                                       | 26                                                                                                     |

| .Verzögerungskette mit Interpolation[4]                                    | 27                                                                                                     |

| Des Ciencellos edicares es fina cience Audichered                          | 04                                                                                                     |

|                                                                            | 31                                                                                                     |

| • • • • • • • • • • • • • • • • • • • •                                    | 34                                                                                                     |

| -                                                                          | 26                                                                                                     |

|                                                                            | 36                                                                                                     |

| •                                                                          | 38                                                                                                     |

|                                                                            | 42                                                                                                     |

| Techt zum Lauen                                                            | 42                                                                                                     |

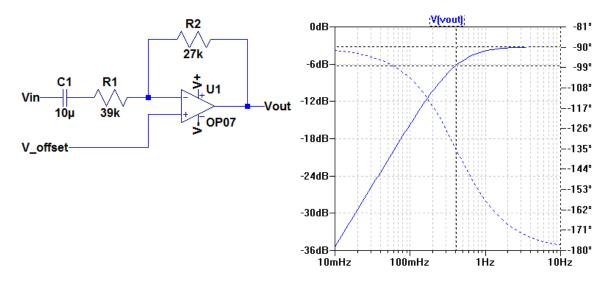

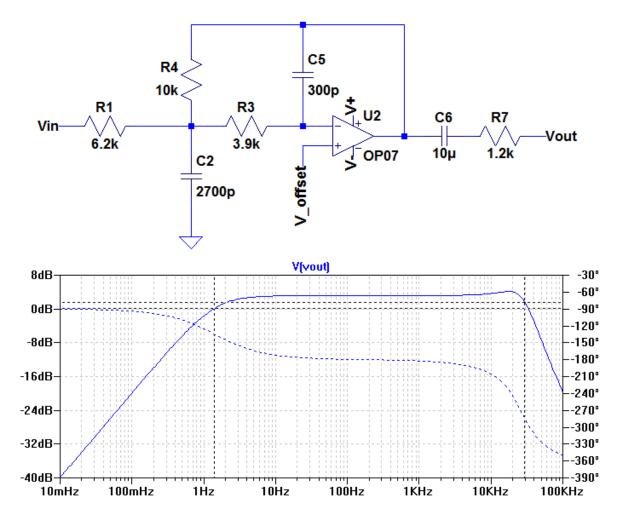

| LTspice Simulation der Eingangsschaltung; Links: Verstärkerschaltung,      |                                                                                                        |

| Rechts: Amplituden und Phasengang der Schaltung im Bereich 10mHz           |                                                                                                        |

| bis 10 Hz                                                                  | 45                                                                                                     |

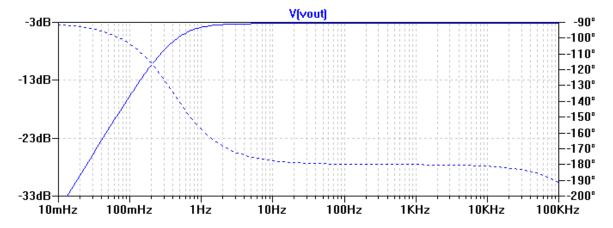

| Amplituden- und Phasengang der Eingangsverstärkerschaltung in Bereich      |                                                                                                        |

| von 10mHz bis 100kHz                                                       | 45                                                                                                     |

| LTspice Simulation der Ausgangsverstärkerschaltung; oben: die Multiple-    |                                                                                                        |

| Feedback-Filterschaltung, unten: Amplituden- und Phasengang der Multiple-  |                                                                                                        |

| Feedback-Filterschaltung in den Grenzen von 10mHz und 100kHz               | 47                                                                                                     |

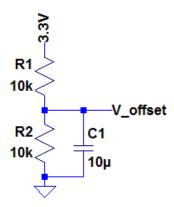

| Spannungsteiler als Offset-Schaltung                                       | 48                                                                                                     |

|                                                                            | Differenzverstärkerschaltung mit einem Operationsverstärker und einem Kondensator am negativen Eingang |

| 5.5. Bedruckte und bestückte Audiocodec-Platine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 48                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

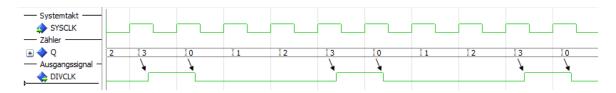

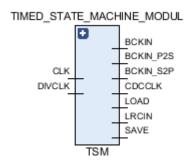

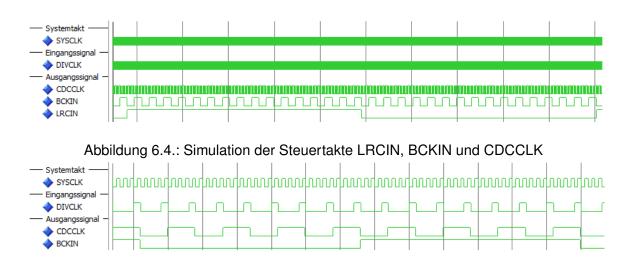

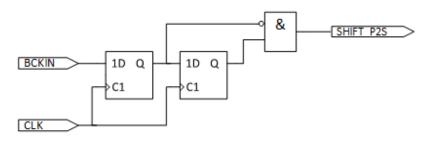

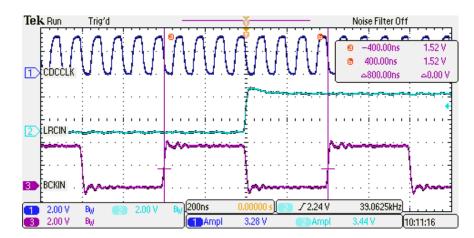

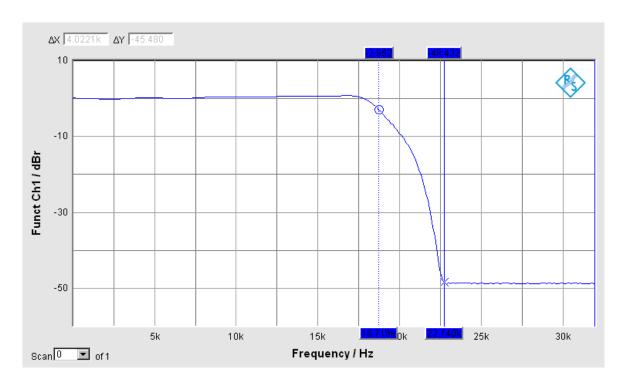

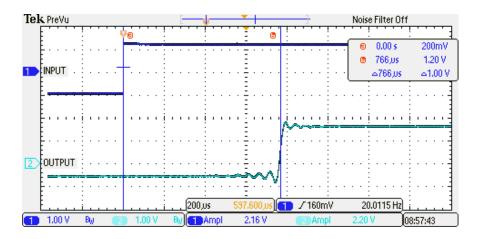

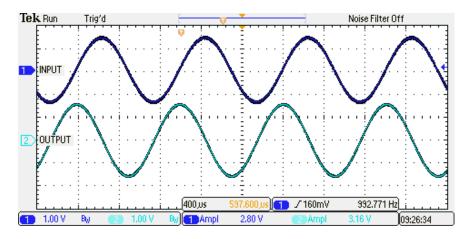

| <ul> <li>6.1. Blockschaltbild des Taktteiler-Moduls</li> <li>6.2. Zeitverlauf von DIVCLK im Taktteiler-Modul</li> <li>6.3. Blockschaltbild des TSM Modul</li> <li>6.4. Simulation der Steuertakte LRCIN, BCKIN und CDCCLK</li> <li>6.5. Simulation der Steuertakte BCKIN und CDCCLK, vergrößert</li> <li>6.6. Digitale Schaltung zur Impulsverkürzung, beispielhaft für BCKIN_P2S-Signal</li> <li>6.7. Digitale Schaltung zur Impulsverkürzung, beispielhaft für SAVE-Signal</li> <li>6.8. Zeitverhalten der BCKIN_S2P und BCKIN_P2S in Abhängigkeit zu BCKIN</li> <li>6.9. Zeitverhalten der SAVE und LOAD in Abhängigkeit zu LRCIN</li> <li>6.10. Blockschaltbild des Serien-Parallel-Umsetzer-Moduls</li> <li>6.11. Zeitverhalten der Ausgangssignale zum LRCIN-Signal und SAVE-Signal im Parallel-Serien-Umsetzer-Modul</li> </ul> | 51<br>51<br>52<br>53<br>53<br>54<br>54<br>54<br>55<br>56 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 57                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 58                                                       |

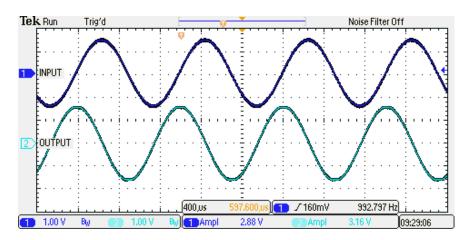

| 6.16. Signalübertragung des linken Kanals im FPGA-Chip, wenn im Signalverarbei-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 58                                                       |

| tungsmodul die Eingangsregister mit den Ausgangsregister kurzgeschlossen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>-</b> 0                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 59<br>60                                                 |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 61                                                       |

| ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 61                                                       |

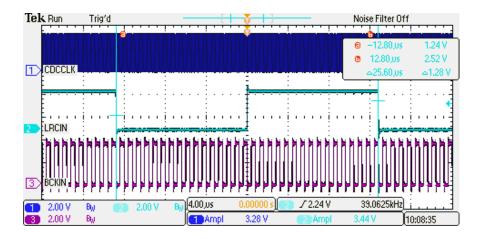

| 6.20. Taktsignale CDCCLK, LRCIN und BCKIN an der Audiocodec-Platine, vergrößert                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          |

| , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 63                                                       |

| <ul><li>6.22. Reaktion der Audiocodec-Platine auf ein Impuls</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 64                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 64                                                       |

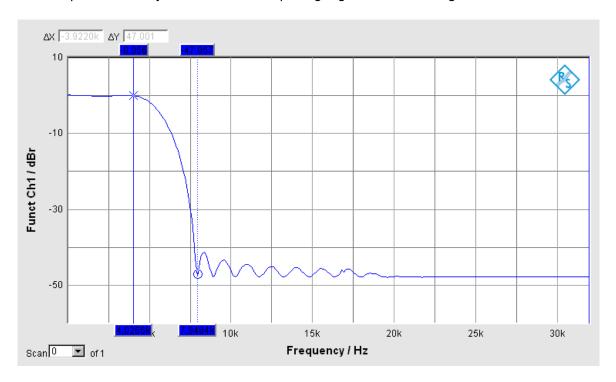

| 6.24. Ausgangssignal bei einer Einspeisung von einem Sinussignal mit einer Ampli-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 65                                                       |

| 7.4. Francisco de FID Ellara                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>67</b>                                                |

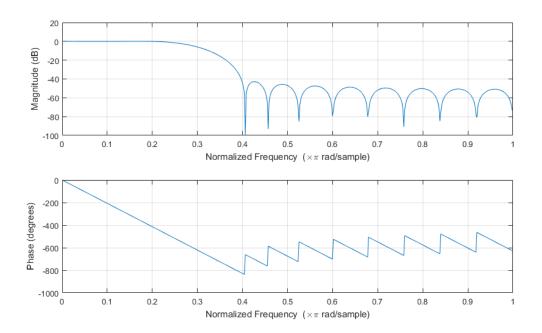

| 1 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 67<br>68                                                 |

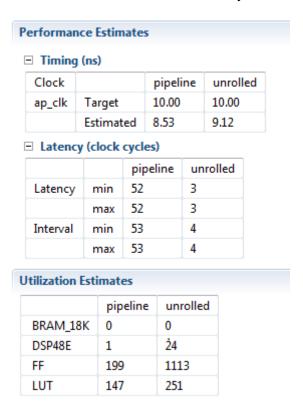

| 7.3. Die berechneten Ressourcen und Takte für die Einstellungen Pipelining-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 00                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 70                                                       |

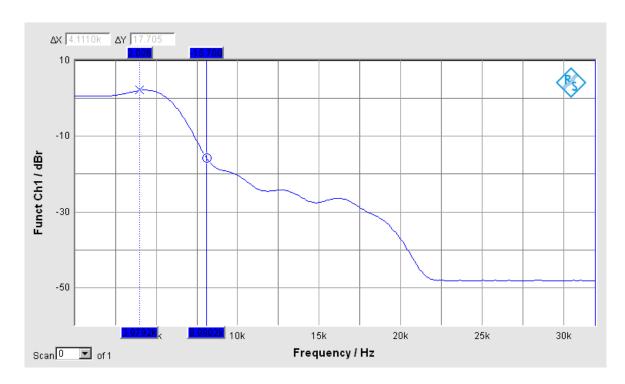

| · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 71                                                       |

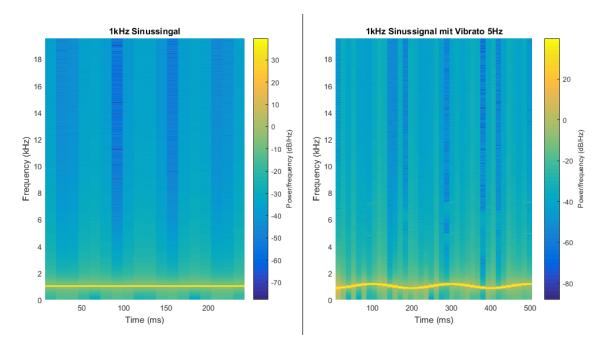

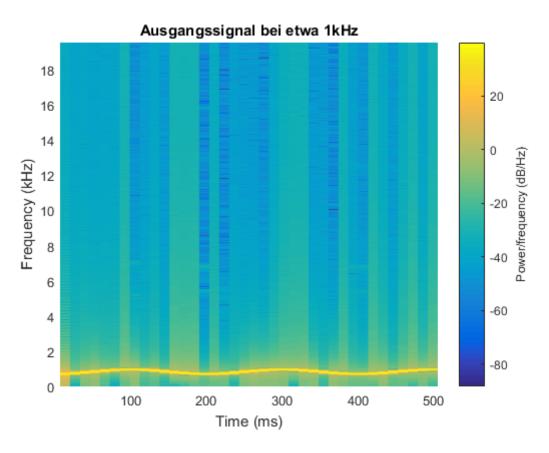

| 7.5. Frequenzspektrum eines 1kHz Sinussignals (links) sowie eines mit 5Hz mo-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 73                                                       |

| Frequenzspektrum eines 1kHz Sinunssignals mit Vivado HLS) Die benötigten Ressourcen für die Synthese des Vibrato VHDL-Codes                                  |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Timing-Diagramm von PCM3006, zeitliche AbhÃngigkeiten der erzeugten Signale zueinander mit spezifischer Dauer, die eingehalten werden mÃ $\frac{1}{4}$ ssen. | 81 |

# 1. Einleitung

Diese Bachelorthesis beschreibt die Entwicklung einer Audiocodec-Platine und Signalverarbeitung auf einem FPGA mit High-Level Synthese. In diesem ersten Kapitel wird die Motivation der Arbeit erläutert. Als dann wird kurz den Inhalt der nachfolgenden Kapitel erläutert.

## 1.1. Motivation

Im Zeitalter der Digitalisierung wird die Signalverarbeitung auf der digitalen Ebene immer wichtiger. Jedoch liegen viele Signale in analoger Form vor und die Sinne des Menschen nehmen die Umwelt analog wahr. Die Verbindung der analogen und digitalen Welt wird mit hochwertigen Analog-Digital und Digital-Analog-Umsetzer ermöglicht. Der Mensch verfügt über fünf Sinne; Riechen, Schmecken, Fühlen, Sehen und Hören. Im speziellen das Gehör nimmt die Umgebung durch Schall war. Um den analogen Schall zu digitalisieren wird ein Audiocodec verwendet. Field Programmable Gate Arrays, kurz FPGA, sind Hardware, die sich programmieren, bzw. sich Konfigurieren lassen und somit anders als die Hardware, bei der die Funktionen zum größten Teil festgestellt ist. Mit FPGAs können sich von simplen Funktion, bis zu komplexen Konstrukten konfigurieren lassen. Dabei verdrängt der FPGA zunehmend mehr den klassischen Prozessors[5][6][7].

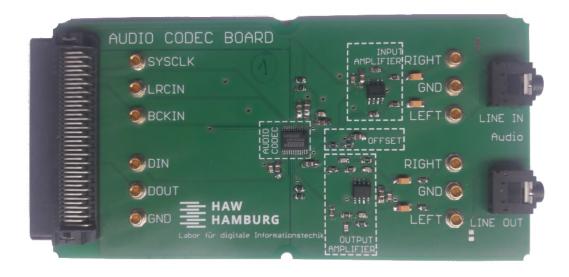

Mit dieser Arbeit soll das Digitaltechnik Labor der Fakultät der Technik und Informatik mit einer Platine erweitert werden. Die Platine soll modular an das bestehende ModSys-Baseboard angepasst werden, sodass die zu entwickelnde Platine nahtlos an das ModSys-Baseboard angebracht werden kann.

Die zu entwickelnde Audiocodec-Platine soll analoge Audiosignale ins Digitale umgesetzt, digital Verarbeitet und zum Schluss ins analoge umgesetzt und ausgegeben werden. Die Platine soll im Digitaltechnik-Labor in Einsatz kommen. Die digitale Signalverarbeitung soll über einen FPGA erfolgen.

1. Einleitung 14

# 1.2. Kapitelübersicht

Nachdem dieses Kapitel die Motivation aufgezeigt hat, beschreibt das zweite Kapitel einige Grundlagen, die für die Bearbeitung dieser Arbeit für notwendig erachtet wurden. Die vorliegende Arbeit ist in sieben Kapitel unterteilt. Im Folgenden werden die Inhalte erläutert.

In Kapitel 1 wird die Motivation aufgezeigt. Weiterhin wird das Ziel dieser Arbeit beschrieben.

In Kapitel 2 werden erforderliche Grundlagen behandelt. Im Einzelnen wird einige Grundlagen zur Tontechnik beschrieben. Des Weiteren werden analoge Schaltungen zur Verstärkung von Signalen beschrieben. Weiterhin wird das im Labor verwendete ModSys-Baseboard 2 erläutert. Anschließend werden digitale Grundschaltungen in VHDL behandelt. Zum Schluss werden zwei Audioeffekte vorgestellt.

In Kapitel 3 werden die Anforderungen an die Arbeit analysiert. Dabei werden die Anforderungen in vier Unterkapitel geteilt. Zuerst werden die Anforderungen an den Audiocodec, dann an die Platine, anschließend an das VHDL-Modell und zum Schluss an den Audioeffekt gestellt.

In Kapitel 4 werden einzelne Konzepte entwickelt. Als erstes wird das Gesamtsystem betrachtet. Anschließend wird ein der Audiocodec ausgewählt und einige Eigenschaften aufgezählt. In Anschluss werden die Konzepte für die Platine entwickelt. Anschließend wird die Konzepte für das VHDL-Grundstruktur behandelt. Zum Schluss wird das Konzept für die Entwicklung von den Audioeffekten beschrieben.

In Kapitel 5 wird die analoge Schaltung entworfen und eine passende Platine entwickelt. Im Anschluss wird die Platine auf ihre Funktionalität getestet.

In Kapitel 6 wird das VHDL-Modell erklärt und entwickelt. Anschließend wird das VHDL-Modell auf dem FPGA mit dem Audiocodec-Board evaluiert.

In Kapitel 7 wird als erstes ein FIR-Filter in VHDL entworfen und getestet. Anschließend wird der selbe FIR-Filter mit dem Software Vivado HLS (High Level Synthesis) entworfen und ausgewertet. Zum Schluss wird ein Audioeffekt mit MATLAB entwickelt, dann in Vivado HLS übertragen und schließlich in VHDL synthetisiert und getestet.

In Kapitel 8 erfolgt schließlich die Zusammenfassung der Arbeit.

In diesem Kapitel werden einige Grundlagen behandelt. Diese werden im Laufe der Arbeit zum Tragen kommen. Als Erstes wird allgemein über das menschliche Gehör und die Tontechnik geschrieben. Danach wird der Operationsverstärker und die beiden Grundbetriebsarten Nicht-Invertierend und Invertierend, sowie die Spezielle Filterschaltung Multiple-Feedback erläutert. Danach wird das im Labor genutzte FPGA-Chip und das FPGA-Board beschrieben. Anschließend werden einige Digitale Schaltungen erklärt. Zum Schluss werden Anwendungen zur Signalverarbeitung der FIR-Filter und der Vibrato-Effekt erklärt.

# 2.1. Bezugspegel in der Tontechnik

In der Tontechnik werden Audiosignalpegel in zwei Arten dargestellt, in dBu und dbV. Die Skalierung ist dieselbe nur der Bezugspunkt ist unterschiedlich. Dem dBu liegt die alte Kommunikationstechnik zur Grunde. Hierbei wird die Spannung an einem 600 Ohm Widerstand die 1 mW effektiv umgesetzt wird als Bezugspunkt gewählt. Beim dBV wird 1 V effektiv als Bezugsspannung gewählt. Die Umrechnung beträgt dBV = 1.29 dBu. In der Anwendung werden verschiedene Pegel für verschiedene Bereiche verwendet. Die Anwendungen werden in zwei Kategorien unterteilt, professionell und Verbraucher Anwendung. Die Pegel bei professionellen Anwendungen sind höher als die der Privatgebrauch. So verwendet das ARD Studio einen Pegel von 6dBu (1.55 V effektiv) und in den Studios in den Vereinigten Staaten 4 dBu (1.228 V effektiv), während im Heimtechnik der Pegel von -10 dBV (0.316 V effektiv) angegeben werden. Der Heimtechnik-Pegel ist jedoch in der Anwendung nicht maßgebend. Beispielsweise werden bei vielen Soundkarten werden eine Spannung von +/-0.7 V angegeben. Jedoch ist das auch nicht der Standard und kann abweichen [19].

# 2.2. Einfacher Verstärker

Mittels eines Operationsverstärkers kann man einen einfachen Verstärker dimensionieren. Man kann den Operationsverstärker in zwei Grundschaltungen beschalten, in einem Invertierenden und ein Nicht-Invertierenden Schaltung. In dieser Sektion werden beide vorgestellt.

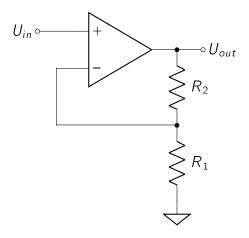

#### 2.2.1. Nicht-Inventierendes Betrieb

Bei der Abbildung 2.1 handelt es sich um einen Nicht-Invertierender Verstärkerschaltung, auch Spannungsfolger genannt.

Abbildung 2.1.: Nicht-Invertierende Grundschaltung mit einem Operationsverstärker

Der positive Eingang des Operationsverstärkers wird mit der Eingangsspannung  $U_{in}$  verbunden. Die Widerstände  $R_1$  und  $R_2$  befinden sich in Reihe an der Ausgangsspannung  $U_{out}$ . Der negative Eingang des Operationsverstärkers wird zwischen den Widerständen verbunden. Der Operationsverstärker verstärkt den Eingangsspannung  $U_{in}$  um die Verstärkung G. Allgemein kann man sagen, dass die Verstärkung das Verhältnis von der Ausgangs- zur Eingangsspannung[8]:

$$G = \frac{U_{out}}{U_{in}} \tag{2.1}$$

Durch die Rückkopplung über die Widerstände  $R_2$  und  $R_1$  kann die Gleichung zu[8]

$$G = \frac{R_2 + R_1}{R_1} \tag{2.2}$$

umgestellt werden. Dadurch kann die Verstärkung individuell über die Widerstände verändert werden[8].

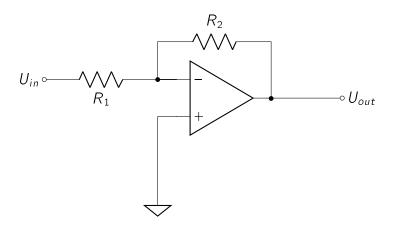

## 2.2.2. Inventierendes Betrieb

In der Abbildung 2.2 ist ein Invertierender Verstärker zusehen. Auch hierbei handelt es sich um einen Operationsverstärker. Das Eingangssignal wird über den Widerstand  $R_1$  an den

negativen Eingang des Operationsverstärkers verbunden. Das Ausgangssignal wird über den Widerstand  $R_2$  an den negativen Eingang des Operationsverstärkers verbunden. Zunächst wird der positive Eingang des Operationsverstärkers mit der Masse verbunden[8]. Die Verstärkung beträgt dann nach der Gleichung 2.1

Abbildung 2.2.: Invertierende Grundschaltung mit einem Operationsverstärker

$$G = -\frac{R_2}{R_1} {(2.3)}$$

Die Verstärkung ist immer negativ zum Eingang[8].

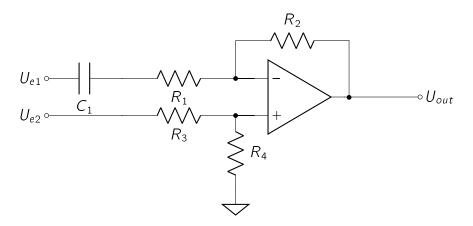

## 2.2.3. Erweiterte Differenzverstärker

Der Differenzverstärker ist eine Schaltung mit einem Operationsverstärker. Die einfache Differenzverstärkerschaltung besitzt keinen Kondensator  $\mathcal{C}_1$ . Der Name kommt daher, dass der einfache Verstärker bei gleich gewählten Widerständen eine Ausgangsspannung von der Differenz vom positiven zur negativen Eingangsspannung des Operationsverstärker einstellt[8].

Für die Gesamtverstärkung für den erweiterten Verstärker wird die Verstärkungen für die einzelnen Eingänge separat betrachtet. Dazu wird der andere Eingang gegen Masse geschaltet[8].

Als erstes wird  $U_{e1}$  auf Masse gelegt. Man erhält einen Nicht-Invertierender Verstärker mit einem Spannungsteiler am positiven Eingang des Operationsverstärkers. An dem negativen Eingang wird die Ausgangsspannung über den Widerstand  $R_2$  zurück gekoppelt. Zusätzlich ist der negative Eingang mit über den Widerstand  $R_1$  und dem Kondensator  $C_1$  gegen Masse verbunden. Die Verstärkung für diesen Fall beträgt

Abbildung 2.3.: Differenzverstärkerschaltung mit einem Operationsverstärker und einem Kondensator am negativen Eingang

$$U_a(j\omega) = \frac{R_4}{R_3 \cdot R_4} \cdot (j\omega C_1(R_1 + R_2) + 1) \cdot \frac{1}{j\omega R_1 C_1 + 1} \cdot U_{e2}(j\omega)$$

(2.4)

Durch den Kondensator wird die Verstärkung Frequenzabhängig. Unter Betrachtung der Gleichung 2.4 wird deutlich, dass diese Schaltung ein Hochpass verhalten zeigt. Läuft die Frequenz gegen Null, stellt sich eine Verstärkung von

$$G_{\omega=0} = \frac{R_4}{R_3 + R_4}. (2.5)$$

R4/R3+R4. Steigt die Frequenz gegen Unendlich verhält sich dieser Verstärker wie ein nicht inventierender Verstärker mit dem Verstärkungsfaktor

$$G_{j\to\infty} = \frac{R_4}{R_3 + R_4} + \frac{R_1 + R_2}{R_1}. (2.6)$$

Das System ist somit Stabil und artet nicht bei einer endlichen Verstärkung.

Als nächstes wird  $U_{e2}$  auf Masse gelegt. Man erhält ein Invertierender Verstärker. Der positive Eingang liegt über den Widerständen  $R_3$  und  $R_4$  an der Masse. Einfachheitshalber werden diese Widerstände weggelassen. Der Kondensator  $C_1$  und der Widerstand  $R_1$  ist mit dem negativen Eingang verbunden. Der Ausgang ist über  $R_2$  zum negativen Eingang zurück gekoppelt. Die Verstärkung beträgt somit

$$U_a(j\omega) = -j\omega R_2 C_1 \cdot \frac{1}{1 + i\omega R_1 C_1} \cdot U_{e1}(j\omega)$$

(2.7)

Anhand der Gleichung 2.7 kann man erkennen, dass sich hierbei wieder um ein Hochpass ähnliches Verhalten vorzeigt. Bei Frequenzen gegen Null stellt sich eine Verstärkung von Eins ein. Wenn die Frequenzen gegen Unendlich steigen, stellt sich die Verstärkung bei -R2/R1 ein. Auch diese Schaltung ist Stabil.

Die gesamte Verstärkung des Differenzverstärkers ist die Summe der Teilverstärkungen

$$U_{a}(j\omega) = \frac{R_{4}}{R_{3} \cdot R_{4}} \cdot (j\omega C_{1}(R_{1} + R_{2}) + 1) \cdot \frac{1}{j\omega R_{1}C_{1} + 1} \cdot U_{e2}(j\omega) - j\omega R_{2}C_{1} \cdot \frac{1}{1 + j\omega R_{1}C_{1}} \cdot U_{e1}(j\omega)$$

(2.8)

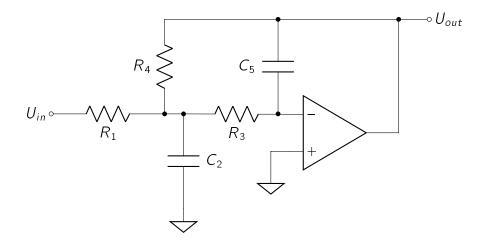

# 2.2.4. Multiple Feedback Filter

Beim Multiple Feedback-Filter handelt es sich um einen aktiven Filter zweiter Ordnung. Dazu wird ein Operationsverstärker als ein Integrator geschaltet. Der Filter invertiert das Eingangssignal, also hat dieser Filter eine Phasenverschiebung von 180° [8].

Abbildung 2.4.: Grundschaltung eines Multiple-Feedback-Filters

In der Abbildung 2.4 ist ein Multiple-Feedback-Filter zu sehen. Der Filter besteht aus drei Widerständen und zwei Kondensatoren. Das Eingangssignal ist über R1 und R3 mit dem negativen Eingang des Operationsverstärkers verbunden. Das Ausgangssignal ist über C5 an den negativen Eingang des Operationsverstärkers zurück gekoppelt. Eine zweite Rückkopplung des Ausgangssignals ist über R4. Die zwei Rückkopplungen ist der Namensgeber dieses Filters [8]. Die Übertragungsfunktion für diesen Filter ist

$$\frac{U_{out}}{U_{in}} = \frac{-H\frac{1}{R_1R_2C_2C_5}}{s^2 + s\frac{1}{R_1}(\frac{1}{R_1} + \frac{1}{R_3} + \frac{1}{R_4}) + \frac{1}{R_3R_4C_2C_5}}$$

(2.9)

Hierbei ist H der Verstärkungsfaktor. [8]

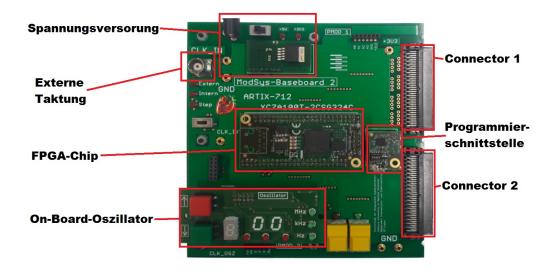

# 2.3. ModSys-Baseboard 2

Im Labor wird ein Modulsystem, das ModSys, verwendet. Er besteht aus einem Hauptboard, ModSys Mainboard genannt, sowie verschiedenen Modulen, die über Steckverbinder verbunden werden [9]. Im speziellen wird das ModSys-Baseboard 2 mit dem ARTIX-712 verwendet. Das Mainboard wird über einen externen Netzteil von 5V versorgt. Mittels Spannungsregler wird 3.3V erzeugt, mit der diverse Bausteine mit Spannung versorgt werden, wie der Oszillator und das FPGA Chip, sowie die Bereitstellung an den Steckverbindungen, auch Connector genannt, für die Pheripherimodule. Das Mainboard besitzt einen On-Board Oszillator mit der das FPGA Chip getaktet werden kann. Zudem besitzt das Board die Möglichkeit extern, sowie Manuell getaktet zu werden. Dieser wird über einen Schiebeschalter eingestellt. Das On-Board Oszillator kann Manuell über zwei Taster von einem Hertz bis 80 MHz eingestellt werden.

Abbildung 2.5.: ModSys-Baseboard 2

Der FPGA Chip befindet sich auf einer Aufsteckplatine von der Firma "Trenz Electronic". Beim FPAG-Chip handelt es sich um ARTIX-7 XC7A100T mit 210 I/O Pins [10]. Die Auf-

steckplatine hat drei zwei 50er Steckleisten für die I/O Pins sowie eine 12er Steckleiste für den JTAG/UART Schnittstelle [11]. Die Aufsteckplatine wird mit 3.3V versorgt.

Der ModSys-Baseboard 2 verfügt über zwei Connectoren. Jeder Connector besteht aus 80 Pins. An je sechs Pins liegen 3.3V für die Versorgung der Peripherimodule, sowie Masseleitung. Zusätzlich sind 32 Pins des Connectors mit dem FPGA I/O Pins verbunden. Diese 32 Pins wurden zu je 8 Pins gebündelt und somit zu 4 Ports zusammengefasst.

# 2.4. VHDL Grundschaltungen

In diesem Unterkapitel werden die digitalen Grundschaltungen im FPGA besprochen. Als erstes wird ein digitales Flipflop vorgestellt. Danach wird der Zähler und Taktteiler beschrieben. Anschließend werden die Schieberegister erklärt. Zum Schluss wird die Impulsverkürzung erläutert.

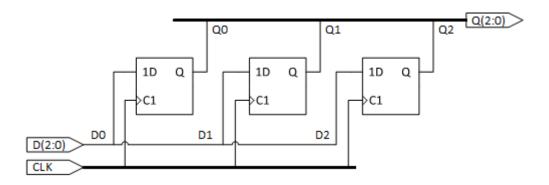

# 2.4.1. Flipflops

Ein Flipflop ist in der Digitaltechnik ein flanken gesteuertes Speicherelement. Er besteht aus einem Taktsignal C1, einem Eingangsdatensignal 1D und einem Ausgangsdatensignal Q. Nur bei einer vorgegebenen Pegeländerung an C1 wird das Eingangssignal an Q weitergereicht. Hierbei signalisiert die Nummer bei 1D die Abhängigkeit zu C1. Es werden in der Regel auch mehrere Speicherelemente zu einem Speicherblock zusammengefasst und wird Register genannt. Es gibt mehrere Arten von Flipflops wie den RS-Flipflop, während der D-Flipflop die gängigste ist [2].

Abbildung 2.6.: Ein einzelner D-Flipflop

In der Abbildung 2.6 sieht man einen D-Flipflop. Der Eingang C1 ist der Takteingang und 1D der Dateneingang und der Ausgang Q ist der Datenausgang. Die Zahl bei C1 gibt die Nummer der Takt an und die Zahl bei 1D zeigt die Abhängigkeit zur Takt C1.

In der Abbildung 2.7 sind drei D-Flipflops zu sehen. Die Eingänge D1 und die Ausgänge Q sind zu einem Bus zusammengefasst. Bei einem Takt wird der Bus gelesen.

Abbildung 2.7.: Ein Speicherblock von drei D-Flipflops (Register)

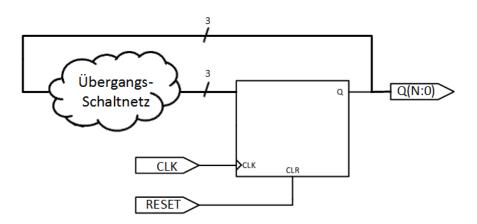

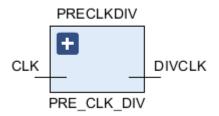

## 2.4.2. Zähler/ Taktteiler

In der Digitaltechnik ist ein Zähler ein Baustein, welcher fortlaufend eine Eins aufaddiert (Vorwärtszähler) oder subtrahiert (Rückwärtszähler) wird. Dabei wird er auch mod-n-Zähler genannt, wobei das n für die Anzahl der Zahlwerte steht. Diese Bezeichnung ist eine Ableitung aus der modulo-Operation der Mathematik, bei der das Ergebnis ein Zahlenwert von 0 bis n-1 ist. Des weiterem wird unter synchronen und asynchronen Zähler unterschieden. Allgemein werden Zähler zum Zählen von Ereignissen und das Herabsetzten einer Taktfrequenz verwendet. Zudem lassen sich durch Zähler Automaten steuern. Im Folgenden wird nur der synchrone Vorwärtszähler beschrieben.

Abbildung 2.8.: Schaltbild eines N-Bit Zählers[2]

Ein Zähler besteht aus einem oder mehreren digitalen Flipflops. Die Anzahl der Flipflops lässt sich durch log2(n) berechnen, wobei das Ergebnis bei einer Fließkommazahl aufgerundet wird. Bei Erreichen der Grenze n-1 wird entsteht ein Überlauf und der Zähler wird zurückgesetzt. Dies geschieht im Übergangsschaltnetz.

Bei der Herabsetzung eines Taktes ist es manchmal wünschenswert, dass der neue Takt synchron zur Taktdomäne ist und dass der neue Takt genauso lange High als auch Low ist (Tastgrad von 50%). Der Tastgrad von 50% wird dadurch erreicht, dass n eine grade Zahl sein muss. Im Ausgangsschaltnetz wird von 0 bis n/2-1 auf Low gesetzt und von n bis n-1 auf High gesetzt.

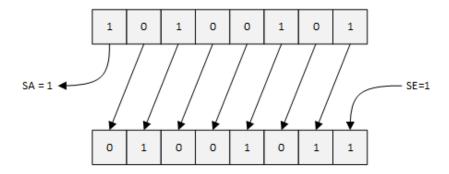

# 2.4.3. Schieberegister

In der Digitaltechnik ist ein Schieberegister eine Schaltung von mehreren hintereinandergeschalteten Flipflops. Sie teilen einen gemeinsamen Takt. Mit jedem Takt wird der Register nach links oder auch nach rechts geschoben. Hierbei heißt links Schiebung, dass die Werte des Registers von LSB in Richtung MSB geschoben werden. Rechts Schiebung dahingegen werden die Werte vom MSB in Richtung MSB geschoben.

Abbildung 2.9.: Ein linksschiebe Register[2]

Ein Schieberegister ist ein Register, welches sich schieben lässt. Beim Schieben werden die Inhalte der Flipflops an das nachfolgende Flipflop übergeben. Bei einem Linksschieber wird der niedrigste Flipflop mit einem Schiebeeingangsbit SE gefüllt und der höchste Datenbit wird auf den Ausgangsbit verschoben (Abbildung 2.9)[2].

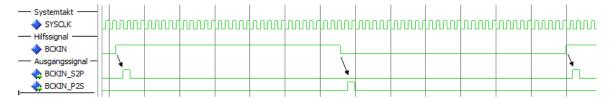

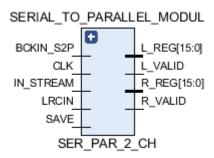

## Serien-Parallel-Umsetzer

Ein Serien-Parallel-Umsetzer ist ein Linksschieberegister, dass ein Eingangswert einliest, ihn zu einem Array bildet und das Array gebündelt ausgibt.

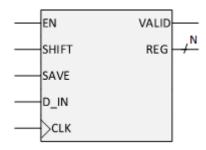

Dieser Baustein wird mit dem Systemtakt SYSCLK betrieben. Der EN-Signal wird für die Aktivierung des Linksschiebers benötigt. Das SHIFT-Signal wird für das Schieben der Register benötigt. Ist SHIFT während eines SYSCLK Flanke High, so wird der Schieberegister einmal nach links geschoben und das niedrigste Flipflop wird mit dem Wert von D\_IN überschieben.

Abbildung 2.10.: Blockschaltbild eines Serien-Parallel-Umsetzers

Beim Anliegen des SAVE-Signals wird bei dem Takt der Schieberegister dem Ausgangsregister übergeben und für eine Taktlänge wird das VALID-Signal auf High geändert.

#### Parallel-Serien-Umsetzer

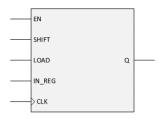

Ein Parallel-Serien-Umsetzer ist ein Schieberegister, welcher ein Register einließt und ihn nacheinander ausgibt.

Abbildung 2.11.: Blockschaltbild eines Parallel-Serien-Umsetzers

Der Parallel-Serien-Umsetzer wird mit dem Systemtakt SYSCLK betrieben. Der EN-Signal aktiviert den Schieberegister. Bei einem aktiven LOAD-Signal wird der IN\_REG in den Schieberegister eingelesen. Solange SHIFT auf High ist, wird bei jeder steigender Flanke des SYSCLK das höchste Flipflop des Registers an Q übergeben und der Register nach links geschoben. Der Register wird mit Null nachgefüllt.

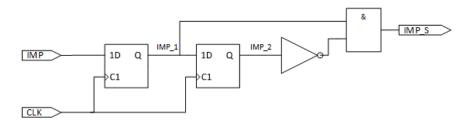

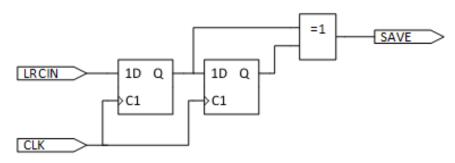

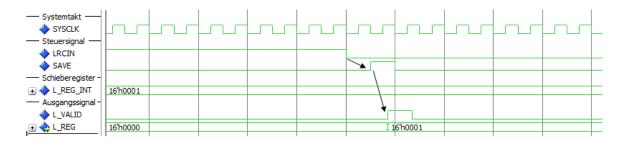

# 2.4.4. Impulsverkürzung

Die Impulsverkürzung ist eine digitale Schaltung zur Verkürzung eines Impulssignals auf die Taktzeit. Das Eingangssignal soll auf die Länge eines Systemtakts verkürzt werden. Dazu werden zwei Flipflops aneinandergereiht. Das Ausgangssignal des ersten Flipflops und das negierte Ausgangssignal des zweiten Flipflops werden an einen UND-Gatter geführt.

Das daraus resultierende Signal ist das verkürzte Eingangimpuls. Diese Schaltung wird zur Synchronisation zweier Systeme mit verschiedenen Taktdomänen und zur Detektierung von steigenden Signalflanken verwendet[2].

Abbildung 2.12.: Digitale Schaltung einer Impulsverkürzung[2]

Wird IMP1 statt IMP2 negiert und an ein UND-Gatter geführt, wird die fallende Flanke detektiert.

# 2.5. Digitale Filter und Zeitvariante Verzögerungen

In dieser Sektion wird der FIR-Filter beschrieben, sowie v Vibrato-Effekt beschrieben.

## 2.5.1. FIR-Filter

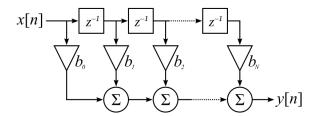

Der Finite Impulse Response Filter, kurz FIR-Filter, ist ein digitales Filter, der mit dem aktuellen Eingangssignalabtastwert x[n] und einer bestimmten Anzahl N von vorherigen Eingangswerten x[n-k] den Ausgangswert berechnen lassen kann. Allgemein lässt sich der FIR-Filter im Zeitbereich durch die folgende Differenzialgleichung beschrieben.

$$y[n] = \sum_{k=0}^{N} c_k \cdot x[n-k]$$

(2.10)

Zur Bestimmung der Ausgangswerte werden die Eingangswerte mit den Koeffizienten  $c_k$  gewichtet. Die Anzahl der zu speichernden Eingangswerte bestimmt die Filterordnung N. Die Filterlänge L gibt die Anzahl der Summanden an (L=N+1) und beschriebt, wie lang die Impulsantwort ist. Da der Filter keine Rückkopplung hat, kann sich der Filter nicht selbstständig zum Schwingung angeregt werden und ist stabil. Die Koeffizienten geben die Art des Filters wieder (Tiefpass, Hochpass) und die Stärke des Dämpfung an[12][4].

Die Gleichung 2.10 wird in den z-Bereich transformiert, um das transiente Verhalten des Filters auszuwerten. Dazu wird die Übertragungsfunktion H(z) ermittelt[12][4].

$$Y(z) = \sum_{k=0}^{N} b_k \cdot z^{-k} X(z) = H(z) \cdot X(z)$$

(2.11)

In Gleichung 2.11 ist  $z^{-k} = e^{j2\pi kfT}$  die Zeitverschiebungsoperator. Er verursacht eine zeitliche Rechtsverschiebung um kT Abtastintervalle[12][4]. Somit ergibt sich

$$H(z) = b_0 z^0 + b_1 z^{-1} + b_2 z - 2 + \dots + b_{N-1} z^{-(N-1)} + b_N z^{-N}$$

(2.12)

Aus H(z) ergibt sich das folgende Blockschaltbild

Abbildung 2.13.: Blockschaltbild eines FIR-Filters[3]

Diese Form wird auch die Direktform genannt.

## 2.5.2. Vibrato-Audioeffekt

Vibrato ist ein Audioeffet basierend auf die Zeitvarianz. Dieser wird erzeugt, indem das Audiosignal mit einer variablen Zeit periodisch verzögert ausgegeben wird. Dadurch wirkt das Ausgangssignal, als ob es schwingen würde. Vibrato wird wie folgt beschrieben

$$y(n) = x(n - M) \tag{2.13}$$

In z-Bereich transformiert ergibt

$$Y(z) = X(z) \cdot z^{-M} \tag{2.14}$$

Der Ausgangssignalwert wird aus dem M-fach verzögerten Eingangssignalwert gebildet. Für den besseren Klang wird ein Hilfsteiler frac eingeführt, der einen Werte zwischen 0 <=

frac < 1 annehmen kann. Dadurch lässt sich die Verzögerung besser einstellen und hat den Effekt, dass der Klang des Audiosignals nicht verzerrt wird[4].

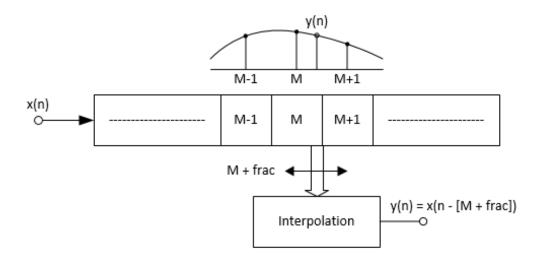

Abbildung 2.14.: Verzögerungskette mit Interpolation[4]

In der Abbildung 2.14 ist eine Verzögerungskette zu sehen, bei der x(n) der Eingangswert und y(n) der Ausgangswert ist. Der neue Eingangswert wird stets an den Anfang gespeichert und die Inhalte der nachfolgenden Werte werden in weiter gereicht. Der letzte Wert fällt aus der Kette raus. Ein Zeiger M zeigt auf die Verzögerungskette. Dieser Zeiger schwingt mit einer niederfrequent über die Verzögerungskette hin und her. Das Kettenglied, auf dem der Zeiger M zeigt, wird an den Ausgang übergeben[4].

Die Position des Zeigers auf die Verzögerungskette wird rechnerisch bestimmt, so zum Beispiel mit Hilfe der Sinuskurve. Die Position des Zeigers liegt meistens zwischen zwei Verzögerungsglidern. Dieser wird mit dem Hilfsteiler *frac* erfasst[4].

$$y(n) = x(n - [M + frac])$$

(2.15)

Mittels frac kann der Ausgangssignalwert durch lineare Interpolation bestimmt werden [4].

$$y(n) = x(n - [M+1]) \cdot frac + x(n - M) \cdot (1 - frac)$$

(2.16)

Weitere Interpolationsverfahren können in [4] auf Seite 74 nachgelesen werden.

Dieser Effekt wird oft bei Seiteninstrumenten angewendet um einen vibrierenden Ton zu erzeugen.

# 3. Anforderungsanalyse

Das Ziel dieses Kapitels ist es, Anforderungen für ein digitales System zur Audioverarbeitung, welches aus einer Platine zur Beschaltung eines Audiocodecs, sowie eines digitalen Systems, implementiert auf einem FPGA, das den Codec digital ansteuert und einen Audioeffekt implementiert. Dieser Audioeffekt soll als Hardware mit Hilfe der High-Level Synthese Software von Xilinx (kurz HLS) implementiert werden.

# 3.1. Audiocodec

Zu Beginn der Arbeit wurden Anforderungen zur Auswahl des Audiocodecs zusammengetragen.

Der Mensch nimmt akustische Signale in Form von Schallwellen über das Gehör wahr. Dabei kann er Schallwellen mit einer Frequenz von 16 Hz bis ca. 20 kHz wahrnehmen. Tiefe Frequenzen werden als Brummen und hohe als schriller Ton wahrgenommen. Die Sprache liegt im Frequenzbereich 0.5 bis 2 kHz [13]. Der Audiocodec soll mindestens 16 kHz bearbeiten können.

Der Audiocodec soll mindestens einen Kanal, d. h. Mono, bearbeiten können. Jedoch wäre es wünschenswert, wenn er zwei Kanäle, also Stereo, bearbeiten könnte.

Die Konfiguration des Audiocodecs soll für die Studierenden einfach gehalten werden. Die Einstellung des Audiocodecs soll nicht mit einem Mikrocontroller oder dem FPGA erfolgen, stattdessen soll er eine feste Voreinstellung besitzen oder durch eine elektrische Schaltung konfigurierbar sein.

Die serielle Datenübertragung zwischen dem FPGA und dem Audiocodec soll ebenfalls einfach sein. Die serielle Schnittstelle soll standardisiert und geläufig sein, wie z. B. I2C oder I2S.

Die Bit-Auflösung gibt die Audioqualität wieder. Je geringer diese ist, desto verrauschter hört sich anschließend das Audiosignal an. Typische Auflösungen sind 8, 12, 16, 24 und 36 Bits. Die Bit-Auflösung des analogen Audiosignals sollte mindesten 16 Bit betragen.

29

Die Audiocodec-Bausteine gibt es in diversen Bauformen, so zum Beispiel in Ball Grid Array (BGA, dt. Kugelgitteranordnung), Quad Flat No Leads (QFN), Small Outline (SO) etc. Um Kosten zu sparen, sollten Bauformen, die mehr als zweilagige Platinen erfordern, wie BGA, oder die nur schwer mit der Hand zu löten sind, wie QFN, vermieden werden.

Der Audiocodec sollte vom Hersteller gut dokumentiert sein. Zusätzlich wäre es wünschenswert, wenn schon Evaluationsboards von Hersteller oder andere öffentlich zugängliche Projekte beim Audiocodec auffindbar wären.

Die Anforderung zusammengefasst

- Abtastrate mindestens 32 kHz

- mindestens ein Kanal (Mono), Stereo-Betrieb wäre wünschenswert

- wenig bis keine Konfiguration

- serielle Datenübertragung wie I2C, I2S, PCM, PWM, etc.

- Mindestauflösung 16 Bit

- Bauform gut lötbar

- gute Dokumentation oder bestehende Projekte

# 3.2. Platine

Die Platine soll als modulare Schnittstelle zum bestehenden Modsys Board benutzt werden. Die Platinengröße muss dementsprechend den anderen Modulen angepasst werden. Passend zur FPGA-Board-Schnittstelle muss das Codecboard eine Kommunikationsschnittstelle haben. Für die zu verarbeitende Audiosignale, die aus einem Computer oder Smartphone kommen, sollten Standardklinkenbuchsen vorhanden sein. Zusätzlich zu diesen sollen die drei Signale linker Kanal, rechter Kanal und Masse über 2mm-Buchsen mit dem Oszilloskop beobachtbar sein. Die Audiosignale sind Line-Level-Pegel. Die Ausgangssignale sollen auch Line-Level-Pegel aufweisen. Auf alle Signale der digitalen Schnittstelle, die für die Kommunikation zwischen dem Audiocodec und dem FPGA erforderlich sind, sollte ebenfalls über 2mm-Buchsen zugreifbar sein. Zudem soll die Audiocodec-Platine Line-Pegel voll auflösen. Des Weiteren bestimmt der ausgewählte Codec weitere Anforderungen sowie die Gestaltung der Leiterbahnplanung. Zusätzlich wird das Buch "Linear Circuit Design Handbook"beim Designen der Platine zu Hilfe genommen.

# 3.3. VHDL-Modell zur Codecansteuerung

Der FPGA ist das Herzstück der Anwendung, da die Studierenden hier später die Ansteuerung des Audiocodecs und die Signalverarbeitung implementieren sollen. Das Kommunikationsmodul erzeugt die digitalen Ansteuersignale für den Audiocodec und die zeitliche Synchronisation und tauscht außerdem die digitalen Daten mit dem Audiocodec aus. Der Steuerpfad und der Datenpfad sollen im VHDL-Code getrennt werden. Der Code soll Herrn Reicherdts Richtlinien entsprechend geschrieben werden.

# 3.4. Audioeffekt mit HLS

Im Rahmen des zu entwickelnden Praktikumsversuchs wird angestrebt, dass langfristig die Studierenden mit dem High-Level-Synthese-Tool (HLS) von Xilinx Erfahrungen sammeln und mit dessen Hilfe einen einfachen Audioeffekt generieren. Der HLS ist eine Software, mit der ein VHDL-Code aus einem C/C++ Code synthetisiert werden kann. Anhand eines einfachen Audioeffektes, der auch leicht in VHDL direkt zu implementieren wäre, sollen zunächst Erfahrungen mit der HLS gesammelt werden und diese mit einer direkten VHDL-Implementierung verglichen werden. Mit diesen Erkenntnissen kann im nächsten Schritt ein zu definierender Audioeffekt realisiert werden. Hierbei gilt, dass dieser möglichst eindrucksvoll, aber im Rahmen eines Praktikumsversuches leicht zu implementieren sein soll.

In diesem Kapitel werden die einzelnen Konzepte entwickelt und beschrieben. Zunächst werden das Gesamtsystem und seine Komponenten in den Blick genommen. Anschließend wird ein Konzept für den Audiocodec und die Platine des Audiocodecs abgeleitet und entwickelt.

# 4.1. Das Gesamtsystem

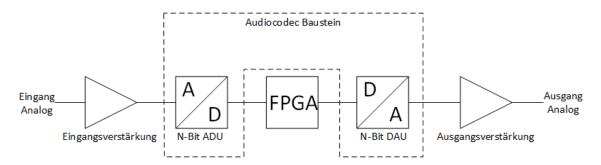

Mit den bekannten Anforderungen aus Kapitel 3 kann ein Konzept für das Gesamtsystem hergestellt werden. Es soll eine Platine entwickelt werden. Dazu gehören der Audiocodec IC und die Zusatzschaltungen für die Stromversorgung sowie die Anpassung der Signalpegel an den Audiocodec.

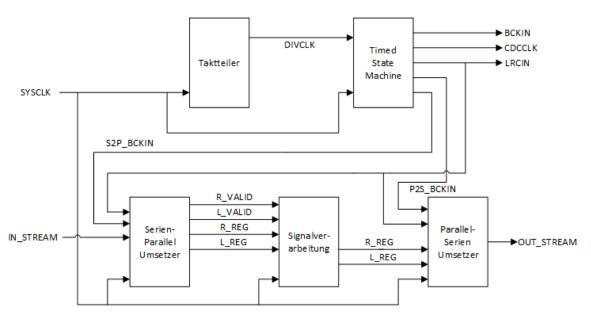

Abbildung 4.1.: Das Signalflussdiagramm für einen Audiokanal

In der Abbildung 4.1 ist das Signalflussdiagramm für das Audiosignal zu sehen. Die analoge Schaltung besteht aus drei Teilen: der analogen Eingangsverstärkerschaltung, dem Audiocodec-Baustein und der Ausgangsverstärkerschaltung. Durch die Schnittstelle wird das Audiocodec-Board mit dem Modsys-Baseboard 2 verbunden. Als erstes wird der Signalpegel des Audiosignals in einer Eingangsverstärkerschaltung an den die Signalpegel des Audiocodec-Bausteins angepasst. Danach wird im Analog-Digital-Umsetzer (ADU) des Audiocodecs das analoge Audiosignal in N-Bits umgewandelt. Alsdann wird das digitale Signal seriell an den FPGA-Chip übertragen. Nach der digitalen Signalverarbeitung im FPGA wird

das N-Bit-Signal wieder zurück an den Audiocodec-Baustein seriell übertragen und mittels eines Digitalen-Analogen-Umsetzers (DAU) wieder in ein analoges Signal umgewandelt. Im Anschluss wird der Signalpegel des analogen Audiosignals wieder zurück angepasst, sodass der Signalpegel wieder mit dem des Eingangssignals übereinstimmt.

# 4.2. Auswahl des Audiocodecs

Anhand der Anforderungen die im Abschnitt 3.1 hergeleitet worden sind, soll ein Audiocodec-Baustein ausgewählt werden. Zuerst werden die Mindestanforderungen betrachtet, um das Portfolio an Audiocodecs zu minimieren und die Suche einfacher zu gestalten. Die Mindestanforderungen sind jene, die zumindest zu erfüllen gilt. Diese sind

- die Abtastrate, mit dem das System arbeitet, ist mindestens 32 kHz,

- die Bit-Auflösung der Audiocodecs ist mindestens 16 Bit und

- das Package soll mit den im Labor zur Verfügung stehenden Mitteln bestückbar sein (kein BGA oder QFN).

Mit diesen Kriterien wurden aus zahlreichen Audiocodecs jeweils ein passender von vier großen Herstellern ausgewählt. Diese sind Folgende:

Analog Devices: AD74111,

• Rohm Integrate: BU26156RFS,

Texas Instruments: PCM3006 und

ST Microelectronic: STA120 und STA020

Für die oben ausgewählten Audiocodecs wurden die Datenblätter ausgewertet und die spezifischen Daten in der unteren Tabelle zusammengetragen.

Tabelle 4.1.: Ausgewählte Audiocodec-Systeme

|                  | AD7411         | BU26156RFS     | PCM3006     | STA020/120  |

|------------------|----------------|----------------|-------------|-------------|

| Abtastrate [kHz] | 8-48           | 4-48           | 4-48        | 4-48        |

| Kanäle           | 1              | 2              | 2           | 1           |

| Bauform          | TSSOP          | HISSOP         | TSSOP       | SOP         |

| Konfiguration    | Programmierbar | Programmierbar | Stand Alone | Stand Alone |

| Audiointerface   | PCM            | PCM            | PCM         | PCM/I2S     |

| Auflösung [Bit]  | 16-24          | 24             | 16          | 16-24       |

Diese Audiocodecs wurden anschließend nach den folgenden Kriterien beurteilt:

- Anzahl der Audiokanäle

- Analoges Interface

- Digitales Interface

- Unterstützung

Alle ausgewählten Audiocodecs können bei einer Abtastrate bis zu 48 kHz betrieben werden, und wie erwünscht haben sie eine Mindestauflösung von 16 Bit. Zudem haben alle die SO (Small Outline) Bauform. Bei SO handelt es sich um eine Surface-Mounted-Device—Bauform (SMD), also eine oberflächenmontierbare Bauform. Die Pins werden flach auf der Oberfläche der Platine, den Pads, gelötet. Die Kommunikation zwischen dem Audiocodec und dem FPGA erfolgt über PCM. Die Konfigurationen müssen bei AD7411 und BU26156RFS über einen Mikrocontroller oder das FPGA eingestellt werden, während bei den anderen beiden die Einstellungen über Spannungspotentiale gesetzt werden können. Alle ausgewählten Audiocodecs können in Mono betrieben werden. BU26156RFS und PCM3006 lassen sich zusätzlich in Stereo betreiben.

Der PCM3006 wurde für die Anwendung als am geeignetsten betrachtet. Außerdem lässt sich die Abtastrate diess Audiocodecs variabel über den Takt einstellen und kann zwei Kanäle verarbeiten. Die Datenübertragung erfolgt über das PCM-Format, und die Auflösung erfolgt auf 16 Bit. Der Audiocodec besitzt Möglichkeiten, die über Pins eingestellt werden können. Dazu wird die Spannung an den Pins entweder auf die Betriebsspannung gezogen oder auf Masse gelegt. Die Bauform des Bausteins ist gut händisch zu löten. Zudem gibt es ein bestehendes Projekt mit diesem Baustein.

Für den Audiocodec spricht weiterhin das einfache Interface. Es können so bereits hardwareseitig die wichtigsten Einstellungen vorgenommen werden und somit der Praktikumsversuch für die späteren Studierenden entlastet werden. Bei den Audiocodecs mit softwarebasierter Konfiguration müssten nach dem Reset Sequenzen von Bitmustern vom FPGA generiert und an den Audiocodec gesendet werden, die bereits zu Anfang des Semesters, in dem die Studierenden den Versuch bearbeiten sollen, Kenntnisse über RAMs und pointerbasierte Zustandsautomaten erfordern. Diese Themen werden jedoch aus didaktischen Gründen erst am Ende des Semesters behandelt. Eine Alternative wäre der Einsatz eines Softcore Mikrocontrollers, der aber noch mehr Knowhow bei den Studierenden erfordert und in der Regel erst auf Niveau der Masterstudiengänge Thema ist.

Die Audioqualität des Audiocodec, z. B. im Hinblick auf Filter und Rauschen (SNR) wurde nicht in die Auswahl einbezogen, da im späteren Praktikumsversuch wegen der einfachen Audioequipments keine besonderen Anforderungen gefragt sind, die nicht bereits ein Standard-Audiocodec erfüllen kann.

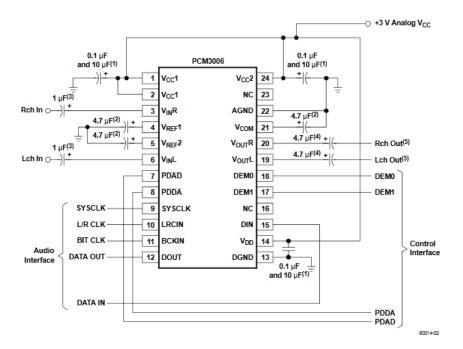

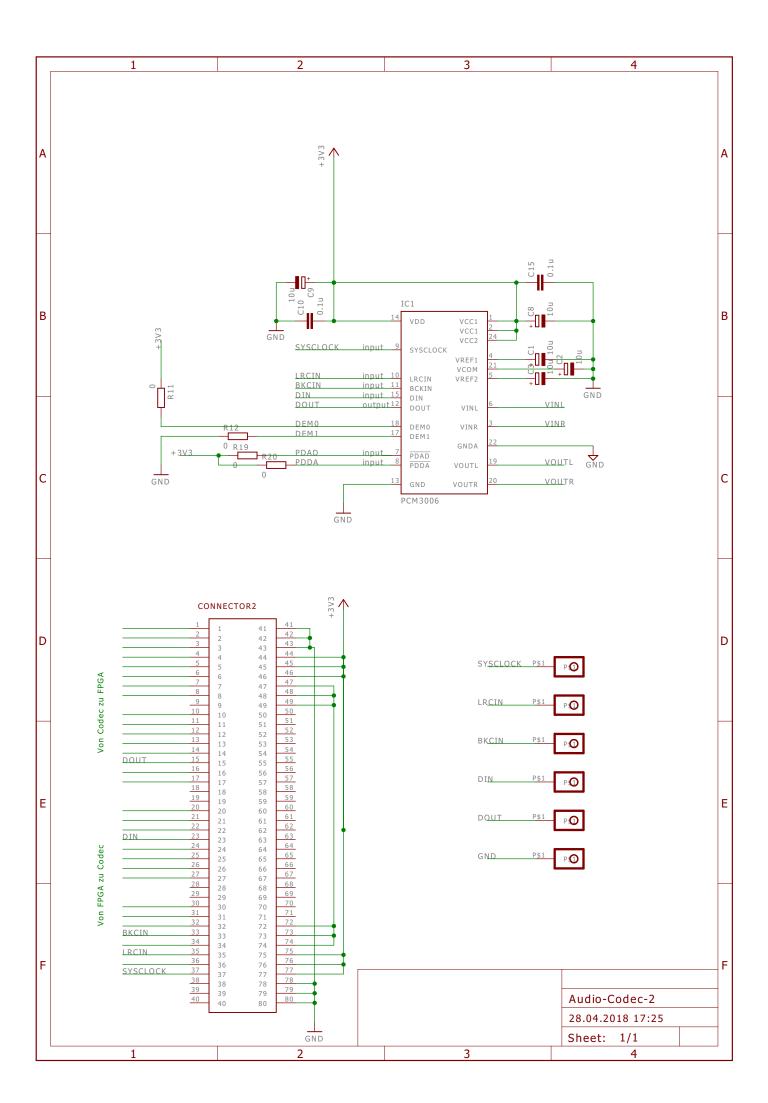

# 4.3. Übersicht über PCM3006 Audiocodec und Schaltungslayout

Im Folgenden werden einige Eigenschaften des PCM3006 vorgestellt, die für das Konzept zum Schaltungslayout die zusätzlichen Anforderungen darstellen.

## **Allgemein**

Der PCM3006 ist ein Audiocodec bestehend aus Analog-Digital-Umsetzer (ADU) und Digital-Analog-Umsetzer (DAU) mit asymmetrischer Signalübertragung. Sowohl der ADU als auch der DAU verwenden für die Umsetzung die Delta-Sigma-Modulation mit 64-facher Überabtastung. Der ADU hat einen Dezimationsfilter und der DAU ein 8-fachen überabtastender Interpolationsfilter. Der DAU hat zusätzlich eine digitale Emphasis-Funktion. Die Abtastfrequenz kann variabel von 4 kHz bis 48 kHz eingestellt und der Betriebstakt variabel in Abhängigkeit von fs auf 256 fs, 384 fs oder 512 fs eingestellt werden. Vier der 24 Pins dienen zur Spannungsversorgung. Der Audiocodec kann in Bereich von 2.7 und 3.6 V betrieben werden[1].

Abbildung 4.2.: Grundschaltung der PCM3006 [1]

## Analoge Audioschnittstelle

Die Kanäle des Stereo Audiosignals werden an die Pins  $V_{in}R$  und  $V_{in}L$  geleitet. Diese werden durch Abblockkondensatoren vom Eingang getrennt. Dadurch werden mögliche Überspannungen am Eingang abgeblockt. Die Pins  $V_{in}R$  und  $V_{in}L$  haben einen Arbeitsbereich von 0.6 Vcc mit einem Offset von 0.5 Vcc. Folglich heißt es für den Audiocodec, wenn er mit 3.3 V betrieben wird, dass das Audiosignal ein Offset von 0.5 Vcc = 1.65 V haben muss und die maximale Amplitude nicht größer als 0.6 Vcc/2 = 0.99 V sein darf. [1].

#### **Control Interface**

Der Control-Interface besteht aus vier Pins PDAD, PDDA, DEM0 und DEM1. Durch das Anlegen eines definierten Spannungspegels an diese Pins lässt sich der PCM3006 konfigurieren. Die definierten Pegel sind zum einen die Betriebsspannung des PCM3006 für den High, sowie die Masse für den Low. Mit den Pins PDAD und PDDA lassen sich der ADU und der DAU ein- und ausschalten. Diese Pins sind low-aktiv. Die Pins DEM0 und DEM1können über den Emphasis-Modus eingestellt werden [1]. Mit der sogenannten Emphasis wird eine Art Rauschunterdrückung beschrieben. Dabei wird das Audiosignal in einem bestimmten Frequenzbereich bei der Aufnahme angehoben und bei der Wiedergabe wieder abgesenkt. Dabei wird darauf geachtet, dass der Frequenzgang linear bleibt [14]. Die Einstellung dieser Control Pins kann sowohl vom FPGA ausgehend erfolgen, als auch durch die Beschaltung an der Platine. Bei der letzteren Variante wäre die Einstellung fix und ließe sich nicht ändern. Bei der ersteren Variante ließe sich der Audiocode individuell einstellen. Um die Ansteuerung des Audiocodec einfach zu halten, wurde die Variante mit der fixen Verschaltung der Pins gewählt. Die Pins  $\overline{PDAD}$ ,  $\overline{PDDA}$  sind so eingestellt, dass ADU und DAU nicht ausschaltbar sind. Zudem wird der Emphasis-Modus ausgeschaltet, indem DEM0 auf High und DEM1 auf Low gesetzt werden [1].

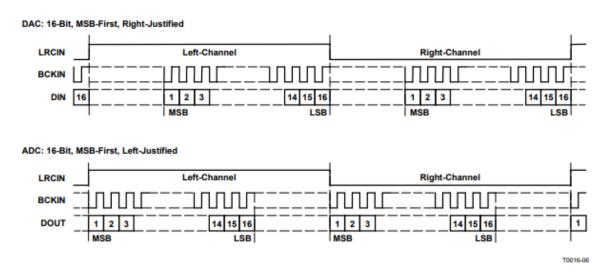

#### Taktschnittstelle und PCM Dataschnittstelle

Der Audiocodec-Takt (CDCCLK) kann je nach Abtastrate fs des Audiosignals variieren. Dabei muss der Takt das 256-, 384- oder 512-fache von fs haben. Wenn ein CDCCLK mit dem 384- oder 512-fachen von fs benutzt wird, wird der Takt mittels einer integrierten Schaltung in dem PCM3006 auf das 256-fache von fs herunter-geteilt. Die hohe Taktung wird für die internen Filter der Ein- und Ausgangssignale benötigt [1].

Neben CDCCLK benötigt der PCM3006 einen Worttakt (LRCIN) und einen Bittakt (BCKIN). Bei einer steigender Worttakt-Flanke wechselt der PCM3006 zum linken Kanal und bei einer fallenden Worttakt-Flanke zum rechten Kanal. Der Worttakt gibt zudem die Abtastfrequenz

| -,                   |         |           |         |  |

|----------------------|---------|-----------|---------|--|

| Abtastrate fs [kHz]  |         | Systemtak | t       |  |

| Abiastrate is [Kriz] | 256     | 384       | 512     |  |

| 32                   | 8.1920  | 12.2880   | 16.3840 |  |

| 44.1                 | 11.2896 | 16.9344   | 22.5792 |  |

| 48                   | 12.2880 | 18.4320   | 24.5760 |  |

Tabelle 4.2.: Systemtakt Frequenzen [1]

fs an. BCKIN gibt dem Audiocodec an, wann ein Bit geschrieben bzw. gelesen werden kann. Bei fallender BCKIN-Flanke wird ein Bit geschrieben, bei steigender gelesen. Beim Bitstrom für den DAU handelt es sich um ein rechtsbündiges und beim Bitstrom für den ADU um ein linksbündiges 16-Bit-Datenformat. Der Most Significant Bit (MSB) wird als erstes geschrieben, bzw. gelesen. BCKIN kann 32-, 48- oder 64-fach höher als der Worttakt eingestellt werden (Abbildung 4.3) [1].

Abbildung 4.3.: Das PCM Signal. Zu sehen ist oben DAC-Signal: Serieller Datenstrom zum Audiocodec; unten ADC-Signal: Serieller Datenstrom vom Audiocodec [1]

Die Takte BCKIN und LRCIN sind jeweils das  $2^2$ - und  $2^8$ -fache vom CDCCLK. Es gibt zwei Möglichkeiten, den Takt zu generieren. Die erste Möglichkeit ist, dass ein Zähler-IC-Baustein z. B. SN74HC590A von Texas Instruments [15], und ein Quarzoszillator auf der Platine eingeplant werden. Der Quarzoszillator mit einem Wert aus der Tabelle 4.2 betreibt den PCM3006. Der Zähler zählt die Takte des Oszillators. Der zweite Pin des Zählers würde das BCKIN-Signal betreiben und der achte Pin das LRCIN-Signal. Die zweite Möglichkeit ist, dass der FPGA alle drei Signale generiert und den PCM3006 ansteuert. Bei der ersten Variante ist der Audiocodec sofort auslesbar, sobald die Platine mit Spannung versorgt wird, jedoch ist die Abtastrate fix und nicht mehr veränderbar. Mit der zweiten Variante ist die Abtastrate fle-

xibel und jederzeit veränderbar, jedoch muss sie zuvor vom FPGA generiert werden. Für die weitere Arbeit wurde die zweite Variante in Betracht gezogen, um die Taktsignale und somit die Abtastrate flexibel zu halten. Zudem entfällt die Synchronisation von BCKIN und LRCIN auf das System, um den Bitstrom DIN/DOUT anzusteuern [1].

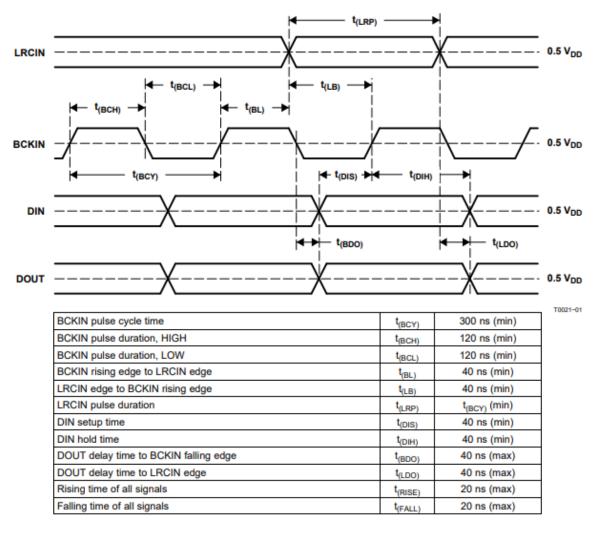

#### **Timing der Signale**

Der FPGA soll entsprechend der zuvor erläuterten Konzeptionentscheidung die Taktsignale LRCIN, BCKIN und CDCCLK sowie die Datensignale DIN und DOUT generieren. Dabei ist darauf zu achten, dass die vom Hersteller angegebenen zeitlichen Relationen der Taktsignale eingehalten werden. Im Anhang A sind die maximalen sowie die minimalen zeitlichen Verschiebungen der einzelnen Signale zu sehen. Der Takt LRCIN wird als Referenz genommen. Alle weiteren Takte und Signale sind auf ihn referenziert. So muss darauf geachtet werden, dass zum Beispiel nach einer Flanke das neue Datensignal mindestens nach 20 ns anliegen muss.

### 4.4. Design der Platine

Im Folgenden wird zuerst die Beschaltung des PCM3006-Bausteins beschreiben. Anschließend wird die Pegelanpassung des Audiosignals erklärt.

### 4.4.1. Grundschaltung

Wie schon erläutert bestimmt der Audiocodec ganz maßgeblich den Schaltungsentwurf für die Platine. Die Spannungsversorgung der analogen ADC- und DAC-Bauteile sowie der digitalen Bauteile wird separat eingespeist. Der ADC wird über die Pins 1 und 2, der DAC über den Pin 24 und die digitalen Bauteile über den Pin 14 versorgt. Dabei ist zu beachten, dass diese Pins mit jeweils zwei Kondensatoren ausgestattet werden müssen, einem 10uF-Elektrolytkondensator und einem 0.1uF-Keramikkondensator. Der Keramikkondensator hat den Vorteil, dass er hochfrequentes Rauschen in der Versorgungsspannung unterdrückt (S.881 in [16]). Der Elektrolytkondensator hingegen liefert als lokaler Ladungsspeicher zusätzlichen Strom für den Fall erhöhten Strombedarfs, sodass die Versorgungsspannung an dem Audiocodec nicht einbricht und verhindert wird, dass Störungen auf das analoge Audiosignal übertragen werden oder sich eine digitale Fehlfunktion ergibt, wenn Vcc die spezifizierten Werte unterschreitet bzw. GND diese überschreitet (S.881 in [16]). Allgemein gilt, dass der Keramikkondensator so nah wie möglich an dem Pin liegen sollte. Der Elektrolytkondensator sollte nicht weiter als 10 cm entfernt vom Pin liegen (S. 87 in [8]). Der PCM3006 hat

asymmetrische Signal-Übertragungseingänge für beide Kanäle. Bei einer asymmetrischen Signalübertragung (engl. single ended) handelt es sich um ein Signal, das sich gegenüber einem Bezugspotential ändert. Dieses liegt in der Regel bei Vcc/2. Ein Kondensator vor dem Eingangspin dient als Gleichspannungsentkopplung und soll die Beeinflussung des Bezugspotentials vor dem Eingangssignal abhalten. Der Wert des Kondensators, der wie ein Hochpassfilter wirkt, soll gerade groß genug sein, um den Gleichanteil zu unterdrücken, aber nicht zu groß, um die niederfrequenten Komponenten des Audiosignals nicht ungünstig zu beeinflussen [17].

Wie oben erläutert wird DEM0 mit der Versorgungsspannung und DEM1 mit der Masse verbunden und die  $\overline{PDAD}$ - und  $\overline{PDDA}$ - Pins mit der Masse verbunden. Die Pins für LR-CIN, BCKIN, SYSCLK sowie DIN und DOUT werden zur Modsys-Baseboard-Schnittstelle geführt.

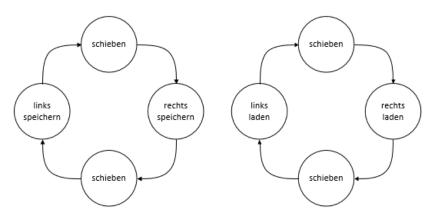

### 4.4.2. Pegelanpassung