# Bachelorarbeit

Sebastian Paulsen

Entwicklung und Evaluierung kompakter Hardware zur Realisierung künstlicher neuronaler Netze im Bereich autonomer Fahrzeuge

#### Sebastian Paulsen

# Entwicklung und Evaluierung kompakter Hardware zur Realisierung künstlicher neuronaler Netze im Bereich autonomer Fahrzeuge

Bachelorarbeit eingereicht im Rahmen der Bachelorprüfung im Studiengang Bachelor of Science Technische Informatik am Department Informatik der Fakultät Technik und Informatik der Hochschule für Angewandte Wissenschaften Hamburg

Betreuender Prüfer: Prof. Dr. Tim Tiedemann Zweitgutachter: Prof. Dr. Michael Schäfers

Eingereicht am: 28. September 2019

#### Sebastian Paulsen

#### Thema der Arbeit

Entwicklung und Evaluierung kompakter Hardware zur Realisierung künstlicher neuronaler Netze im Bereich autonomer Fahrzeuge

#### Stichworte

Hardware, Neuronale Netze, autonome Fahrzeuge, miniatur, FPGA, SoC, Kamera, MIPI, Leiterplatten, JTAG, 3D-Modell

#### Kurzzusammenfassung

Die vorliegende Arbeit beschäftigt sich mit der Entwicklung von kompakter Hardware für autonome Miniaturfahrzeuge. Hierfür wird ein Testfahrzeug inklusive Elektronik im Maßstab H0 (1:87) entwickelt und in Betrieb genommen. Abschließend werden die Ergebnisse bezüglich der Anforderungen an die Hardware diskutiert, ein Fazit gezogen und ein Ausblick gegeben.

#### Sebastian Paulsen

#### Title of Thesis

Development and evaluation of compact hardware for realizing neuronal networks in autonomous cars

#### Keywords

Hardware, Neuronal Network, autonomous Cars, miniature, FPGA, SoC, Camera, MIPI, PCB, JTAG, 3D model

#### Abstract

This thesis focuses on the development of compact hardware for autonomous miniature vehicles. For this purpose, a test vehicle including electronics in scale H0 (1:87) is developed and put into operation. Finally, the results regarding the hardware requirements are discussed, a conclusion is drawn and an outlook is given.

# Inhaltsverzeichnis

| A  | Abbildungsverzeichnis vii |                                                            |    |  |

|----|---------------------------|------------------------------------------------------------|----|--|

| Ta | abell                     | enverzeichnis                                              | ix |  |

| 1  | Ein                       | leitung                                                    | 1  |  |

|    | 1.1                       | Motivation                                                 | 1  |  |

|    | 1.2                       | Zielsetzung                                                | 2  |  |

|    | 1.3                       | Vorgehen                                                   | 2  |  |

| 2  | The                       | eoretische Grundlagen                                      | 3  |  |

|    | 2.1                       | Prozessor                                                  | 3  |  |

|    | 2.2                       | Pipelining                                                 | 5  |  |

|    | 2.3                       | Serielle Datenübertragung                                  | 6  |  |

|    | 2.4                       | Neuronale Netze                                            | 10 |  |

|    |                           | 2.4.1 Training von Neuronalen Netzen                       | 12 |  |

|    | 2.5                       | Autonome Fahrzeuge                                         | 12 |  |

|    |                           | 2.5.1 Die 6 Level des Autonomen Fahrens                    | 12 |  |

|    | 2.6                       | Elektronik – Schaltungstechnik                             | 13 |  |

|    |                           | 2.6.1 Spannungsversorgung                                  | 13 |  |

|    |                           | 2.6.2 Schaltregler                                         | 14 |  |

|    |                           | 2.6.3 Differentielle Signale                               | 15 |  |

|    | 2.7                       | Leiterplattentechnik                                       | 16 |  |

|    |                           | 2.7.1 Lagenaufbau                                          | 16 |  |

|    |                           | 2.7.2 Impedanzen                                           | 17 |  |

| 3  | For                       | $\operatorname{schungsstand}$                              | 22 |  |

|    | 3.1                       | Faller & DC-Car-System                                     | 22 |  |

|    | 3.2                       | Selbstfahrendes Fahrzeug mit externer Prozesseinheit       | 23 |  |

|    | 3.3                       | Selbstfahrendes Fahrzeug mit integrierter Prozessoreinheit | 24 |  |

| 4 | Kon           | ${f zept}$                                             | <b>26</b> |

|---|---------------|--------------------------------------------------------|-----------|

|   | 4.1           | Autonomes Fahrzeug                                     | 26        |

|   | 4.2           | Fahrzeugabmaße                                         | 27        |

|   |               | 4.2.1 Erweiterung des Chassis - Design und Herstellung | 27        |

|   | 4.3           | Verarbeitung der Kameradaten                           | 32        |

|   |               | 4.3.1 Datenverarbeitung im Fahrzeug oder extern        | 33        |

|   |               | 4.3.2 Auswahl der verarbeitenden Hardware              | 34        |

|   |               | 4.3.3 Training von neuronalen Netzen                   | 35        |

|   |               | 4.3.4 Boardauswahl oder eigene Platine                 | 35        |

|   | 4.4           | Pipelinekonzeption                                     | 37        |

|   | 4.5           | Weitere Anforderung an die Platine                     | 38        |

|   | 4.6           | Zusammenfassung des Konzepts                           | 38        |

|   | 4.7           | Architektur des Konzepts                               | 39        |

| 5 | $\mathbf{Um}$ | $\operatorname{setzung}$                               | 40        |

|   | 5.1           |                                                        | 40        |

|   |               | 5.1.1 Vergleich Xilinx Z-7020 mit Xilinx Z-7030        | 40        |

|   | 5.2           | Xilinx Z-7030                                          | 41        |

|   |               | 5.2.1 IO und Controller                                | 42        |

|   |               | 5.2.2 LVDS                                             | 44        |

|   | 5.3           | Kamerainterface                                        | 44        |

|   |               | 5.3.1 Pinbelegung Kamera Header                        | 44        |

|   | 5.4           | Programmierung des SoC                                 | 45        |

|   |               | 5.4.1 USB-Chip                                         | 45        |

|   |               | 5.4.2 Konfiguration des USB-Chips                      | 45        |

|   | 5.5           | Persistenter Speicher des SoC                          | 46        |

|   |               | 5.5.1 SD-Chip                                          | 46        |

|   |               | 5.5.2 Flashspeicher                                    | 46        |

|   | 5.6           | Auslagerungsspeicher - DRAM                            | 47        |

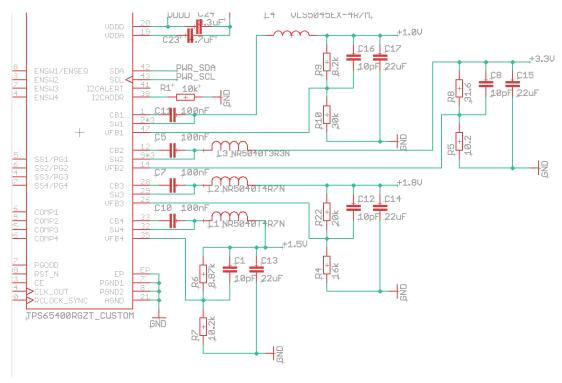

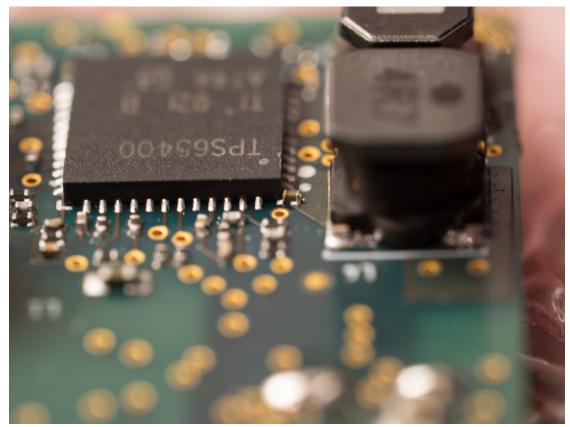

|   | 5.7           | Spannungsversorgung                                    | 48        |

|   |               | 5.7.1 Vierfach Spannungsregler - TI TPS65400           | 48        |

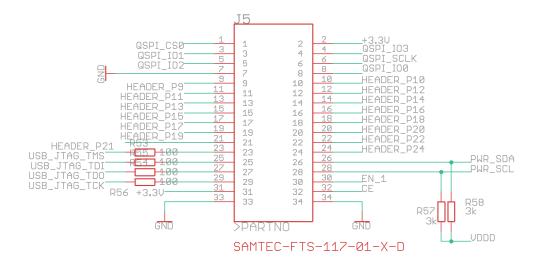

|   | 5.8           | Peripherie                                             | 50        |

|   |               | 5.8.1 Steckbrücken und Stiftleiste                     | 50        |

|   |               | 5.8.2 I/O Header                                       | 52        |

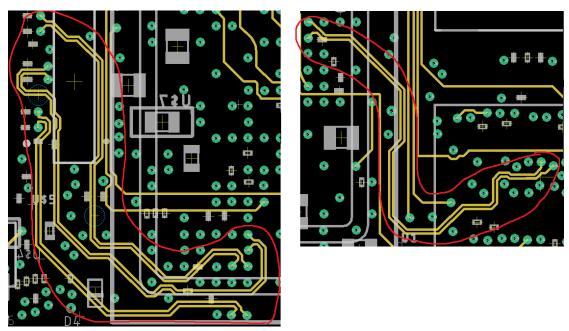

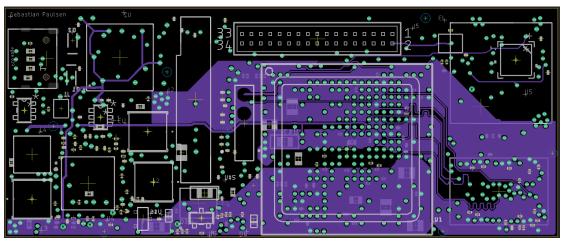

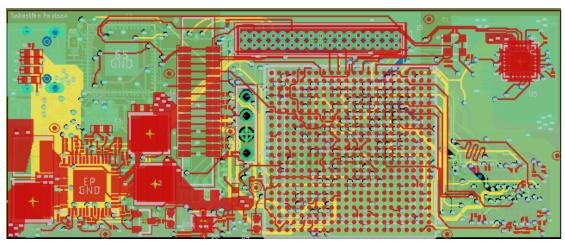

|   | 5.9           | Layout                                                 | 52        |

|   |               | 5.9.1 Umsetzung des Layouts                            | 53        |

### Inhaltsverzeichnis

|              |       | 5.9.2   | DDR                                 | 54         |

|--------------|-------|---------|-------------------------------------|------------|

|              |       | 5.9.3   | Layout von differentiellen Signalen | 54         |

|              |       | 5.9.4   | Powerschichten                      | 56         |

| 6            | Inb   | etriebr | name und Evaluation der Hardware    | <b>5</b> 8 |

|              | 6.1   | Elektr  | ische Überprüfung                   | 58         |

|              |       | 6.1.1   | Optische Inspektion                 | 58         |

|              |       | 6.1.2   | Durchgangsprüfung von Kondensatoren | 60         |

|              |       | 6.1.3   | Stromzufuhr                         | 60         |

|              | 6.2   | Funkt   | ionsprüfung der Peripherie          | 64         |

| 7            | Disl  | kussioi | ı der Ergebnisse                    | <b>7</b> 0 |

| 8            | Fazi  | it und  | Ausblick                            | <b>7</b> 2 |

|              | 8.1   | Fazit   |                                     | 72         |

|              | 8.2   | Ausbli  | ck                                  | 72         |

| Li           | terat | urverz  | zeichnis                            | 74         |

| $\mathbf{A}$ | Anl   | nang    |                                     | 77         |

| ~            |       |         | keitserklärung                      | 86         |

# Abbildungsverzeichnis

| 2.1  | Vergleich Pipeline-Bearbeitung mit sequentieller Bearbeitung | 6  |

|------|--------------------------------------------------------------|----|

| 2.2  | $I^2$ C mit zwei Knoten                                      | 7  |

| 2.3  | SPI                                                          | 8  |

| 2.4  | Vergleich MIPI C-PHY und D-PHY                               | 9  |

| 2.5  | Neuron                                                       | 11 |

| 2.6  | Übersicht Neuronales Netz                                    | 11 |

| 2.7  | Temperaturzunahme bei unterschiedlichem Leiterdurchmessern   | 14 |

| 2.8  | Buck Converter                                               | 15 |

| 2.11 | Grafik Impedanzen Aufteilung Empfänger Sender Leitung        | 17 |

| 2.12 | Grafik unterschiedlicher Impedanzklassen                     | 18 |

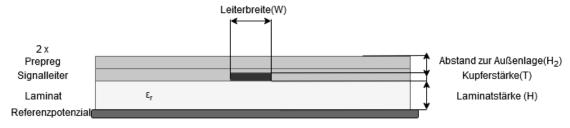

| 2.13 | Surface Microstrip                                           | 18 |

| 2.14 | Embedded Microstrip                                          | 19 |

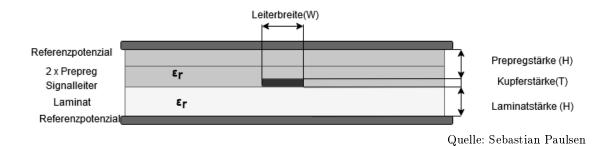

| 2.15 | Single Stripline symmetrisch                                 | 20 |

| 2.16 | Single Stripline asymmetrisch                                | 20 |

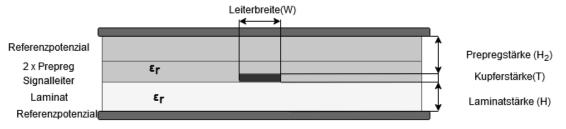

| 2.17 | Dual Stripline                                               | 21 |

| 3.1  |                                                              | 23 |

| 3.2  | Architektur Projekt Zheng Wang                               | 24 |

| 3.3  | Architektur PiCar                                            | 25 |

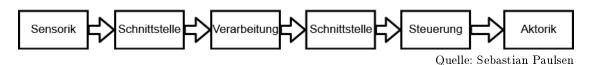

| 4.1  | Konzept Autonomes Fahren mit Sensorik-Prozessor-Aktorik      | 26 |

| 4.2  | Faller Car System Chassis-Kit                                | 27 |

| 4.3  | H0 Gigaliner                                                 | 28 |

| 4.4  | H0 Bus                                                       | 28 |

| 4.5  | CAD-Zeichnung des Chassis                                    | 30 |

| 4.6  | Gegenüberstellung 3D-Modell mit H0 im Miniatur Wunderland    | 31 |

| 4.7  | Schaltung PWM-Steuerung                                      | 32 |

| 4.8  | Ansatzübersicht                                              | 34 |

| 4.9  | Pipelineüberblick Sensorik zu Aktorik                        | 37 |

| 4.10 | Architektur des Konzepts                               | 9 |

|------|--------------------------------------------------------|---|

| 5.1  | Block Diagram                                          | 2 |

| 5.2  | MIO Übersicht                                          | 3 |

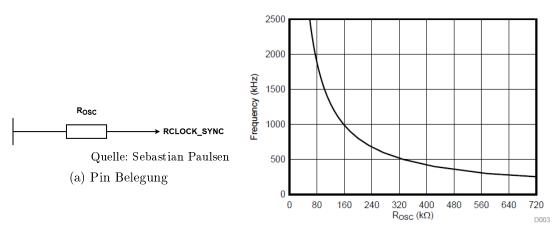

| 5.3  | Pin Belegung                                           | 4 |

| 5.4  | SD Chip Symbol                                         | ŝ |

| 5.5  | W25Q128JVSIQ                                           | 7 |

| 5.6  | Spannungsübersicht                                     | 3 |

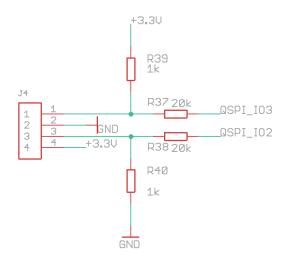

| 5.7  | Schaltplan Widerstände                                 | 9 |

| 5.9  | Pin Belegung Stiftleiste                               | 1 |

| 5.10 | Pin Belegung I/O Header                                | 2 |

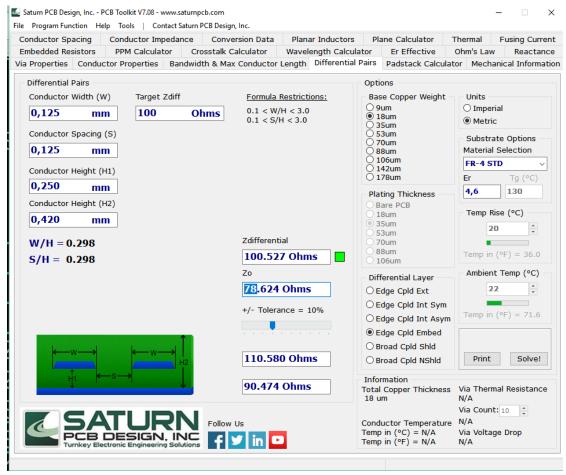

| 5.11 | Aufnahme von PCB Toolkit                               | ŏ |

| 5.12 | Verlegung differentielle Signale                       | ĉ |

| 5.13 | Struktur der Versorgungsleitungen                      | 7 |

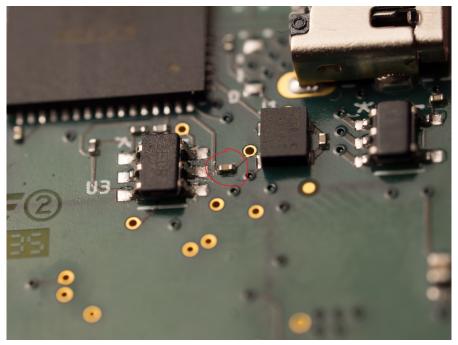

| 6.3  | Spannungsregler Kondensator erstes Board               | n |

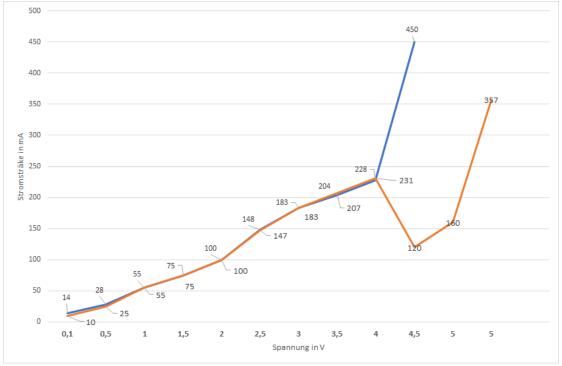

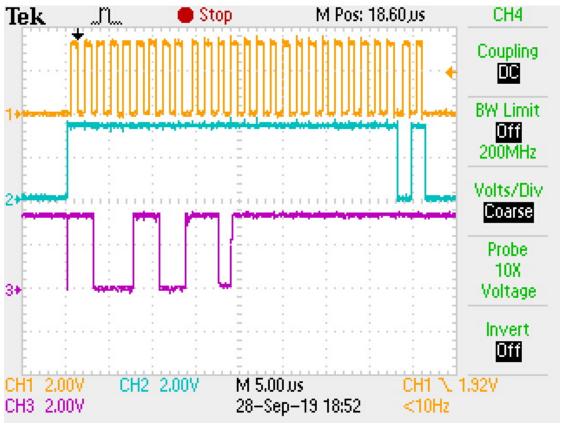

| 6.4  | Vergleich Stromverlauf zu Spannung                     |   |

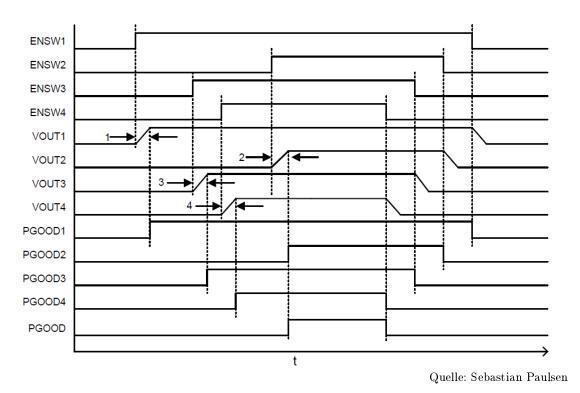

| 6.5  | Vorgabe Datenblatt TPS65400                            |   |

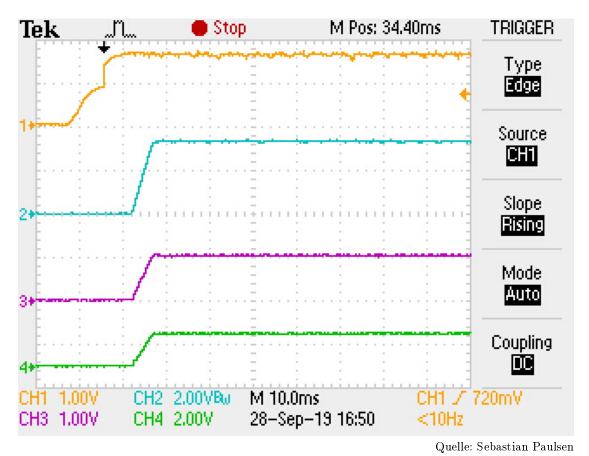

| 6.6  | Messung von oben nach unten EN1, VOUT1, VOUT2, VOUT3 6 | - |

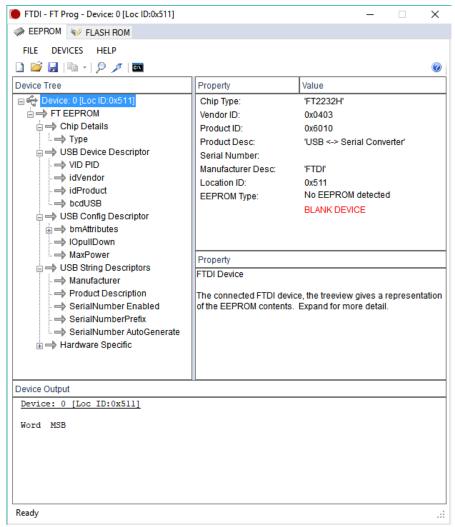

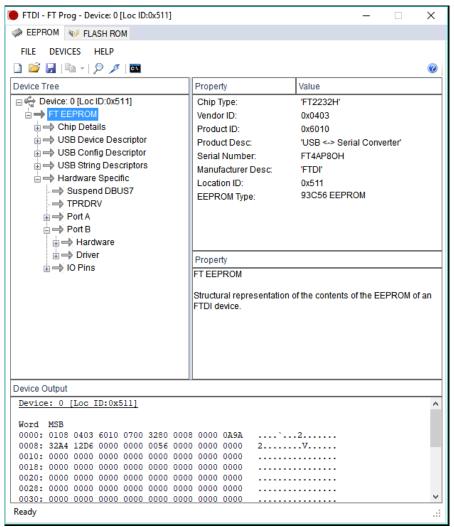

| 6.7  | EEPROM nicht erkannt in FT-Prog                        |   |

| 6.8  | Kondensator an Stelle eine Widerstandes eingelötet     |   |

| 6.9  | EEPROM Kommunikation                                   |   |

| 6.10 | EEPROM erkannt in FT-Prog                              |   |

| 0.10 |                                                        | , |

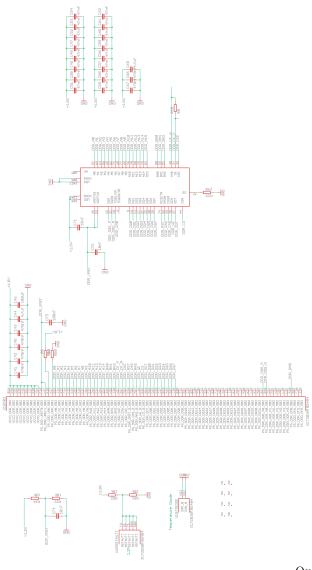

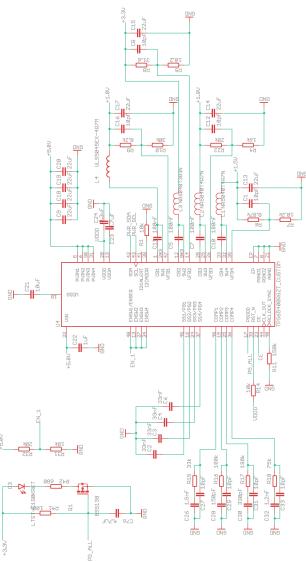

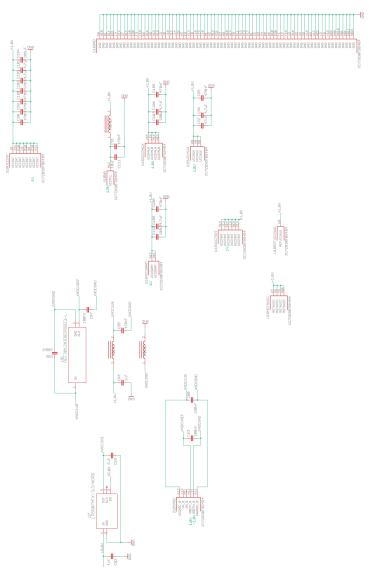

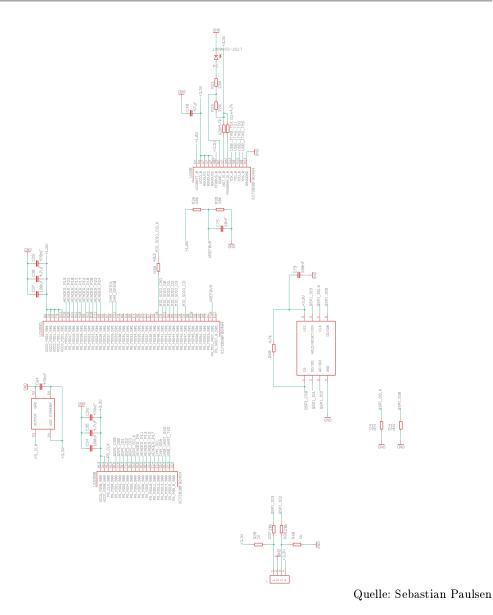

| A.1  | Schaltplan Seite 1                                     | 7 |

| A.2  | Schaltplan Seite 2                                     | 3 |

| A.3  | Schaltplan Seite 3                                     | 9 |

| A.4  | Schaltplan Seite 4                                     | ) |

| A.5  | Schaltplan Seite 5                                     | 1 |

| A.6  | Schaltplan Seite 6                                     | 2 |

| A.7  | Schaltplan Seite 7                                     | 3 |

| A.8  | Schaltplan Seite 8                                     | 4 |

| A.9  | Layout der Platine                                     | õ |

# Tabellenverzeichnis

| 2.1 | USB Versionsvergleich                       | 8  |

|-----|---------------------------------------------|----|

| 4.1 | Messung der Größen von H0 Bus und Gigaliner | 28 |

| 4.2 | Peripherie Vergleich                        | 36 |

| 5.1 | Vergleich Z-7020 mit Z-7030[Vgl. S.2 23]    | 41 |

| 5.2 | Stellungen der Steckbrücke                  | 51 |

| 6.1 | Messung am Board 1                          | 61 |

| 6.2 | Messung am Board 2                          | 61 |

# 1 Einleitung

Alle zwei Jahre verdoppelt sich die Menge an Transistoren, die auf eine bestimmte Fläche passen [13]. Folglich wird der benötigte Platz für die gleiche Rechenleistung immer kompakter, womit Entwicklungen in der Industrie auch immer kompakter und leistungsstärker werden. Was vor einigen Jahren einen ganzen Raum ausgefüllt hat, lässt sich heutzutage in der Hosentasche unterbringen, was zum Beispiel an der Entwicklung des Smartphone ersichtlich wird. Diese Entwicklung lässt sich auch auf die Rechenhardware in der Automobilindustrie übertragen.

Heutige Fahrzeuge fahren mit vielen Assistenzsystemen, die dem Fahrer helfen. Ein Beispiel hierfür ist der Distanzsensor, welcher durch die Messung der Distanz zum vorausfahrenden Fahrzeug eventuelle Aufprälle ermittelt und den Fahrer durch visuelle und akustische Signale warnen kann oder eine Bremsung einleitet. Die Assistenzsysteme bilden Bestandteile autonomes Fahrens.

#### 1.1 Motivation

Katastrophen wie die Kernschmelze in einem Kernkraftwerk in Fukushima [Vgl. 4] machen exemplarisch deutlich, dass es Probleme gibt, für dessen Lösung nur besonders kleine und spezialisierte Roboter benutzt werden können. Dies gilt für die Orte, an denen wegen Unzugänglichkeit und Abschirmung weder Menschen noch ferngesteuerte Roboter Zugriff haben. Für dieses Szenario benötigt man autonome Fahrzeuge, die sich ohne menschliche Interaktion durch Geröll bewegen können und verletzte Personen finden oder notwendige Arbeiten ausführen. MDiese Arbeit soll einen Beitrag dazu leisten, sich mit autonomen Miniaturfahrzeugen außeinanderzusetzen und deren Entwicklungswege auszuloten.

### 1.2 Zielsetzung

Das Ziel dieser Arbeit ist es, zu evaluieren, welche elektronischen Bauteile für ein autonomes Fahrzeug benötigt werden und wie sich die Auswahl der Bauteile auf eine minimale Größe des Fahrzeugs auswirkt. Deshalb geht diese Arbeit der folgenden Fragestellung nach, inwiefern die Entwicklung einer kompakten Hardware für autonome Fahrzeuge realisiert werden kann.

Dabei werden die Bauteile auf eine Platine gebracht, welche in das Fahrzeug einbaut werden soll. Die Platine soll die Daten der Sensoren in Steuerungssignale für die Aktoren des Fahrzeuges umwandeln. Auf der Platine soll es neben den Sensoren und Aktoren noch weitere Interfaces geben, die für die Initialisierung einer Platine benutzt werden können.

### 1.3 Vorgehen

Um das oben genannte Ziel zu verfolgen, ergibt sich der erste Schritt, nach Informationen über bereits vorhandene Arbeiten und Ansätze bezüglich des autonomen Fahrens in Miniaturfahrzeugen zu recherchieren. Dafür wird der aktuelle Forschungsstand analysiert und beschrieben.

In einem nächsten Schritt werden die für die darauf folgenden Kapitel benötigten theoretischen Grundlagen dargestellt und erläutert. Die theoretischen Grundlagen sollen einen Überblick über die beschriebene Thematik geben und für diese Arbeit relevanten Unterpunkte eine Basis bieten.

Darauf folgend wird die Konzeption und die Umsetzung der kompakten Hardware und seiner elektronischen Bauteile beschrieben. Der Fokus dabei wird auf die Auswahl der elektrischen Bauteile für diverse Interfaces gelegt. Diese definieren die Optionen, welche Sensoren, Aktoren und weitere Peripherie angeschlossen werden können.

Nachdem die Planung abgeschlossen ist, wird die daraus resultierende Hardware in Betrieb genommen.

Abschließend werden die Ergebnisse diskutiert, sowie ein Fazit gezogen. In Hinsicht auf die Ergebnisse der Umsetzung werden eine Diskussion und ein Fazit die Arbeit vollenden.

# 2 Theoretische Grundlagen

Die folgenden theoretischen Grundlagen sollen den theoretischen Rahmen für die Entwicklung kompakter Hardware bieten, die im Laufe dieser Arbeit verwendet werden.

Folgend werden datenverarbeitende elektrische Schaltungen beschrieben.

#### 2.1 Prozessor

Prozessoren sind elektronische Schaltungen, die Daten verarbeiten. Es gibt unterschiedliche Prozessortypen, die je nach Einsatzgebiet anders spezialisiert sind. Dabei besitzen sie zum Beispiel unterschiedliche Registerbreiten, Befehlssätze oder Architekturen.

IC Zum besseren Verständnis der folgenden datenverarbeitenden Schaltung wird der Begriff Integrated Circuit (IC) an dieser Stelle erläutert. Unter einem IC versteht man eine elektronische Funktionseinheit, die sich durch eine auf einem gemeinsamen Halbleitersubstrat(Chip) realisierte Vielzahl elektrisch und mechanisch untrennbar miteinander verbundener elektronischer Funktionselemente(Transistor- und Diodenfunktionen, Widerstände, Kondensatoren etc.) mit Abmessungen im Mikrometer- und Submikrometer-Bereich kennzeichnet[Vgl. S.394, 2].

CPU Der Kern eines Computers ist die zentrale Verarbeitungseinheit (Central Processing Unit, CPU). Diese besteht im wesentlichen aus den Komponenten eines Steuerwerks, Rechenwerks, mehreren Registern und eines Verbindungssystems zur Ankopplung von Speicher- und Peripheriekomponenten. [S.18, 2] Der Begriff Mikroprozessor beschreibt die auf einem Chip realisierte CPU eines Computersystems. [S.19, 2] Damit sind die meisten Prozessoren, die in Computern eingesetzt werden, Mikroprozessoren.

**GPU** Graphical Processing Unit (GPU) sind spezialisierte Prozessoren die hauptsächlich für die rechenintensiven Berechnung von 2D- und 3D-Grafiken eingesetzt werden.[15]

Mikrocontroller Ein Mikrocontroller ist ein vollständiges Mikrocomputersystem auf einem Chip. Mikrocontrollerkern (Core), Speicher, Peripheriekomponenten und Interrupt-System sind gemeinsam auf einem Chip integriert und über einen bzw. mehrere Busse miteinander verbunden. Ein Mikrocontrollerkern ist im Sinne eines modularen MC-Konzepts die On-Chip-integrierte CPU. Dieser beinhaltete im Wesentlichen ein komplexes Steuerwerk, mehrere Register, eine Arithmetic Logic Unit (ALU) und eine Bussteuereinheit. [S.242-243, 2]

**Prozessorarchitekturen** CPUs, wie sie in Mikrocontrollern vorkommen, haben unterschiedliche Prozessarchitekturen implementiert. Prozessorarchitekturen zeichnen sich durch ihre unterschiedlichen Befehlssätze, Datenbreite und Registeranzahl aus. Diese machen sie je nach Konfiguration besonders schnell oder platzsparend. Beispiele für Prozessorarchitekturen sind RISC, x86 oder CISC.

FPGA FPGA (Field Programmable Gate Array) bestehen aus Transistoren, die in Gatter angeordnet sind. Diese Transistoren lassen sich bei FPGAs, außer bei Antifusebased FPGAs nur einmalig, beliebig häufig programmieren und ermöglichen durch Verkettungen die Realisierung unterschiedlicher Aufgaben. Durch die Anordnung der Transistoren in Gattern in einem FPGA ist es möglich, parallel viele Daten zu verarbeiten. Diese Eigenschaft ist besonders in der Datenverarbeitung von Datenströmen nötig. Die FPGA-Programme werden am Computer erstellt und dann insofern optimiert, als sie in die Gatterform passen und falls nötig Bereiche der Schaltung teilen. In FPGA gespeicherte Programme sind insofern flüchtig, dass sobald an dem Chip keine Spannung mehr anliegt, sie das gespeicherte Programm verlieren. Da FPGAs frei programmierbar sind und keiner Prozessorarchitektur unterliegen, werden sie mit einer Hardware Description Language (HDL) programmiert. Diese wird dann von der menschenlesbaren Hochsprache in die Gattersynthese übersetzt. FPGAs sind durch ihren Aufbau sehr flexibel, aber sie zeichnen sich auch darin aus, dass sie anspruchsvoll zu programmieren sind, da Signallaufzeiten eingehalten werden müssen. [Vgl. S.388-391, 2]

SoC SoC (System on Chip) gibt es in vielen Varianten. Als die verbreiteste Variante kann die Verbindung von einem FPGA und einem Mikrocontroller auf einem Silizium Chip gelten. Der Vorteil dieses Chips ist es, dass die rechenleistungsintensiven Aufgaben im FPGA berechnet werden können, wohingegen im Mikrocontroller die Entscheidungslogik ausgeführt wird. Mit dieser Übersicht über die Hardware können vergleichende Bewertungen im Konzept getätigt werden.

## 2.2 Pipelining

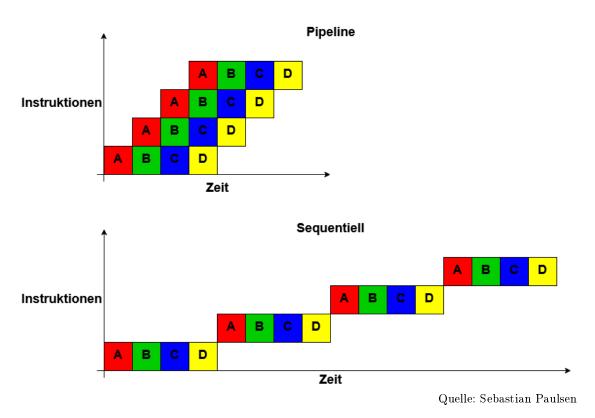

Pipelining stammt ursprünglich aus der Zeit der Industrialisierung, in welcher in Fabriken Arbeiten am Fließband ausgeführt worden sind. Es beschreibt in der Informatik die Abfolge der Aufgabenverarbeitung eines Prozessors. Dabei werden im Prozessor Aufgaben nicht sequenziell abgearbeitet, sondern die Aufgaben laufen parallel ab. Dies hat zur Folge, dass die Menge an bearbeiteten Aufgaben ab einer bestimmten Zeit erhöht wird und dies ermöglicht neue Ergebnisse nach jedem neuen Takt. Die folgende Grafik2.1 stellt dar, wie mehr Aufgaben im Pipeline-Verfahren im Vergleich zum sequentiellen Verfahren ab einem gewissen Zeitpunkt verarbeitet werden. [Vgl. 19]

Abbildung 2.1: Vergleich Pipeline-Bearbeitung mit sequentieller Bearbeitung

# 2.3 Serielle Datenübertragung

Serielle Datenübertragung ist die verbreitetste Datenübertragung zwischen ICs. Die Datenübertragung findet meist zwischen zwei Platinen oder zwischen einer Platine und einem Sensor statt. Jede serielle Übertragungsart hat unterschiedliche Protokolle, Leitungsanzahlen, elektrische Charakteristiken und Nachrichtenformate. Das macht die Datenübertragungen besonders flexibel, daher können meist die gleichen Sensoren mit unterschiedlichener Transmitterhardware an unterschiedlichen Schnittstellen angeschlossen werden. [Vgl. S.109-112, 5]

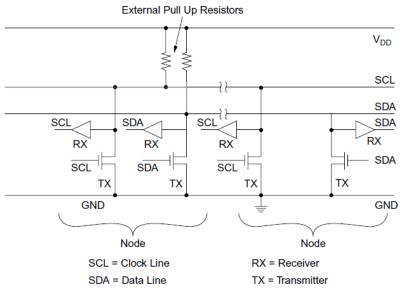

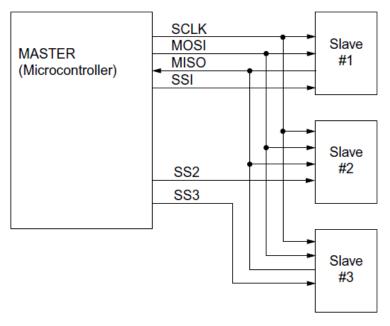

Die folgende Aufzählung über I2C, SPI, und USB zeigt die in der Industrie häufig verwendeten Standards und stellt deren Hauptmerkmale dar:

#### I2C Leitungsanzahl: SCL SDA VDD GND

Übertragungsgeschwindigkeit: 100 kb/s, 400 kb/s, 1 Mb/s, 3,4 Mb/s

Maximallänge: Hängt von der Datenraten ab. Maximallänge 10 m bei niedrigster Daten-

rate.[Vgl. S.65-70, 5]

Quelle: [Vgl. S.66, 5]

Abbildung 2.2:  $I^2$ C mit zwei Knoten

#### SPI Leitungsanzahl: MISO MOSI SCLK SSI

Übertragungsgeschwindigkeit: 20 Mb/s bis 100 Mb/s

Maximallänge: Bis zu 1 m aber typischerweise nur wenige Fuß[Vgl. S.143ff, 5]

Quelle: [Vgl. S.144, 5]

Abbildung 2.3: SPI

**USB** Leitungen: Vier Leitungen Ground, DC 4.75 bis 5,25 V, Data Positive(DP) und Data Minus(DM)

| Version | Übertragungsgeschwindigkeit |

|---------|-----------------------------|

| 1.1 1.5 | 12 Mbps                     |

| 2.0     | $480\mathrm{Mbps}$          |

| 3.1     | 5 oder 10 Gbps              |

Tabelle 2.1: USB Versionsvergleich

Maximallänge: 3 m bei Version 3.1 sonst 5 m bei den anderen Versionen bis hin zu 100 m mit Repeatern.

[Vgl. S.147-151, 5]

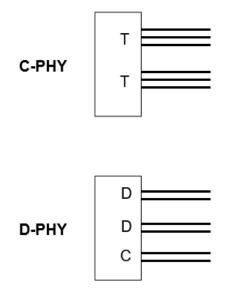

MIPI Standard Der MIPI (Mobile Industry Processor Interface) Standard beschränkt sich nicht wie der Name sagt nur auf den mobilen Sektor sondern ist vielmehr in den letzten Jahren zu einem allgemein genutzten Standard geworden. Der Standard definiert zwei

Hardware Schnittstellen (D-PHY und C-PHY) 2.4, zu denen zwei Softwareschnittstellen (CSI-2 und DSI-2) kompatibel sind. CSI-2 steht für Camera Serial Interface und beschreibt die kommunikation zwischen einer Camera und einer Platine. DSI-2 steht für Display Serial Interface und beschreibt die Kommunikation zwischen einem Display und einer Platine.

[20] Leitungsanzahl: Variable Anzahl von differentiellen Leitungen

Übertragungsgeschwindigkeit: Maximal 5,7 Gbps

Maximallänge: Wenige cm auf der Platine oder kurze Leitungen.

[Vgl. S.193f, 5] Ein Vergleich des Aufbaus der physikalischen Schnittstellen C-PHY und D-PHY:

#### Vergleich der beiden elektrischen Standards C-PHY D-PHY

D-PHY besitzt ein differentielles Clock-Signal und ab einem Datensignal. C-PHY dagegen besitzt dreier Leitungen.

Quelle: Sebastian Paulsen

Abbildung 2.4: Vergleich MIPI C-PHY und D-PHY

**Ethernet** Anzahl der Leitungen: Je nach Standard Übertragungsgeschwindigkeit: 10 Mb/s bis 100 Gb/s

Maximallänge: Bis zu 100 m ohne Repeater oder Ähnliches.

[Vgl. S.129ff, 5] Das Verständnis für serielle Kommunikation ist wichtig Voraussetzung für die im vierten Kapitel folgende Konzeption

#### 2.4 Neuronale Netze

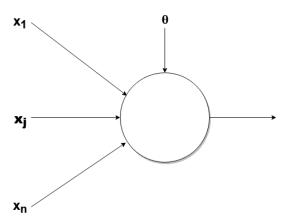

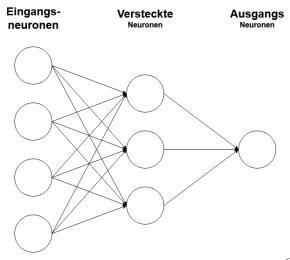

Um die Hardware Anforderungen für neuronale Netze bewerten zu können werden diese im Folgenden erläutert. Neuronale Netze sind eine Ansammlung von künstlichen Neuronen, die in drei unterschiedlichen Schichten unterteilt sind - die Eingangsschicht, die versteckte Schicht und die Ausgangsschicht. Künstliche Neuronen siehe Grafik 2.5 besitzen wie biologische Neuronen auch Eingänge (Dendriten) und Ausgänge (Axonen).

Diese Ein- und Ausgänge leiten elektrische Signale vom vorherigen bzw. zum nächsten Neuron. Dabei werden die Eingangssignale $(x_i)$ , welche mit unterschiedlichen variablen Gewichten $(W_i)$  multipliziert werden, im Neuron aufaddiert und mit einem Schwellwert $(\theta)$  substrahiert. Daraus resultiert der sogenannte Aktivierungswert $(\alpha)$ :

$$\alpha = W_1 * x_1 + W_2 * x_2 - \theta$$

Der Aktivierungswert wird in die Aktivierungsfunktion  $f(\alpha)$  eingesetzt. Die Aktivierungsfunktion der Neuronen ist eine mathematische Funktion, wobei anfänglich eine binäre Funktionen verwendet wurde:

$$y = sign \alpha$$

$y = +1, wenn \alpha \ge 0$   $y = -1, wenn \alpha < 0$

Quelle: Sebastian Paulsen

Abbildung 2.5: Neuron

Die Eingangsschicht fungiert als eine der beiden Schnittstellen zum neuronalen Netz 2.6. Sie reagiert nicht auf synaptische Verbindungen, sondern auf Daten von außerhalb. Die zweite Schichtkategorie ist die optionale versteckte Schicht, die aus mehreren Unterschichten bestehen kann. Die dritte Schichtkategorie ist die Ausgangsschicht, welche als zweite Schnittstelle fungiert und Daten an ihre Knoten liefert. [Vgl. 25]

Quelle: Sebastian Paulsen

Abbildung 2.6: Übersicht Neuronales Netz

#### 2.4.1 Training von Neuronalen Netzen

Durch die variablen Gewichte, können Neuronale Netze lernen. Es gibt unterschiedliche Ansätze wie das Netzt trainiert wird bzw. lernt.

**Backpropagation** Bei der Backpropagation werden dem Netz die Eingangswerte und die erwarteten Ausgangswerte als Tupel gegeben. Mit diesen Werten werden die Gewichte angepasst, damit der Eingangswert den erwarteten Ausgangswert ausgibt. Dies wird mit möglichst vielen Eingangs- und Ausgangswerten (Tupeln) gemacht. Durch Iteration lernt das Neuronale Netz. [Vgl. 25]

Genetisches Lernen Beim genetischen Lernen werden zu Beginn zufällige neuronale Netze generiert. Nach den Durchläufen der Testdaten in den Netzen werden die 50% der neuronalen Netze mit der höchsten Güte selektiert. Dann werden die restlichen 50% wieder aufgefüllt und dabei gibt es zwei Möglichkeiten, wie aufgefüllt werden kann. Entweder werden vorhandene kopiert oder mutiert, also leicht verändert, oder miteinander gekreuzt. Dieser Vorgang wird für mehrere Generationen wiederholt, bis sich höhere Güten der neuronalen Netze erzielen lassen. [Vgl. S.62-63, 16] Durch die Grundlagen der neuronalen Netze wird deutlich wie rechenintensiv die Berechnung von neuronalen Netzen ist.

## 2.5 Autonome Fahrzeuge

Weil die Evaluation einer Hardware für autonome Fahrzeug im Zentrum dieser Arbeit steht, wird im Folgenden eine Kategorisierung für autonome Fahrzeuge vorgestellt. Autonome Fahrzeuge, insbesondere Automobile, werden laut der Society of Automotive Engineers (SAE) in sechs unterschiedliche Level der Autonomie unterteilt. Kriterium für autonomes Fahren ist die Bewertung der Rolle des Fahrers und die Art des autonomen Systems. [Vgl. S.19-23, 17]

#### 2.5.1 Die 6 Level des Autonomen Fahrens

**Level 0** Das Auto hat keine Assistenzsysteme verbaut. Der Fahrer steuert das Fahrzeug.

Level 1 Das erste Level beschreibt das Vorhandensein von Assistenzsystemen, die dem Autofahrer in seltenen Situationen helfen und entweder bremsen bzw. beschleunigen oder steuern.

Level 2 Das zweite Level beschreibt das Vorhandensein von Assistenzsystemen, die dem Autofahrer während des Fahrens gleichzeitig bei dem Bremsen bzw. Beschleunigen und bei dem Steuern helfen.

Level 3 Das dritte Level beschreibt ein Assistenzsystem, dass das Auto vollständig steuern kann, aber in bestimmten Situationen die Kontrolle dem Menschen übergibt.

Level 4 Beim vierten Level steuert das Assistenzsystem das gesamte Fahrzeug und gibt nur in Notfällen die Kontrolle an den Fahrer zurück.

Level 5 Menschen sind nur noch Passagiere in Fahrzeugen und steuern das Fahrzeug nicht mehr.

Wenn im Folgenden autonome Fahrzeuge beschrieben werden, ist darunter die Teilmenge der gesamten Fahrzeuge zu verstehen, die durch Sensoren und Aktoren gesteuert werden.

# 2.6 Elektronik – Schaltungstechnik

Um die unterschiedlichen Hardware Ansätze richtig bewerten zu können, werden im Folgenden einige Grundlagen erläutert.

#### 2.6.1 Spannungsversorgung

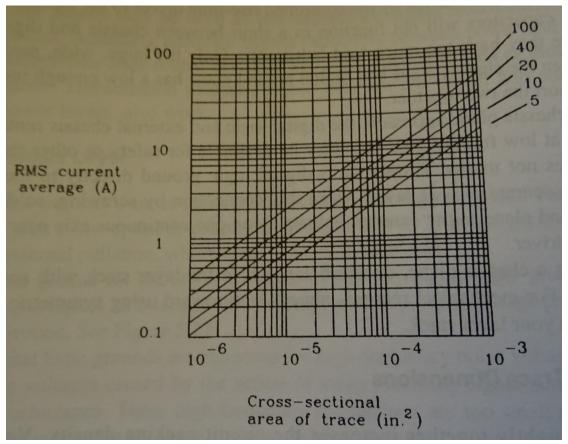

Leiterbahnen, durch die Strom fließt, erhitzen sich abhängig von dem Durchmesser der Leitung und der elektrischen Stromstärke. Deswegen ist es wichtig, die Leitungsbreite so zu dimensionieren, dass die Temperatur der Platine nicht über die maximale Temperatur der Bauteile steigt. Im Folgenden ist der Graph der Leitungsdurchmesser und die elektrische Stromstärke abgebildet. [Vgl. S.224ff., 10]

Quelle: [Vgl. S.226, 10]

Abbildung 2.7: Temperaturzunahme bei unterschiedlichem Leiterdurchmessern

Für digitale Schaltungen werden Kondensatoren an den Eingängen verwendet. Diese verhindern, dass die Spannung bei schnellen Schaltungen am Eingang der Bauteile fällt. Diese sollen Störungen auf der Versorgungsleitung dämpfen, sodass ein fehlerfreier Betrieb möglich ist. Eine solche Störung kann zum Beispiel das kurzzeitige Einsinken der Versorgungsspannung sein.

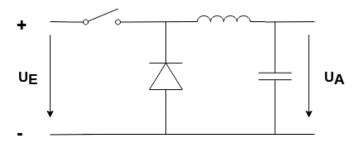

#### 2.6.2 Schaltregler

Ein Schaltregler bzw. der spezielle Buck Converter ist ein elektrisches Bauteil, dass aus höheren Spannungen durch das gezielte Regeln eines binären Schalters mit Hilfe eines Tiefpassfilters, eines Oszillators und eines Spannungsteilers für die Rückinformation niedrigere Spannungen erzeugt, um die unterschiedlichen Spannungen für Bauteile auf einer

Platine zu ermöglichen. Mit der Frequenz des Oszillators überprüft der Schaltregler die Spannung am Spannungsteiler und schaltet den Schalter an oder aus. Der Tiefpassfilter schafft mit Hilfe der Induktivität die als Zwischenspeicher der Energie dient, aus den kurzen Spannungsimpulsen eine geglättete Ausgangsspannung.

Quelle: Sebastian Paulsen

Abbildung 2.8: Buck Converter

#### 2.6.3 Differentielle Signale

Bei der Übertragung von Signalen über elektrische Leitungen können äußere Einflüsse, wie elektromagnetische Impulse, die Signale beeinflussen und verzerren. Um dem entgegenzuwirken, werden Techniken angewandt, die die empfangenen Übertragungsinhalte auf ihre Korrektheit überprüfen. Ein Beispiel dafür ist das Paritätsbit, welches indiziert, ob eine ungerade oder gerade Anzahl von High-Signalen in einer Nachricht enthalten sind. Solche Übertragungen sind aber weiter anfällig für Störungen von außen, da sie sich nicht auf jedes Bit einzeln beziehen, sondern die Gesamtheit der Bits betrachten [Vgl. S.66, 2].

Differentielle Signale vermeiden Übertragungsfehler indem sie über zwei elektrische Leitung jeweils ein unnegiertes und ein negiertes Signal übertragen, somit werden die beiden Signale miteinander referenziert. Dabei können die Signale auch negative Spannungen aufweisen. Durch die differentiellen Signale können Fehler in der Übertragungen leichter detektiert werden und vermeiden die Berechnung von Paritätsbits [Vgl. S.1116-1123, 9].

# 2.7 Leiterplattentechnik

Für die Analyse von Hardware im Konzept Kapitel werden im Folgenden einige Grundlagen vorgestellt.

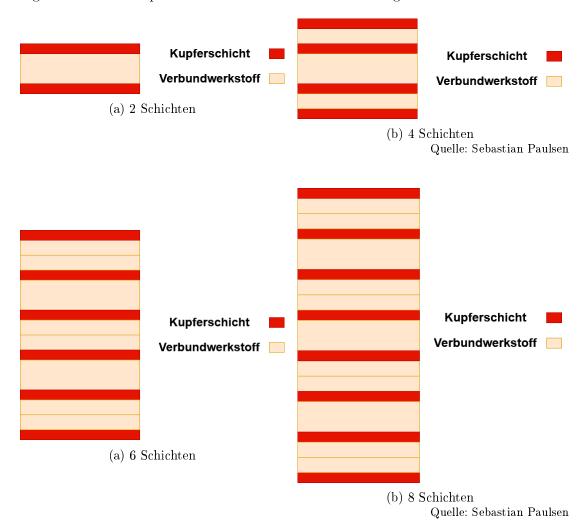

#### 2.7.1 Lagenaufbau

Leiterplatten sind in unterschiedliche Schichten unterteilt. Die Anzahl der Schichten variiert je nach Anwendungsfall und ergibt meist eine Potenz von zwei.

Folgend wird der beispielhafte Aufbau von Platinen mit dargestellt.

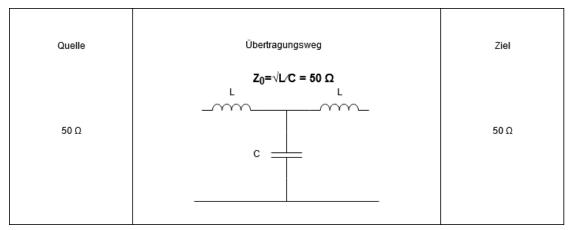

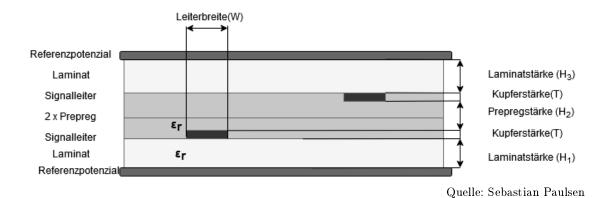

#### 2.7.2 Impedanzen

Differentielle Signalleiterbahnen müssen in einer vom Übertragungsstandard vorgegebenen Weise verlegt werden, damit sie resistent gegen äußere Einflüsse sind. Dabei sind die Leiterbahnbreite, die Dicke und die umliegenden Schichten für die Impedanz der Leitung entscheidend. Die folgende Grafik2.11 zeigt die Aufteilung der Impedanzen vom Sender bis zum Empfänger.

Quelle: Sebastian Paulsen

Abbildung 2.11: Grafik Impedanzen Aufteilung Empfänger Sender Leitung

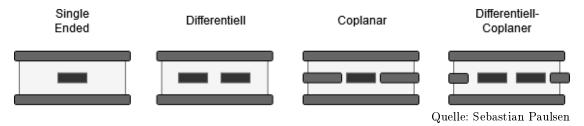

Differentielle Signale nutzen je nach Art der Übertragung unterschiedliche einheitliche Impedanzen. Beispielsweise verwendet Ethernet  $50\,\Omega[9]$ . Für die Impedanz einer Leitung betrachtet man die folgenden unterschiedlichen Impedanzklassen, die sich nach dem Ort des Bezugspotenzial unterscheiden. [Vgl. S.108-115, 26]

Single Ended Impedance Die Impedanz ergibt sich durch die Anordnung eines einzelnen Leiters über einem oder zwischen zwei Bezugspotenzialen. [S.110, 26]

**Differential Impedance** Die Impedanz ergibt sich durch zusammengehörige (differenzielle) Signale in zwei parallel zueinander verlaufenden Leitern, die in Referenz zu Bezugspotentialen stehen. [S.110, 26]

Coplanar Impedance Die Impedanz ergibt sich durch einen Leiter, der in eine Potenzialfläche eingebettet ist, bezüglich einer Referenz zu einem oder zu zwei Bezugspotenzialen. [S.110, 26]

**Differential-Coplanar Impedance** Die Impedanz ergibt sich durch zusammengehörige (differenzielle) Signale in zwei parallel verlaufenden Leitern, die in Potenzialflächen eingebettet sind, mit Referenz zu einer oder zu zwei Bezugspotenzialen. [S.110, 26] Folgende Formel resultiert daraus für die Impedanz.

Abbildung 2.12: Grafik unterschiedlicher Impedanzklassen

Die Impedanzklassen werden weiter in Impedanztypen unterteilt, die sich durch die Lage zu den Potenzialen auszeichen:

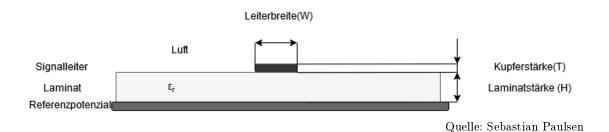

Microstrip Die Signalleitung ist über einem Potenzial angeordnet. [Vgl. S.110, 26]

Stripline Die Signalleitung liegt zwischen zwei Potenzialen. [Vgl. S.110, 26]

#### Surface Microstrip

Abbildung 2.13: Surface Microstrip

$$Z_0 = \frac{60}{\sqrt{\varepsilon_{eff}}} \cdot ln\left(\frac{5,98H}{0,8W+T}\right) \cdot \Omega$$

mit

$$\varepsilon_{eff} = 0,475\varepsilon_r + 0,67$$

#### Embedded Microstrip

Quelle: Sebastian Paulsen

Abbildung 2.14: Embedded Microstrip

$$Z_0 = \frac{60}{\sqrt{\varepsilon_{eff}}} \cdot ln\left(\frac{5,98H_1}{0,8\,\mathrm{W} + T}\right) \cdot \Omega$$

$_{

m mit}$

$$\varepsilon_{eff} = \varepsilon_r \left( 1 - e^{\frac{-1,55(H_1 + H_2)}{H_1}} \right)$$

#### Single Stripline symmetrisch

Abbildung 2.15: Single Stripline symmetrisch

$$Z_0 = \frac{60}{\sqrt{\varepsilon_r}} \cdot \ln\left(\frac{1,9(2H+T)}{0.8\,\mathrm{W}+T}\right) \cdot \Omega$$

#### Single Stripline asymmetrisch

Quelle: Sebastian Paulsen

Abbildung 2.16: Single Stripline asymmetrisch

$$Z_0 = \frac{80}{\sqrt{\varepsilon_r}} \cdot \ln\left(\frac{1,9(2H_1 + T)}{0,8 \,\mathrm{W} + T}\right) \cdot \left(1 - \frac{H_1}{4H_2}\right) \cdot \Omega$$

bei  $H_1 \leq H_2$

#### **Dual Stripline**

Abbildung 2.17: Dual Stripline

$$Z_0 = \frac{80}{\sqrt{\varepsilon_r}} \cdot \ln\left(\frac{1,9(2H_1 + T)}{0.8 \,\text{W} + T}\right) \cdot \left(1 - \frac{H_1}{4(H_2 + H_3 + T)}\right) \cdot \Omega$$

Der Hauptgrund die Leitungen an die Impedanzen anzupassen sind Reflexionen auf der Leitung bei sehr schnellen Signalen[Vgl. S.1117f, 9]. Nach den theoretische Grundlagen wird nun mit dem Forschungsstand fortgeführt.

# 3 Forschungsstand

Der Forschungsstand soll einen Überblick über momentane Entwicklungen im Bereich der autonomen Miniaturfahrzeuge geben.

### 3.1 Faller & DC-Car-System

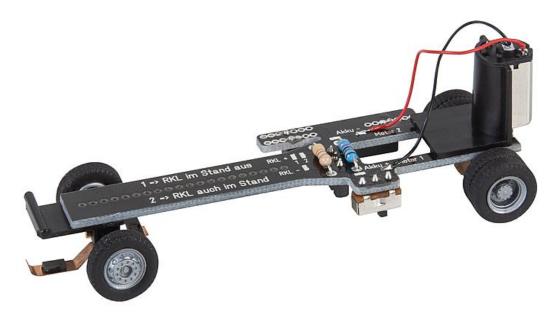

Es werden nun zwei Hersteller von selbstfahrenden Fahrzeugen im H0-Standard vorgestellt. Das Fallersystem sowie das DC-Car System verfolgen das Ziel, Modellfahrzeuge im H0 Standard über eine Modelllandschaft fahren zu lassen. Die Steuerung wird mit einem Fahrzeug realisiert, dass eine durch einen Elektromotor angetriebene Hinterachse besitzt und dessen Vorderachse mit einem kleinen Magneten ausgestattet ist. Mithilfe von Elektromagneten unter der Fahrbahn wird die Vorderachse in eine vorgegebene Richtung abgelenkt. So kann der Magnet und damit auch das Fahrzeug der Spur folgen oder je nach Schaltung der Elektromagnete auch Abbiegen und Kreuzungen befahren. Die Steuerung des Elektromotors für die Hinterachse wird von einem Funkmodul in dem Fahrzeug getätigt, das wiederum mit einem weiteren Funkmodul in einem Controller verbunden ist. Dieser Controller ist an einen Computer angeschlossen. Dieses Setup ermöglicht es mehrere Fahrzeuge gleichzeitig zu steuern. Nun im Folgenden Abbildungen 3.1 einer der Fahrzeuge, der jeweiligen Hersteller.

$\label{eq:Quelle:https://www.faller.de/xs_db/BILD_-DB/1/161/www/750/161484_fg_01.jpg} DB/1/161/www/750/161484_fg_01.jpg$

Quelle: http://www.h0-car-action.de/WIM/911-1.png

(a) Fahrzeug Faller

(b) Fahrzeug DC-Car

Abbildung 3.1

Als Erweiterung zu dem Faller-System besitzen die Fahrzeuge im DC-Car-System noch einen Abstandssensor, der nach Vorne ausgerichtet ist. Mithilfe des Abstandsensors kann das Fahrzeug Hindernisse erkennen und davor stoppen.

### 3.2 Selbstfahrendes Fahrzeug mit externer Prozesseinheit

Zunächst wird ein Ansatz betrachtet der ein Fahrzeug mit externer Prozesseinheit vorstellt.

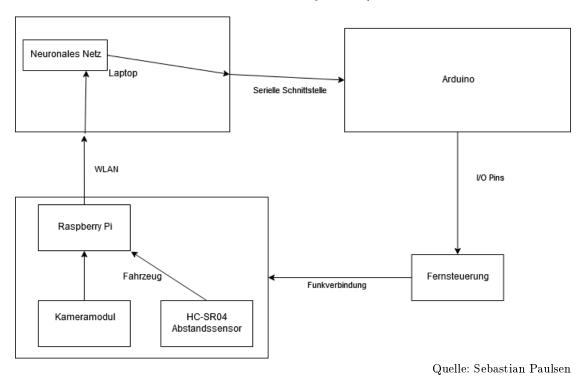

Der folgende Ansatz 3.2 von Zheng Wang ist ein kleines selbstfahrendes Auto, das die Sensordaten von Abstandsensor und Kamera via WLAN vom Fahrzeug an einen Laptop sendet. Auf dem ferngesteuerten Fahrzeug ist ein HC-SR04 Abstandssensor, ein Raspberry Pi model B+, die Raspberry Pi Kamera und eine Powerbank verbaut. Der Raspberry PI ist mit einer Kamera über ein Flachbandkabel über die MIPI Schnittstelle verbunden. Der Abstandsensor ist mit dem Raspberry PI über vier Kabel verbunden. Zudem werden die Ausgänge VCC für die Spannungsversorgung, GND für die Masse, Trigger als Input und Echo als Output an den Raspberry PI angeschlossen. Der Raspberry PI initiiert eine Messung, indem er den Triggerpin umschaltet und wartet dann auf die Spannungsflanke der Echo-Leitung. Aus der Laufzeit lässt sich der Abstand ermitteln. Die Komponenten für die Steuerung des ferngesteuerten Modellfahrzeugs sind in ihrem ursprünglichen Zustand gelassen worden. Auf dem Laptop läuft ein TCP/IP Server, der die Daten an

das OpenCV und ein neuronales Netz weiterleitet, die Daten interpretiert und die Steuerungsbefehle an das Fahrzeug zurückleitet. Dies wird dadurch realisiert, dass die Daten vom Laptop über eine serielle Schnittstelle an einen Arduino gesendet werden, der mit seinen Pins direkt an die Fernsteuerung angeschlossen ist, die serielle Befehle interpretiert und das ferngesteuerte Fahrzeug damit steuert. [Vgl. 22]

Abbildung 3.2: Architektur Projekt Zheng Wang

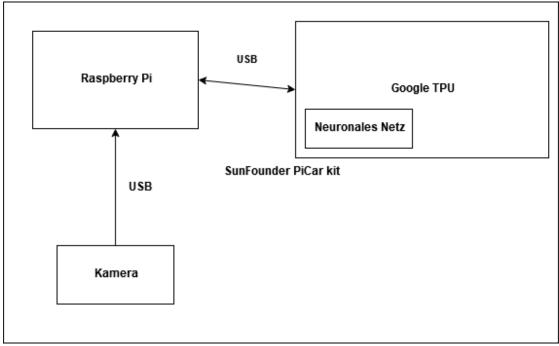

# 3.3 Selbstfahrendes Fahrzeug mit integrierter Prozessoreinheit

Gegenüber dem vorangegangenen Ansatz verfolgt dieser Ansatz 3.3 von David Tian den Weg die Prozessoreinheit in Form einer Google-Tensor Processing Unit (TPU) und eines Raspberry PIs auf dem Fahrzeug (SunFounder PiCar kit) zu realisieren. Die Google-TPU ist via USB an den Raspberry PI angeschlossen. Die Kamera wird an den Raspberry PI ebenfalls via USB angeschlossen. Hier wird das OpenCV-Framework in Kombination mit dem Tensor Flow-Tool von Google verwendet, um die Kameradaten zu interpretieren

und die Steuerungsimpulse zu generieren. Durch die TPU werden bis zu 12 Bildern pro Sekunde verarbeitet und interpretiert. Würde nur der Raspberry PI die Verarbeitung erledigen, läge die Verarbeitungsgeschwindigkeit nur bei einem Bild pro Sekunde. [Vgl.

Quelle: Sebastian Paulsen

Abbildung 3.3: Architektur PiCar

21] Mit diesem Überblick über einen Teil des Forschungsstandes wird mit dem Konzept fortgeführt.

# 4 Konzept

Dieses Konzept teilt das Ziel, eine Hardware für ein weitgehend autonomes Miniaturfahrzeug zu entwickeln, in kleinere Teile auf. Aus den Teilzielen werden Anforderungen

generiert und diese werden im Folgenden analysiert, evaluiert und konkretisiert. Im ersten Schritt wird das generelle Fahrzeugkonzept eingegrenzt. Im zweiten Schritt wird die

Größe des Fahrzeugs festgelegt gefolgt vom dritten Schritt bei dem der Ort der Datenverarbeitung bestimmt wird. Im vierten Schritt wird die Auswahl der berechnenden

Hardware getätigt und zuletzt im fünften Schritt wird die Peripherie der berechnenden

Hardware gewählt.

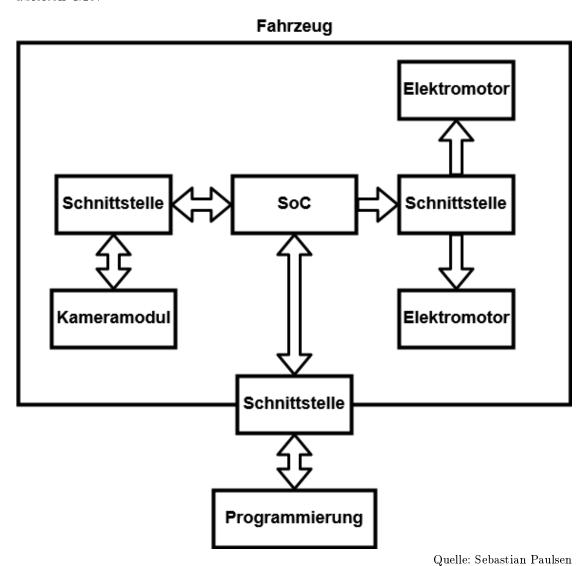

### 4.1 Autonomes Fahrzeug

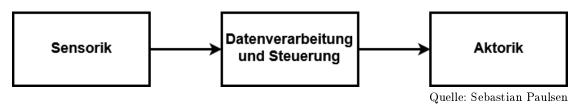

Diese Arbeit beschränkt sich nur auf das Steuern von zweiachsigen Fahrzeugen mit Elektromotoren als Aktoren und mit Digitalkameramodulen als Sensoren. Für das Fahrzeug bedeutet dies, es erfasst die Umgebung mit Hilfe von Sensoren, bildet diese ab und bewegt sich darin mit Aktoren fort. Als Verbindung und Verarbeitung zwischen der Sensorik und der Aktorik benötigt ein autonomes Fahrzeug eine Intelligenz, welcher es möglich sein sollte, die Sensordaten zu interpretieren und die Aktoren zu steuern. Die zweidimensionale Steuerung des Fahrzeugs wird auf zwei Elektromotoren aufgeteilt, einer der Elektromotoren ist für die Lenkung und der andere ist für den Antrieb zuständig.

Abbildung 4.1: Konzept Autonomes Fahren mit Sensorik-Prozessor-Aktorik

### 4.2 Fahrzeugabmaße

Im zweiten Schritt wird eine Größe für das Fahrzeug festgelegt und die daraus resultierenden Anforderungen evaluiert. Es bietet sich an, eine Größe zu wählen, in der es bereits Entwicklungen gibt, mit denen man das Fahrzeug vergleichen kann und die eigene Arbeit somit daran anknüpfen kann. Es wird der 1:87 H0 Standard gewählt, denn dieser ermöglicht durch die weite Verbreitung im Modellbau und die Auswahl an Fahrzeugen eine Referenzmöglichkeit. Außerdem ist ein Bausatz für ein Chassis im H0-Standard bereits im Rahmen der Hochschule vorhanden und kann für diese Arbeit benutzt werden.

Aufgabe ist es nun, zu analysieren, wie viel Platz in einem Modellfahrzeug, mit einem Verhältnis von 1:87(H0), für die Sensoren, Aktoren und Intelligenz vorhanden ist.

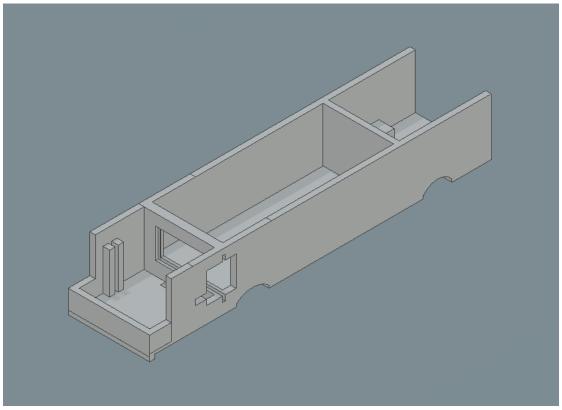

#### 4.2.1 Erweiterung des Chassis - Design und Herstellung

Der Faller-Bausatz "Car System Chassis-Kit"hat keine Möglichkeit die Bauteile zu befestigen, daher wird ein 3D-Modell erstellt, dass auf das vorhandene Chassis aufgesetzt werden kann. Doch um das 3D-Modell zu erstellen, müssen die Abmaße bestimmt werden.

|                    | Bus                 | Gigaliner Zugmaschine | Gigaliner Auflieger |

|--------------------|---------------------|-----------------------|---------------------|

| Breite             | $31~\mathrm{mm}$    | $28  \mathrm{mm}$     | 28 mm               |

| ${ m H\ddot{o}he}$ | 42  mm              | $30  \mathrm{mm}$     | $30  \mathrm{mm}$   |

| Länge              | $137 \mathrm{\ mm}$ | $85 \mathrm{\ mm}$    | $160~\mathrm{mm}$   |

Tabelle 4.1: Messung der Größen von H0 Bus und Gigaliner

Referenz Messung im Miniaturwunderland Für die Ermittlung der maximal zulässigen Abmaße für das Fahrzeug im Modellbau mit dem Standard H0 werden Messungen im Miniatur Wunderland durchgeführt, welche diesen Standard verwenden. Im Miniatur Wunderland besteht die größte zusammenhängende Modellanlage der Welt. Im Rahmen der Zielsetzung dieser Arbeit wurde der Fokus auf die größten Modelle im Miniatur Wunderland gelegt, um im Rahmen des H0-Standards den größtmöglichen Platz im 3D-Modell zu erhalten. Die folgenden Abbildungen 4.3 4.4 zeigen die gemessenen Modelle.

$Quelle: \ http://www.modellbahn-alstertal.de/WebRoot/Store21/Shops/62437818/4B88/1531/9777/D586/45FE/C0A8/2936/00FE/156646-1.jpg$

Abbildung 4.3: H0 Gigaliner

Die Abmessungen aus der Messung werden nun mit einem Bus in Originalgröße verglichen, um die gemessenen Werte zu verifizieren Als Vergleich wird ein Bus der Firma Mercedes Benz herangezogen. Dieser hat eine Breite von 2550 mm eine Länge von 12135 mm und Höhe von 3400 mm. Dies entspricht bezogen auf den H0 Standard:

$$\frac{2,550\,\mathrm{mm}}{87} \approx 30\,\mathrm{mm}\ Breite$$

$$\frac{12{,}135\,\mathrm{mm}}{87}\approx140\,\mathrm{mm}\ L\ddot{a}nge$$

$$\frac{3,400\,\mathrm{mm}}{87}\approx39\,\mathrm{mm}\ H\ddot{o}he$$

[S.4, 8]

Die Messungen werden von der Berechnung bestätigt. Mit diesen Abmessungen des Busses kann das 3D-Modell erstellt werden.

CAD Modell Für das Zeichnen des Chassis wird mit der Software Inventor von Autodesk gearbeitet. Diese erlaubt es Zeichnungen zu erstellen und zu exportieren um die Zeichnungen dann mit einem 3D-Drucker zu realisieren. In das Design des Modells wird das Faller-Chassis mit aufgenommen und Platz für die Chassisgrundplatte gelassen. Im Chassis-Set enthalten ist ein DC-Motor für den Antrieb der Hinterachse. Für die Steuerung der Vorderachse wird ein vorhandener Servomotor verwendet. Dieser muss so platziert werden, sodass er mit der Lenkerstange der Vorderachse verbunden werden kann. Außerdem wird im vorderen Bereich des 3D-Modells eine Halterung für eine Kamera eingebaut. Als Vorlage wird hierfür die Raspberry PI Kamera verwendet.

Abbildung 4.5: CAD-Zeichnung des Chassis

Zur Überprüfung der Ergebnisse wird im Miniatur Wunderland noch eine Gegenüberstellung von dem H0 Bus und dem erstellen Modell getätigt.

Abbildung 4.6: Gegenüberstellung 3D-Modell mit H0 im Miniatur Wunderland

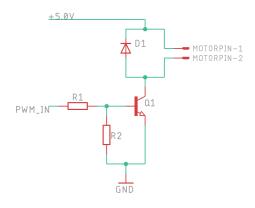

Elektronische Steuerung Für die realistische Ermittlung des vorhandenen Platzes für die Platine im Modell wird auch die elektrische Schaltung zum Betrieb des Fahrzeuges realisiert. Dafür wird eine Schaltung entwickelt, die die Ansteuerung des DC-Motors mit einem Pulsweitenmodulationssignal ermöglicht. Dies ist notwendig, da die I/O-Ports von Platinen zwar die benötigte Spannungen liefern aber nicht den benötigten Strom.

Abbildung 4.7: Schaltung PWM-Steuerung

Nach dem Einsetzen der Schaltung, der Kamera und der Motoren in das Fahrzeug wird der Platz für die Hardware in der Umsetzung des 3D-Modells vermessen. Vermessung des inneren Kerns beträgt:

- 64 mm Länge

- 18 mm Tiefe

Ergebnis der Evaluation des Chassis Dadurch, dass die Wände noch entfernt bzw. versetzt oder der DC-Motor gedreht werden kann, wird auf die Länge des inneren Kerns, 12 mm addiert.

Die maximal verfügbare Gesamtlänge im Inneren des Fahrzeugs für die Platine beträgt 76 mm. Die maximal verfügbare Gesamttiefe beträgt in Folge dieser Messungen 18 mm. Die maximal verfügbare Gesamtehöhe beträgt 31 mm

### 4.3 Verarbeitung der Kameradaten

Im dritten und nun folgenden Schritt wird die Verarbeitung der Kameradaten betrachtet. Um die Kameradaten zu analysieren und zu interpretieren, bietet es sich an, ein neuronales Netz zu verwenden. Wie in den theoretischen Grundlagen erläutert, ermöglichen es

trainierte neuronale Netze, Bilder zu interpretieren. So sollen zum Beispiel die Straßenführung oder auch Straßenschilder erkannt werden. Aus diesen Interpretationen lassen sich Steuerimpulse für die Aktorik generieren.

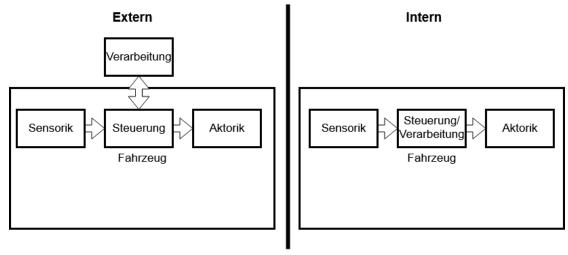

### 4.3.1 Datenverarbeitung im Fahrzeug oder extern

Wie bereits im Forschungsstand beschrieben, gibt es zwei unterschiedliche Ansätze, wie in einem autonomen Fahrzeug die Kameradaten interpretiert werden.

Beim ersten Ansatz wird das Fahrzeug nicht direkt von der Hardware auf dem Fahrzeug gesteuert, sondern sendet die Bilder der Kamera über W-LAN an einen Computer. Der Computer leitet die Bilder nach der Übertragung an die Eingangsschicht eines trainierten neuronalen Netzes weiter. Dieses neuronale Netz verarbeitet die Bilder auf dem Computer und ermittelt die Steuerimpulse daraus, die an das Fahrzeug zurück übermittelt werden.

Beim zweiten Ansatz wird die Verarbeitung der Bilder mithilfe eines neuronalen Netzes auf dem Fahrzeug selber ausgeführt. Dies vermeidet die Übertragung der Daten vom Fahrzeug zum Computer und erlaubt es, die Steuerimpulse direkt an die Aktorik zu leiten.

Evaluierung der Ansätze Die Vorteile des ersten Ansatzes zeichnen sich dadurch aus, dass die Hardware auf dem Fahrzeug nur die Übertragung der Kameradaten und die Steuerung der Aktorik ausführen muss. Dies ermöglicht eine kompaktere Bauform und ermöglicht es, durch die Rechenleistung des Computers sehr viele Daten zu verarbeiten, welche nur durch die Übertragungsgeschwindigkeit gedrosselt werden.

Die Vorteile des ersten Ansatzes bestehen darin, dass die Übertragungszeiten zwischen den einzelnen Komponenten des Aufbaus relativ gering sind, sodass im Gegensatz zum Ansatz mit externer Hardware keine Übertragungsprotokolle implementiert werden müssen und, dass keine externe Hardware benötigt wird.

Der Nachteil des ersten Ansatzes ergibt sich aus der Übertragung der Daten vom Fahrzeug zum Computer. Diese können durch Interferenzen gestört werden oder abbrechen, weil die Übertragungsdistanz zwischen den beiden Komponenten zu groß wird. Der Nachteil des zweiten Ansatzes besteht darin, dass die Umsetzung im Vergleich zum ersten Ansatz komplexer ist und weniger Rechenleistung als beim ersten Ansatz vorhanden ist. Die Visualisierung der beiden Ansätze kann in der folgenden Grafik betrachtet werden 4.8.

Quelle: Sebastian Paulsen

Abbildung 4.8: Ansatzübersicht

Ergebnis der Evaluation Der zweite Ansatz wird gewählt, denn dieser verspricht durch die fehlende Datenübertragung eine geringere Fehleranfälligkeit und macht externe Hardware gegenstandslos.

#### 4.3.2 Auswahl der verarbeitenden Hardware

Neuronale Netze benötigen durch die Menge an Multiplikationen und Additionen eine enorme Rechenleistung und werden deswegen, neben CPU und GPU, häufig auch auf spezialisierter Hardware wie beispielsweise Application-Specific Integrated Circuits (ASIC) implementiert. Im Folgenden werden die Komponenten FPGA, CPU und GPU nach ihrer Fähigkeit ein neuronales Netz zu Implementieren evaluiert.

tinyTPU Ein vielversprechender Ansatz für ein neuronales Netz implementiert dieses auf einem SoC. Der SoC besteht hier aus einem FPGA und einen dual-core Mikrocontroller. Dieser Ansatz macht sich die Rechenleistung der Digital Signal Processor (DSP)-

Blöcke auf dem FPGA des SoCs zu nutze. Genauer verwendet dieser Ansatz das Z-turn Board mit dem Xilinx XC7Z020 SoC, welches einen FPGA und einen Mikrocontroller integriert hat [6].

#### Evaluierung der Hardwareoptionen

In [18] werden CPU, GPU und FPGA mithilfe des Min-Warping Algorithmus miteinander verglichen. Der Min-Warping-Algorithmus ist mit seiner parallelen Datenverarbeitung für einen Vergleich zwischen paralleler Hardware geeignet. Dabei wird besonders auf die Energieeffizienz und die Rechenleistung geachtet. Die Implementation auf dem FPGA wird hier wie in [6] mit Hilfe der DSP-Blöcke realisiert. Im niedrigen Leistungsbereich ist der FPGA schneller und effizienter als CPU und GPU. Eine weiter Publikation die diese These stützt ist [1]

Ergebnis der Evaluation Die Wahl fällt auf den FPGA integriert mit einem Mikrocontroller auf einem SoC, da der FPGA im Vergleich energieeffizienter und leistungsstärker ist.

### 4.3.3 Training von neuronalen Netzen

Neuronale Netze benötigen Training mit aufwändigen Lernalgorithmen, die auf kompakten Systemen zu Speicherplatzproblemen führen können. Es bietet sich daher an, das Training des neuronalen Netzes auf einem externen Rechner zu tätigen und das trainierte Netz zu übertragen. Dies ist, unter dem Gesichtspunkts des Speicherbedarfs der Trainingsdaten betrachtet, eine elegante Lösung, die es vermeidet, Lernalgorithmen wie genetische Algorithmen implementieren zu müssen und Speicherplatz auf dem SoC zu verbrauchen.

#### 4.3.4 Boardauswahl oder eigene Platine

Nachdem der FPGA bzw. der SoC als verarbeitende Hardware festgelegt wird, wird im vierten Schritt nun die Frage nach der umliegenden Peripherie geklärt.

Vorstellung der Ansätze Ein Ansatz wäre es, bereits vorhandene Boards zu verwenden, auf denen der Xilinx XC7Z020 SoC aus [6] verwendet wird. Es gibt mehrere Evaluationsboards, die diesen SoC verwenden, wie z.B. das PYNQ-Board von Digilent, das TE0720 von Trenz Elektronik oder das ZED-Board von AVNET. [14]

Ein zweiter Ansatz wäre es, eine eigene Platine zu designen und fertigen zu lassen, die den Platzanforderungen entspricht.

Als dritter Ansatz wäre es möglich, die Funktionalität unterschiedlicher Boards mit einer Trägerplatine zu verbinden, beispielsweise werden dabei die Steuerung des Fahrzeugs und das Interpretieren der Kameradaten auf zwei Boards aufgeteilt.

Evaluierung der Ansätze Der letzte vorgestellte Ansatz fällt aus der Auswahl, da die Wahl der Hardware auf einen SoC fiel und somit das gesamte Projekt auf diesem SoC umgesetzt werden muss, ist keine weitere Berechnungshardware notwendig, weil der SoC bereits die Möglichkeiten bietet, die die Trägerplatine gehabt hätte.

Der Vorteil des ersten Ansatzes besteht darin, dass von den Herstellern bereits getestete und funktionierende Hardware zur Verfügung gestellt wird. Die Peripherie der Boards wird nach der Möglichkeit, eine Kamera anzuschließen, untersucht:

| Board  | Peripherie                                                                               | Breite           | Länge             |

|--------|------------------------------------------------------------------------------------------|------------------|-------------------|

| PYNQ   | HDMI in, Ethernet, I/O Ports,<br>USB OTG, PMOD                                           | 8,7 cm           | $12,2\mathrm{cm}$ |

| Z-Turn | USB OTG, Ethernet,<br>2x 1,27 mm pitch 80-pin SMT female connectors                      | $6,3\mathrm{cm}$ | $10,2\mathrm{cm}$ |

| Trenz  | 2x B2B connector Samtec Razor Beam LSHM-150,<br>B2B connector Samtec Razor Beam LSHM-130 | $4\mathrm{cm}$   | $5\mathrm{cm}$    |

Tabelle 4.2: Peripherie Vergleich

[14] [3] Das Trenz-Board hat keine Peripherie und es ist nötig, ein Trägerboard zu entwickeln, deswegen fällt dieses Board auch aus der Auswahl wie der zu letzt genannte Ansatz. Sowohl das PYNQ-Board sowie das ZED-Board ermöglichen das Anschließen einer Kamera, jedoch ist das ZED-Board wesentlich kleiner als das PYNQ-Board und daher zu präferieren.

Der Nachteil des ersten Ansatzes ist es jedoch, dass die Boards nicht die Platzanforderungen erfüllen. Die recherchierten Boards sind zu groß für das Modell.

Der zweite Ansatz hat den Vorteil, dass die Auswahl der Peripherie gänzlich den Anforderungen angepasst werden kann und sie deswegen sehr flexibel ist.

Der zweite Ansatz hat hingegen den Nachteil, dass die Entwicklung von eigener Hardware aufwändiger ist.

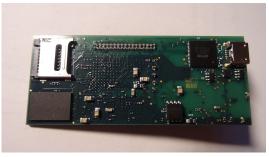

Ergebnis der Evaluation Die Argumente sprechen für den zweiten Ansatz, da dieser Flexibilität bietet, dies ist beim zweiten Ansatz durch vorhandene Bauteile bereits eingeschränkt und überschreitet nicht die Platzanforderung.

### 4.4 Pipelinekonzeption

Im fünften Schritt nun ein Ansatz der in die Zielsetzung integriert wird. Der Vorteil einer Pipeline ist es, dass die Aufgabe in kleinere Unteraufgaben aufgeteilt werden können, welche parallel von dedizierten Komponenten bearbeitet werden können. Dies wird nun auf die Problemstellung der Verarbeitung großer Datenmengen angewandt. Daher werden nun aus der Problemstellung Teilaufgaben und Schnittstellen definiert. Die Prozesseinheit wird aufteilt in das Verarbeiten der Kameradaten und die Ansteuerung der Motoren. Das Verarbeiten der Kameradaten wird weiter aufgeteilt in Kameradaten empfangen, Kameradatenvorverarbeiten (Filter), Kameradaten analysieren, Kameradaten interpretieren und die Ergebnisse weiterleiten. Die Steuerung teilt sich in das Empfangen von Ergebnissen, das Umwandeln von Ergebnissen in Steuerimpulse und das Ausführen von Steuerimpulsen auf. Die Konzeption wird in folgender Grafik zusammengefügt 4.9.

### Pipeline Konzept

Abbildung 4.9: Pipelineüberblick Sensorik zu Aktorik

### 4.5 Weitere Anforderung an die Platine

Weitere Funktionen, die nicht zwingend für die bisherigen Anforderungen nötig sind, stellen die Folgenden Punkte dar. Weitere Fähigkeit des SoCs ist die Möglichkeit auf dem Mikrocontrollern ein Betriebssystem zu verwenden, doch das Betriebssystem benötigt allerdings Arbeitsspeicher und persistenten Speicher. Mit unterschiedlichen Bootmedien (persistenter Speicher und interner Speicher) wird die Auswahl des Bootmediums vor dem Start des Bootloaders zwingend. Die Ausführung des gewählten Bootmediums übernimmt ein Bootloader. Dieser muss während des Bootvorgangs bereits das gewählte Medium kennen. [Vgl. S.170, 24] Daraus folgend werden in die Architektur ein Speichermedium, ein Arbeitsspeicher und eine Möglichkeit, dem Bootloader die Auswahl mitzuteilen, integriert.

### 4.6 Zusammenfassung des Konzepts

Es wird eine Platine entwickelt, die an zwei Elektromotoren angeschlossen ist und die Elektromotoren zu steuern vermag - Dabei ist die Leistungselektronik extern realisiert und nicht Teil des Konzepts der Platine. Desweiteren ist auf der Platine ein SoC verbaut, der über eine Übertragungsschnittstelle an eine Kamera angeschlossen ist. Die Daten werden von der Übertragungsschnittstelle zu einem im FPGA des SoC implementierten neuronalen Netz weitergeleitet und interpretiert. Aus den interpretierten Daten sollen dann Steuerimpulse generiert werden, die an die Elektromotoren weitergeleitet werden. Ferner soll der SoC außerhalb der Platine programmiert werden können und die gesamte Platine soll die für die Funktionen benötigten Spannungen aus einer Gleichspannung generieren können.

Darüber hinaus soll die Platine folgende Abmaße haben und somit in ein Modellautomobil im H0 Standard passen:

- Länge 76 mm

- Breite 18 mm

- Höhe 31 mm

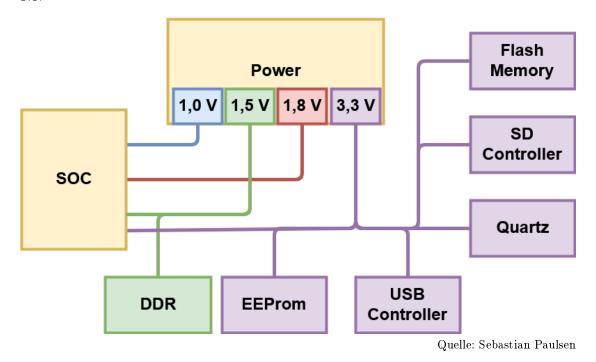

## 4.7 Architektur des Konzepts

Aus dem Konzept und den Anforderungen lässt sich folgende Grafik der Architektur ableiten 4.10.

Abbildung 4.10: Architektur des Konzepts

# 5 Umsetzung

Maßgeblich für die Umsetzung ist die Wahl des SoCs als Prozessoreinheit sowie der verwendete SoC in der Realisierung des neuronalen Netztes aus [6]. Die Umsetzung gliedert sich in zwei Teile, zum einen in die Entwicklung des Schaltplans und zum anderen in den Platinenentwurf. Im Gegensatz zum Platinenentwurf, der nicht aufgeteilt ist, wird der Schaltplan beim Hinzufügen eines Bauteils Stück für Stück erweitert.

Damit nicht die gesamte Platine neuentwickelt werden muss, werden für die Umsetzung diverse im Handel erhältliche Platinen als Referenz genommen.

Eagle Im Weiteren wird die für Studenten frei erhältliche Version 9.4.2 von Eagle für das Zeichnen der Schaltpläne und die Erstellung des Platinenentwurfs verwendet.

### 5.1 Auswahl des SoC-Modells

Xilinx vertreibt neben dem Z-7020 auch leistungsstärkere SoCs die denselben Aufbau haben wie der Z-7020. Sodass der nächst größere SoC der Z-7030 verwendet werden könnte, ohne Anpassungen am neuronalen Netz oder der Struktur der Umgebung des neuronalen Netzes vornehmen zu müssen.

### 5.1.1 Vergleich Xilinx Z-7020 mit Xilinx Z-7030

Die signifikanten Daten der SoCs in einer Tabelle zusammengefasst

|                 | Z-7020          | Z-7030           |

|-----------------|-----------------|------------------|

| LUTS            | 53,200          | 78,600           |

| Flip Flops      | 106,400         | 157,200          |

| DSP Blöcke      | 220             | 400              |

| BlockRAM Memory | 4,9 Mb          | $9,3\mathrm{Mb}$ |

| Abmaße          | $17\mathrm{mm}$ | $23\mathrm{mm}$  |

Tabelle 5.1: Vergleich Z-7020 mit Z-7030 [Vgl. S.2 23]

Die Anzahl der für das neuronale Netz wichtigen Bestandteile, wie der DSP Blöcke oder des BlockRAMs, sind auf dem Z-7030 fast doppelt vorhanden. Mit diesen signifikanten Vorteilen, im Hinblick auf das neuronale Netz, ist die größere Bauform des Z-7030 zu vernachlässigen und der Z-7030 zu verwenden.

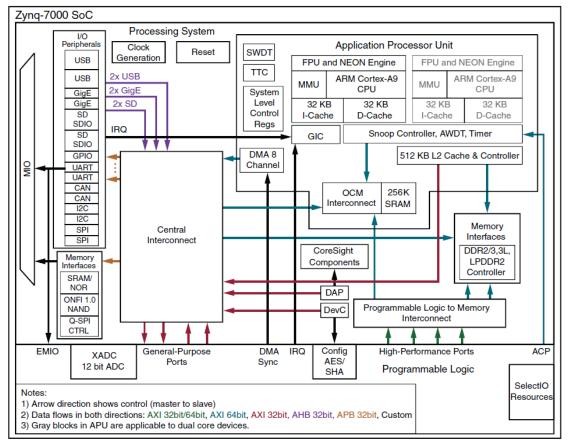

### 5.2 Xilinx Z-7030

Der Z-7030 wird in zwei Bereiche unterteilt, die Programmable Logic (PL) und das Programming System (PS). Im Grunde genommen entspricht die PL dem FPGA und das PS dem Mikrocontroller.

Quelle: [23, S.27]

Abbildung 5.1: Block Diagram

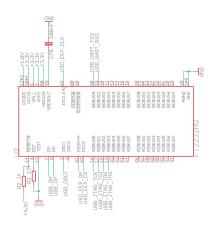

### 5.2.1 IO und Controller

Im Folgenden werden einige Aspekte des Z-7030 vorgestellt.

**AXI** AXI steht für Advanced eXtensible Interface, es verbindet die einzelnen Komponenten des SoCs miteinander und ermöglicht die Ansteuerung von den gleichen I/O Pins aus der PL sowie aus dem PS. Dies vollzieht sich in einem Master-Slave-System, welches mit SPI vergleichbar ist. [24]

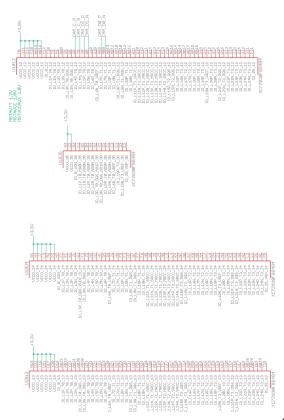

MIO Multiplexed I/Os (MIO) ermöglichen es die selben I/O-Pins durch multiplexing an das PS oder die PL zu binden. Diese sind besonders vielseitig, da sie intern an un-

terschiedliche im SoC vorhandene Controller wie CAN, SPI, I2C angeschlossen werden können. Eine Übersich über die verbauten Controller und die MIO Pins folgen in dieser Grafik 5.2.

| MIO Voltage Bank 0                                                      | MIO Voltage Bank 1 Package Bank 501                                                  |                                                                                     |                                                                         |  |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|

| Package Bank 500                                                        | MIO VOITage Bank I Package Bank 501                                                  |                                                                                     |                                                                         |  |

| 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5                                         | 1   1   1   1   2   2   2   2   2   2                                                | 2 2 3 3 3 3 3 3 3 3 3 3 3 3 8 9 0 1 2 3 4 5 6 7 8 9                                 | 4 4 4 4 4 4 4 4 4 4 5 5 5 5 5 0 1 2 3 4 5 6 7 8 9 0 1 2 3               |  |

|                                                                         | Pins not available in<br>7z010 and 7z007s CLG225 devices                             |                                                                                     | Pins not available in<br>7z010 and 7z007s<br>CLG225 devices             |  |

| BOOT_MODE The 20k ohm Boot Mode                                         | Ethernet 0                                                                           | Ethernet 1                                                                          | MDIC                                                                    |  |

| Device pll V are sampled at Reset.                                      | tx tx data tx rx rx data rx                                                          | tx data tx rx rx data rx                                                            | ck d                                                                    |  |

| Quad SPI 0 Quad SPI 1                                                   |                                                                                      | USB 0                                                                               | USB 1                                                                   |  |

| cs cs io io io io o s fb s io io io io<br>1 0 0 1 2 3 clk ckclk 0 1 2 3 |                                                                                      | da dir st nx<br>ta data ck data                                                     | da dir st nx<br>ta dir p t data ck data                                 |  |

| SPI 1,0 SPI 1<br>molmil . lsslsslss                                     | SPI 0 SPI 1                                                                          | SPI 0 SPI 1                                                                         | SPI 0 SPI 1                                                             |  |

| SPI   mo mi   ck   ss   ss   ss   ss   ss   ss   ss                     | ck mi ss ss ss momo mi ck ss ss ss ss<br>so 0 1 2 si si ss so 0 1 2<br>SDIO 0 SDIO 1 | ck mi ss ss ss momomi ck ss ss ss ss<br>so 0 1 2 si si so ck 0 1 2<br>SDIO 0 SDIO 1 | ck mi ss ss ss momomi ck ss         |  |

| CDIO C                                                                  |                                                                                      |                                                                                     |                                                                         |  |

|                                                                         | ck m 0 1 2 3 0 m ck io io io io d d ck 1 2 3                                         | ck m 0 1 2 3 0 m ck 10 io io io d ck 1 2 3                                          | ck m 0 1 2 3 0 m ck 1 2 3                                               |  |

| SD Card Detect and Write Prof                                           | tect are available in any of the s                                                   | haded positions in any combina                                                      | tion of the four signals.                                               |  |

| 0 1 2 3 4 5 6 9 10 11 12 13 14 15                                       | 16 17 18 19 20 21 22 23 24 25 26 27                                                  | 28 29 30 31 32 33 34 35 36 37 38 39                                                 | 40 41 42 43 44 45 46 47 48 49 50 51 52 53                               |  |

| SD Card Power Controls are av                                           | ailable on an odd/even pin basi                                                      | s that corresponds to SDIO cont                                                     | trollers 0 and 1.                                                       |  |

| 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1                                         |                                                                                      | 0 1 0 1 0 1 0 1 0 1 0 1                                                             | 0 1 0 1 0 1 0 1 0 1 0 1 0 1                                             |  |

| SMC interface choice: NOR/SRA                                           | M or NAND Flash                                                                      |                                                                                     |                                                                         |  |

| o te data oe bis data da ta                                             | address                                                                              | [0:24]                                                                              | NOR/SRAM MIO Pin 1 is optional:<br>addr 25, cs 1 or gpio                |  |

| cs alewe io io io io de rd io 4 ~ 7 io bu 3 sy                          | io 8 ~ 15                                                                            | NAND Flas                                                                           | h                                                                       |  |

| 0 1 2 3 4 5 6 7 8 9 1 1 1 1 1 1 1                                       | 1 1 1 1 2 2 2 2 2 2 2 2 2 2 6 7 8 9 0 1 2 3 4 5 6 7                                  | 2 2 3 3 3 3 3 3 3 3 3 3 3 8 9 0 1 2 3 4 5 6 7 8 9                                   | 4 4 4 4 4 4 4 4 4 4 5 5 5 5 5 0 1 2 3 4 5 6 7 8 9 0 1 2 3               |  |

| CAN 0 rx tx rx tx                                                       | nxtx nxtx nxtx                                                                       | rx tx rx tx rx tx                                                                   | nx tx nx tx nx tx                                                       |  |

| 1   tx   rx   tx   rx                                                   | tx rx tx rx tx rx                                                                    | tx rx tx rx                                                                         | tx rx tx rx tx rx tx rx                                                 |  |

| CAN External Clocks are optionally a                                    | avaliable on any pin in any comi                                                     | omation                                                                             |                                                                         |  |

| UART 0 rx tx rx tx                                                      | rx tx rx tx rx tx                                                                    | rx tx rx tx rx tx                                                                   | rx tx rx tx rx tx                                                       |  |

| 1 tx rx tx rx                                                           | tx rx tx rx tx rx                                                                    | tx rx tx rx tx rx                                                                   | tx rx tx rx tx rx tx rx                                                 |  |

| 12C 0   ck d   ck d   ck d                                              | ck d         ck d         ck d           ck d         ck d         ck d              | ck d         ck d         ck d           ck d         ck d         ck d             | ck d         ck d         ck d           ck d         ck d         ck d |  |

| System TTC 0 Clk In, Wave Out                                           | w ck                                                                                 | w ck                                                                                | w ck                                                                    |  |

| Timers TTC 1 Clk In, Wave Out SWDT Clk In. Reset Out ck r               | w ck ck r                                                                            | w ck ck r                                                                           | w ck r ck r ck r                                                        |  |

| GPIOs are available for each MIO                                        |                                                                                      |                                                                                     |                                                                         |  |

| 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15                                   | •                                                                                    | 2                                                                                   | *                                                                       |  |

| PJTAG Interface   t t t t di do ck ms                                   | t t t t<br>di do ckms                                                                | t t t t<br>di do ck ms                                                              | tttt<br>didockms                                                        |  |

| ck ctl                                                                  | ck ctl                                                                               | Clock and Control                                                                   | Trace Port User Interface                                               |  |

| 8 9 10 11 12 13 14 15 2 3 0 1                                           | 4 5 6 7 2 3 0 1                                                                      | Data                                                                                |                                                                         |  |

Quelle: [24, S.52]

Abbildung 5.2: MIO Übersicht

#### 5.2.2 LVDS

Low Voltage Differential Signaling(LVDS) ist eine Form der seriellen Datenübertragung. Der SoC besitzt zwei verschiedene Varianten, die mit den Spannungen 2,5 V oder 1,8 V betrieben werden.

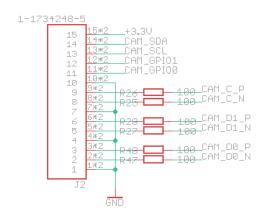

### 5.3 Kamerainterface

Der Xilinx Z-7030 SoC hat diverse Schnittstellen für den Anschluss von Kameras wie z.B. USB OTG oder Ethernet. Desweiteren besitzt er LVDS. Diese erlauben es, Interfaces zu implementieren, die nicht direkt mit einem der internen Controller funktionieren. So wie auch das MIPI D-PHY Interface, dass im Mobiltelefon- und Industriebereich, wie z.B. im Raspberry PI eingesetzt wird und weit verbreitet ist. Für die D-PHY Schnittstelle gibt es im Xilinx-IP-Store einen IP-Core den man käuflich erwerben kann. Der Vorteil dieses Interfaces gegenüber den anderen besteht in der großen Anzahl von passenden Geräten und die hohe Übertragungsgeschwindigkeit von mehreren giga bits per second (gbps).

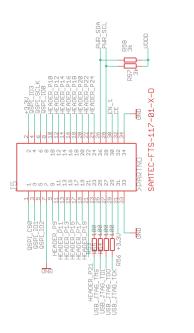

### 5.3.1 Pinbelegung Kamera Header

Aus den MIPI Bestimmungen wird also folgender Header genommen.

Quelle: Sebastian Paulsen

Abbildung 5.3: Pin Belegung

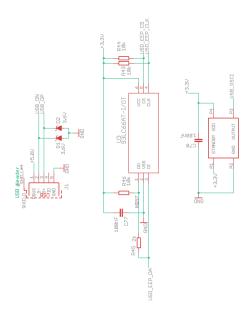

### 5.4 Programmierung des SoC

Nach der Auswahl des SoC besteht der nächste Schritt darin, diesen zu programmieren. Der SoC besitzt eine JTAG-Schnittstelle, die mit vier Pins an Peripherie nach außen gelegt werden kann.

### 5.4.1 USB-Chip

Der Chip 2232HQ der Firma Future Technology Devices International (FTDI) verbindet mehrere Funktionen in einem Gerät. Dies spart Platz auf der Platine, erschwert allerdings aufgrund der damit verbundenen Komplexität die Konfiguration des Bauteils. Der USB-Chip verfügt über diverse Schnittstellen:

- USB zu dual UART

- USB zu dual FIFO

- USB zu dual JTAG

- USB zu dual SPI

- USB zu dual  $I^2C$

- USB zu Kombination aus zwei Genannten [Vgl. S.1 12]

Das bedeutet, dass der Benutzer die Möglichkeit hat über ein Micro-USB Kabel das Gerät via JTAG zu programmieren, eine serielle Verbindung damit aufzubauen, zu Debuggen und die Platine mit Strom zu versorgen.

### 5.4.2 Konfiguration des USB-Chips

Der FTDI-Chip benötigt zum Speichern der unterschiedlichen Konfigurationen einen EEPROM-Speicher, der an seine EEPROM-Pins angeschlossen wird. Als EEPROM wird ein 93LC66 verwendet. Dieser wird im Manual des USB-Chips aufgeführt.

### 5.5 Persistenter Speicher des SoC

Für das neuronale Netz wird Speicherplatz für die Bias und Gewichte benötigt. Desweiteren benötigt der Linuxkernel einen Mindestspeicherplatz von 4 Mb. Die Lösung wäre eine SD Karte als persistentes Speichermedium zu verwenden.

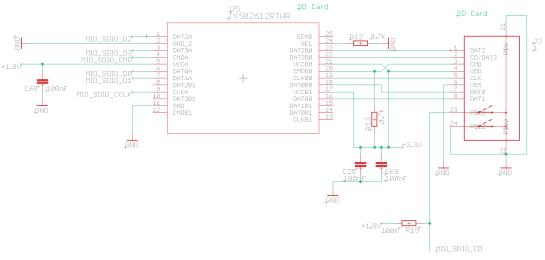

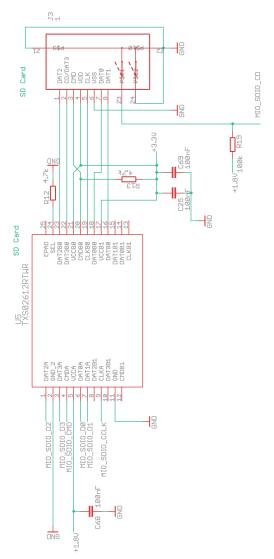

### 5.5.1 SD-Chip

Um die SD Karte benutzen zu können muss sie angesteuert werden, dies geschieht durch einen SD Karten Controller der als Bindeglied zwischen SD-Kartenslot und SoC agiert. Der SD Karten Chip ist mit den MIO Pins 41-45, 46 und der internen SD Schnittstelle des SoCs dem SDIO Controller verbunden. [Vgl. S.366, 24] Dies wird in der folgenden Grafik dargestellt 5.4.

Quelle: Sebastian Paulsen

Abbildung 5.4: SD Chip Symbol

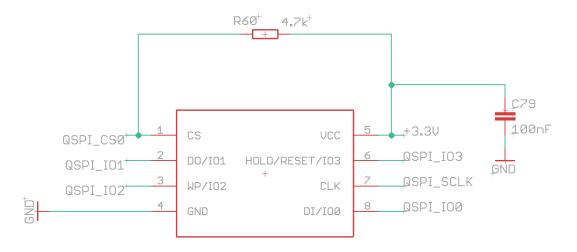

### 5.5.2 Flashspeicher

Der FPGA des SoCs verliert nach Abschalten der Versorgungsspannung seine Konfiguration. Sobald man den FPGA außerhalb des Setups, mit direkter Verbindung zum PC via USB Kabel betreiben möchte, wird daher persistenter Speicher notwendig. Ein Ansatz ist es, den FPGA seine Konfiguration von einem Flashspeicher laden zu lassen. Dieser behält auch nach dem Abschalten der Versorgungsspannung seine Daten bei und kann wiederholt programmiert werden. Die Auswahl des Speichers ist von dessen Platzbedarf, dessen Speichergröße und dessen Möglichkeit der schnellen Übertragung via QSPI abhängig. Deswegen wird der W25Q128JVSIQ verwendet. Hier der Schaltplan 5.5.

Quelle: Sebastian Paulsen

Abbildung 5.5: W25Q128JVSIQ

### 5.6 Auslagerungsspeicher - DRAM