# Bachelorarbeit

Erik Andresen

Implementierung einer digitalen Regelung auf einem FPGA basierten System on Chip unter FreeRTOS

## Erik Andresen

# Implementierung einer digitalen Regelung auf einem FPGA basierten System on Chip unter FreeRTOS

Bachelorarbeit eingereicht im Rahmen der Bachelorprüfung im Studiengang Technische Informatik am Department Informatik der Fakultät Technik und Informatik der Hochschule für Angewandte Wissenschaften Hamburg

Durchgeführt bei ESW GmbH, Wedel Betreuer: Dipl.-Ing. M. Fischer

Betreuender Prüfer: Prof. Dr.-Ing. B. Schwarz

Zweitgutachter: Prof. Dr.-Ing. F. Korf

Abgegeben am 24. November 2008

#### Erik Andresen

#### Thema

Implementierung einer digitalen Regelung auf einem FPGA basierten System on Chip unter FreeRTOS

#### **Stichworte**

System on Chip, Xilinx Virtex-4 FX12 FPGA, Microblaze Mikrocontroller, FreeR-TOS, Digitale Regelung, harte Echtzeit

#### Kurzzusammenfassung

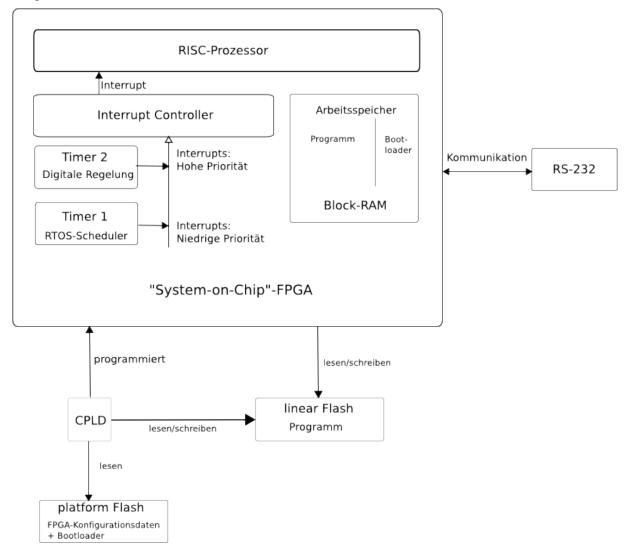

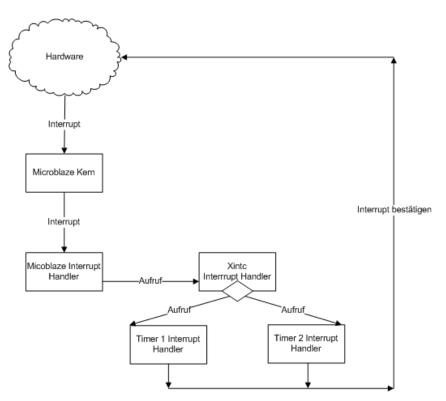

Im Rahmen dieser Bachelorarbeit wurde ein FPGA mit Microblaze Prozessor IP-Core als System On Chip dazu eingerichtet, alle  $100\mu s$  eine digitale Regelung parallel zu dem Echtzeitbetriebssystem FreeRTOS mit dazu parallel laufenden Tasks auszuführen. Jeweils ein Timer mit Interrupt für die Regelung, sowie das Betriebssystem sorgen dafür, dass beide exakt ausgeführt werden. Da der Microblaze über genau einen Interrupt-Eingang verfügt, wurde noch ein Interrupt-Controller dazwischen geschaltet. Die zeitkritischere Regelung erhält am Interrupt-Controller die höhere Priorität. Zusätzlich prüft ein für den Microblaze angepasster Bootloader zunächst, ob über die RS-232 Schnittstelle ein neues Programm heruntergeladen werden soll. Wenn nicht, wird das Hauptprogramm aus dem Flash-Speicher in den Arbeitsspeicher geladen und ausgeführt.

#### Erik Andresen

## Title of the paper

Implementation of a digital control on a FPGA based System on Chip running FreeR-TOS

### **Keywords**

System on Chip, Xilinx Virtex-4 FX12 FPGA, Microblaze microcontroller, FreeR-TOS, digital Control, hard Real-Time

#### **Abstract**

Within the scope of this bachelor thesis an FPGA with Microblaze Processor IP-Core as System On Chip has been configured to execute every  $100\mu s$  a digital control in parallel to the real time operation system FreeRTOS with running tasks. A Timer for each, the digital control and the operation system make sure that both are executed accurately. Since the Microblaze has exactly one interrupt pin an interrupt controller has been added. The more time-critical digital control gets the higher priority at the interrupt controller. Furthermore an adapted Bootloader for the Microblaze initially tests if there is a program to download over the RS-232 interface. If not, the main program is loaded from the Flash into the main memory and executed from there.

# **Inhaltsverzeichnis**

| 1 | Einle<br>1.1 | <b>eitung</b><br>Ziel. Ii | ndustrielle | Anwendung und Hintergrund                         | <b>7</b><br>7 |

|---|--------------|---------------------------|-------------|---------------------------------------------------|---------------|

|   |              |                           |             |                                                   |               |

| 2 |              |                           |             | und Software                                      | 10            |

|   | 2.1          |                           |             | Development Kit                                   | 10            |

|   | 2.2          | Ubersi                    | icht zur FF | PGA-Peripherie des Xilinx ML403 Evaluation Board  | 11            |

| 3 | Übe          | rsicht z                  | u den Reç   | gelungsfunktionen                                 | 13            |

|   | 3.1          | Model                     | l der Rege  | elung zur Stabilisierung der Höhe von Plattformen | 13            |

|   | 3.2          | Schnit                    | tstellen de | r Regelung                                        | 14            |

| 4 | Der          | Microbl                   | aze Mikro   | controller                                        | 15            |

|   | 4.1          | Grund                     | struktur de | es Microblaze Mikrocontrollers                    | 15            |

|   |              | 4.1.1                     | Der RIS     | C-Prozessor mit Harvard-Architektur               | 15            |

|   |              |                           | 4.1.1.1     | Ausnahmen                                         | 17            |

|   |              |                           | 4.1.1.2     | Cache                                             | 17            |

|   |              |                           | 4.1.1.3     | Fließkommaeinheit                                 | 17            |

|   |              |                           | 4.1.1.4     | Header-Dateien und Treiber des Microblaze         | 18            |

|   |              | 4.1.2                     | Bussyste    | eme des Microblaze: FSL, LMB und PLB              | 18            |

|   |              |                           | 4.1.2.1     | Fast Simplex Link                                 | 18            |

|   |              |                           | 4.1.2.2     | Der Local Memory Bus                              | 18            |

|   |              |                           | 4.1.2.3     | Der Processor Local Bus                           | 19            |

|   |              | 4.1.3                     | Speicher    | am Microblaze: Block-RAM und Flash                | 19            |

|   |              |                           | 4.1.3.1     | Der Block-RAM                                     | 19            |

|   |              |                           | 4.1.3.2     | BRAM Interface Controller                         | 20            |

|   |              |                           | 4.1.3.3     | Externer Speicherzugriff                          | 20            |

|   |              | 4.1.4                     | Peripher    | ie des Microblaze                                 | 21            |

|   |              |                           | 4.1.4.1     | Das Timer/PWM-Modul                               | 21            |

|   |              |                           | 4.1.4.2     | Der Interrupt Controller                          | 23            |

|   |              |                           | 4.1.4.3     | Ein- und Ausgabe                                  | 26            |

|   |              |                           | 4.1.4.4     | Asynchroner serieller Datenstrom: RS-232          | 26            |

|   |              |                           | 4.1.4.5     | MDM Debug Module                                  | 26            |

|   |              |                           | 4.1.4.6     | Clock Generator                                   | 27            |

|   |              |                           | 4.1.4.7     | Prozessor System Reset-Module                     | 27            |

|   |              |                           | 4.1.4.8     | Utility Bus Split                                 | 28            |

|   | 4.2          | Speich                    | er und Ad   | lressen des Microblaze                            | 28            |

| 5 | Free         | RTOS                      |             |                                                   | 30            |

|   | 5.1          | Das Fı                    | eeRTOS.o    | org Projekt                                       | 30            |

|   | 5.2          |                           |             |                                                   | 30            |

|   | 5.3          |                           |             | RTOS-Sourcecodes                                  | 31            |

|   | 5.4          |                           |             |                                                   | 32            |

Inhaltsverzeichnis 5

|    | 5.5   |          | OS Tasks                                                       | 32 |

|----|-------|----------|----------------------------------------------------------------|----|

|    | 5.6   |          | sk-Kommunikation                                               | 33 |

|    | 5.7   | Implem   | nentierung auf dem Microblaze                                  | 33 |

| 6  |       | _        | n der Microblaze-Hardware für die Anwendungen                  | 34 |

|    | 6.1   | Übersic  | cht der verwendeten Hardware                                   | 34 |

|    | 6.2   | Eingese  | etzte Komponenten                                              | 34 |

|    |       | 6.2.1    | Prozessor: Microblaze                                          | 34 |

|    |       | 6.2.2    | Memory Bus: LMB                                                | 36 |

|    |       | 6.2.3    | Peripherie Bus: PLB                                            | 37 |

|    |       | 6.2.4    | Programmspeicher: BRAM                                         | 37 |

|    |       | 6.2.5    | Visualisierung: LEDs                                           | 37 |

|    |       | 6.2.6    | Zeitmessung: Timer                                             | 38 |

|    |       | 6.2.7    | Interrupt Controller xintc                                     | 38 |

|    |       | 6.2.8    | Kommunikation mit PC: RS-232 Uart                              | 38 |

|    |       | 6.2.9    | Flash Massenspeicher: Multi-CHannel External Memory Controller | 39 |

|    |       |          | Flash Massenspeicher: Utility Bus Split                        | 39 |

|    |       | 6.2.11   | Taktgenerator: Clock Generator                                 | 40 |

|    |       |          |                                                                | 40 |

|    | ( )   |          | Reset Modul                                                    | _  |

|    | 6.3   | Kompie   | ette Belegung der Hardware Ressourcen                          | 41 |

| 7  |       |          | ungen Regelung, FreeRTOS und der Bootloader                    | 43 |

|    | 7.1   |          | gelung                                                         | 43 |

|    |       | 7.1.1    | Implementation im Microblaze                                   | 43 |

|    |       | 7.1.2    | Timer und Interrupt                                            | 43 |

|    |       | 7.1.3    | Regelungsfunktionen parallel zu den FreeRTOS Tasks             | 44 |

|    | 7.2   | Interrup | pt Hierarchie                                                  | 45 |

|    | 7.3   | Der Bo   | otloader für die Anwendungssoftware                            | 45 |

| 8  | Erge  | bnisse ı | und Messtechnische Analyse                                     | 47 |

|    | 8.1   | Messur   | ng der Regelung                                                | 47 |

|    |       | 8.1.1    | Maximale Ausführungszeit der Regelung                          | 47 |

|    |       |          | 8.1.1.1 Aufbau der Messung                                     | 47 |

|    |       |          | 8.1.1.2 Ergebnis der Messung                                   | 48 |

|    |       | 8.1.2    | Jitter der Regelung                                            | 49 |

|    |       |          | 8.1.2.1 Ergebnis der Messung                                   | 49 |

|    | 8.2   | Verwen   | ndete FPGA Ressourcen                                          | 50 |

|    |       | 8.2.1    | Alle Hardware Optimierungen                                    | 50 |

|    |       | 8.2.2    | Vorkonfigurierter Microblaze mit FPU                           | 51 |

|    |       | 8.2.3    | Vorkonfigurierter Microblaze mit FPU, 3 Stage Pipeline         | 51 |

|    |       | 8.2.4    | Ausführung aus einem externem Speicher                         | 51 |

|    |       | 8.2.5    | Zusammenfassung                                                | 51 |

|    | 8.3   |          |                                                                | 52 |

|    | 0.5   |          | nanz von FreeRTOS parallel zur Regelung                        |    |

|    |       | 8.3.1    | Aufbau der Messung                                             | 52 |

|    |       | 8.3.2    | Ergebnis der Messung                                           | 52 |

| 9  | Zusa  | mmenfa   | assung                                                         | 53 |

| 10 | Liter | aturverz | zeichnis                                                       | 54 |

Inhaltsverzeichnis 6

| A | A.1  | Grundl  | für FreeRTOS einrichten agen des Embedded Development Kit |    |

|---|------|---------|-----------------------------------------------------------|----|

| В | Free | RTOS f  | ür Microblaze patchen                                     | 62 |

|   | B.1  | Datei p | oortasm.s                                                 | 62 |

|   |      | _       | oort.c                                                    | 62 |

|   |      | B.2.1   | Funktion xPortStartScheduler()                            | 62 |

|   |      | B.2.2   | Timer Konfiguration, Funktion prvSetupTimerInterrupt()    | 62 |

|   |      | B.2.3   | vTaskISRHandler                                           | 63 |

|   |      | B.2.4   | Demo Applikation                                          | 63 |

| С | Boot | tloader | Konfiguration                                             | 65 |

| D | Foto | ML403   |                                                           | 67 |

# 1 Einleitung

# 1.1 Ziel, Industrielle Anwendung und Hintergrund

Für die Luft-, Bahn- und Fahrzeugtechnik werden von der ESW GmbH Mechatronische Systeme entwickelt, bei denen Elektrotechnik, Maschinenbau und Informatik zusammenarbeiten. Hier kommt oftmals eine Regelung zum Einsatz, die auf Basis von Mikrocontrollern und Field Programmable Gate Arrays (FPGAs)[19] realisiert wird. Während FPGAs durch hohe Parallelverarbeitung komplexe Aufgaben schneller[18] erledigen, sind Mikrocontroller einfacher zu programmieren, weswegen es oftmals kostengünstiger ist, einen Mikrocontroller und einen FPGA zu benutzen, anstatt nur einen FPGA in einer Hardwarebeschreibungssprache wie VHDL[2] oder Verilog zu programmieren[3].

Seit einiger Zeit gibt es Mikrocontroller wie den Xilinx[20] Microblaze als Softcore für den FPGA. Dies erlaubt dem Entwickler, einen FPGA wie einen Prozessor in der Programmiersprache C zu programmieren.

Ein Softcore[21], auch Intellectual Property (IP)-Core, ist ein wiederverwendbarer Schaltplan der entweder als Quellcode oder als bereits für die Hardware synthetisierte Netzliste existiert. Der Microblaze als Softcore existiert also ausschließlich in den Logikblöcken des FPGA und nicht als Physische Hardware.

Durch die Integration des Mikroprozessors in den FPGA hinein, wird der FPGA selber zum Ein-Chip-System: "System on Chip" (SoC). System on Chip bedeutet, daß elektronische Bauteile wie Prozessoren, Speicher und Peripherie, in einem vereint werden[1].

Die Vorteile des FPGA mit Mikrocontroller als System on Chip sind:

- **Kosteneinsparung und Miniaturisierung**: Durch die Reduzierung der Anzahl elektronischer Bauteile wird das Board kleiner.

- Anpassungsfähigkeit an Anforderungen: Der Hardware Entwickler kann jede Kombination an Peripherie wählen. Er kann sogar neue Peripherie erstellen und diese direkt an die CPU anschließen.

- **Hardware Beschleunigung**: Komplexe Aufgaben, die durch Parallelverarbeitung beschleunigt werden müssen, können in einer Hardwarebeschreibungssprache realisiert, an den Mikroprozessor angebunden werden, ohne einen extra Baustein auf die Platine zu löten[18].

- Obsoleszenz: Einige Firmen, vor allem militärische Zulieferer, müssen eine lange Produkt-Lebenserwartung garantieren, die länger als die eines Standard elektronischen Produktes ist. Elektronische Komponenten wie Mikrocontroller sind oftmals schon nach wenigen Jahren nicht mehr erhältlich was eine Anpassung an das Nachfolgemodell erforderlich macht. IP-Cores sind jedoch vom FPGA unabhängig. Tauscht man den FPGA gegen das Nachfolgemodell aus müssen die IP-Cores lediglich neu kompiliert werden[3].

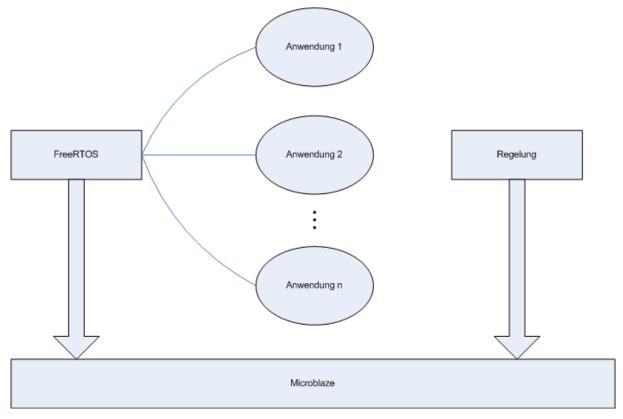

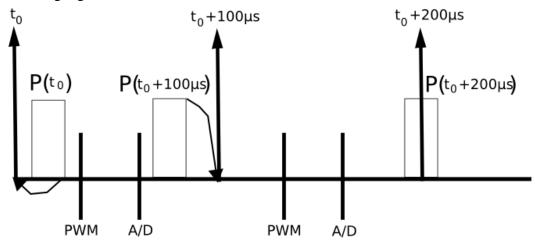

Im Rahmen dieser Bachelorarbeit soll untersucht werden, ob der FPGA als System On Chip in der Lage ist, ein Echtzeitbetriebssystem mit Anwendungen und alle  $100\mu$ s eine CPU-Intensive digitale Regelung zusammen auszuführen (vgl. Abb. 1.1).

Die Digitale Regelung soll innerhalb der 100µs ausgeführt werden und dabei muss noch aus-

1 Einleitung 8

reichend Rechenzeit für das Echtzeitbetriebssystem zur Verfügung stehen. Für beide parallel laufenden Anwendungen darf außerdem die Echtzeitfähigkeit nicht verletzt werden. Ist die maximale Laufzeit oder der Jitter der Regelung zu hoch, dann greift z.B. eine Bremse zu spät, was zu unzulässigen Folgen führen kann. Zusätzlich soll ein für den Microblaze angepasster Bootloader zunächst prüfen, ob über die RS-232 Schnittstelle ein neues Programm heruntergeladen werden soll. Wenn nicht, wird das Hauptprogramm in den Arbeitsspeicher geladen und ausgeführt.

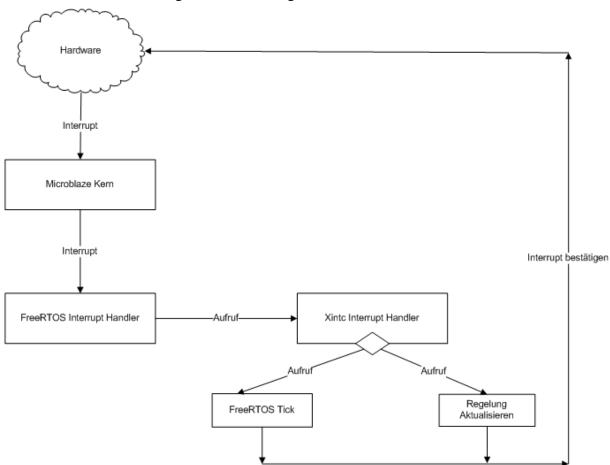

**Abb.** 1.1: Überblick über das Komplettsystem

Zuerst lädt der CPLD die FPGA-Konfigurationsdaten aus dem "platform Flash" und schreibt sie in den FPGA. Die Konfigurationsdaten enthalten den kompletten Microblaze System-on-Chip, sowie den Bootloader. Anschließend liest der Bootloader das Hauptprogramm aus "linear Flash" und speichert es in den Arbeitsspeicher. Für das Programm gibt es einen zum Bootloader separaten Arbeitsspeicher. Die rechtzeitige Ausführung der Regelung und die Unterbrechung für den FreeRTOS-Scheduler wird mit jeweils einem Timer-Interrupt erzeugt. Da für die Regelung höhere Anforderungen an die Echtzeitfähigkeit gestellt werden, erhält deren Timer am Interrupt Controller die höhere Priorität.

Diese Arbeit beginnt mit den Grundlagen von FreeRTOS und dem Microblaze Mikrocontroller, es folgt deren Konfiguration und schließlich die Analyse ob alle Anforderungen erfüllt worden sind:

1 Einleitung 9

• Beginnen wird diese Arbeit mit einem Überblick über die Entwicklungsumgebung und verwendete Hardware, das ML403 Board von Xilinx sowie der digitalen Regelung.

- Im dritten Kapitel wird der Microblaze Mikrocontroller mit dessen Eigenschaften, Merkmalen, Fähigkeiten und den für diese Arbeit benötigten Bussysteme sowie Peripherie vorgestellt.

- Das dritte Kapitel befasst sich mit dem Echtzeitbetriebssystem FreeRTOS, dessen Kernel, Vorgehensweise und Aufbau. Es endet mit einer Beschreibung, wie eine typische Anwendung für FreeRTOS erstellt wird.

- Das fünfte Kapitel dokumentiert, wie welche Hardware eingesetzt wurde, um die Ziele dieser Bachelorarbeit zu erreichen.

- Das sechste Kapitel befasst sich mit der Umsetzung des Reglers im Microblaze und geht auf das Zusammenspiel mit FreeRTOS ein.

- Die Aufgabe des siebten Kapitels ist die Analyse, ob alle Anforderungen von dem Microblaze erfüllt wurden und vergleicht die Ausführungsgeschwindigkeit mit einem physischen Mikrocontroller. Es werden unterschiedliche Konfigurationsvarianten des Microblaze Prozessors untersucht und wie sie sich auf die Ausführungsgeschwindigkeit auswirken.

Den Schluss bildet eine Zusammenfassung dieser Bachelorarbeit im achten Kapitel. Vielen Dank an die Firma Xilinx für das Bereitstellen vieler Grafiken.

# 2 Übersicht zur Hard- und Software

Hier wird ein Überblick zum ML403 Board gegeben, für das die Hard- und Software dieser Arbeit erstellt wurde.

# 2.1 Das Embedded Development Kit

Das Xilinx Embedded Development Kit (EDK) enthält die Entwicklungsumgebungen Platform Studio und Platform Studio SDK, sowie verschiedene IP-Cores, wie den Microblaze, aber auch Speicher-Steuerungen für Flash, DDR-SDRAM und SRAM, Peripherie wie Timer, Interrupt Controller, RS-232 und viele weitere mehr, die den Microblaze Prozessor zu einem Mikrocontroller aufrüsten. Vorkompiliert und optimiert für alle Xilinx FPGAs, vom kleinen Spartan 3 bis zum großen Virtex 5 ist der Microblaze im Xilinx Embedded Development Kit als verschlüsselte Netzliste enthalten. Die Lizenz erlaubt es den Microblaze in einer unbegrenzten Anzahl FPGAs der Firma Xilinx einzusetzen. Der Einsatz in anderen FPGAs muss mit Xilinx extra verhandelt werden. Der VHDL-Quellcode ist von Xilinx erhältlich. Für die meisten IP-Cores sind die VHDL- und C-Quellcodes im EDK enthalten.

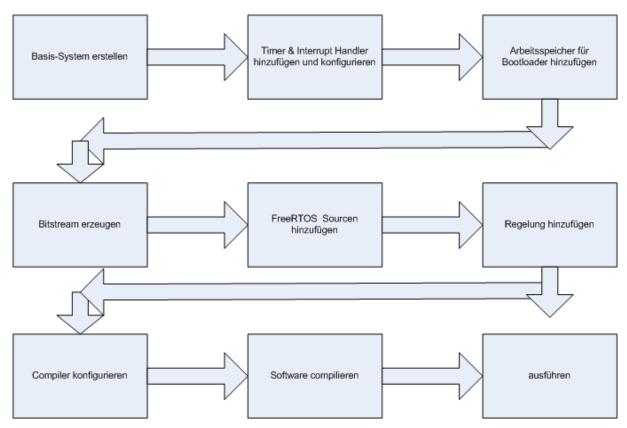

Das Platform Studio enthält alle nötigen Funktionen zur Hard- und Softwareentwicklung. Zur Synthese der Hardware wird dabei auf die ISE Design Tools zurückgegriffen. Das Platform Studio enthält Assistenten um IP-Cores dem eigenen System hinzuzufügen und hilft bei der Erstellung von eigenen IP-Cores. Zum kompilieren des C-Quellcode wurde der C-Compiler des GNU Projektes[17] von Xilinx auf den Microblaze portiert. Für ein Projekt wird zuerst die Hardware mit Peripherie erstellt und zur system.bit-Bitstream kompiliert. Das Erstellen der Basis-Hardware kann mit einem Assistenten erfolgen. Spätere Änderungen an der Hardware können im EDK über ein grafisches Interfaces oder durch manuelles Editieren der Dateien erledigt werden. Anschließend wird die Software kompiliert und zusammen mit der Hardware-Bitstream zu der download.bit-Bitstream gepackt, mit der der FPGA programmiert wird.

Das Platform Studio SDK ist eine auf Eclipse[4] basierte Entwicklungsumgebung, die zur reinen Softwareentwicklung verwendet werden kann. Gegenüber dem Platform Studio sind im SDK Funktionen enthalten, die dem Entwickler beim Software Projekt Management, Navigation und Suche im Quellcode und bei der Versionskontrolle unterstützen.

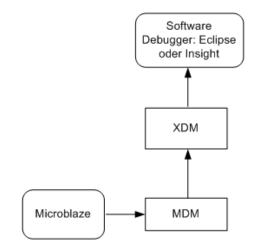

Zum Debuggen benutzen beide Entwicklungsumgebungen den Debugger des GNU Projektes, GDB, der zur Kommunikation mit der Hardware auf die Xilinx Microprocessor Debug Engine (XMD) zugreift. Als Frontend greift das Platform Studio auf die grafische Debug-Oberfläche Insight[11], das SDK auf den in den Eclipse integrierten Debugger zurück.

# 2.2 Übersicht zur FPGA-Peripherie des Xilinx ML403 Evaluation Board

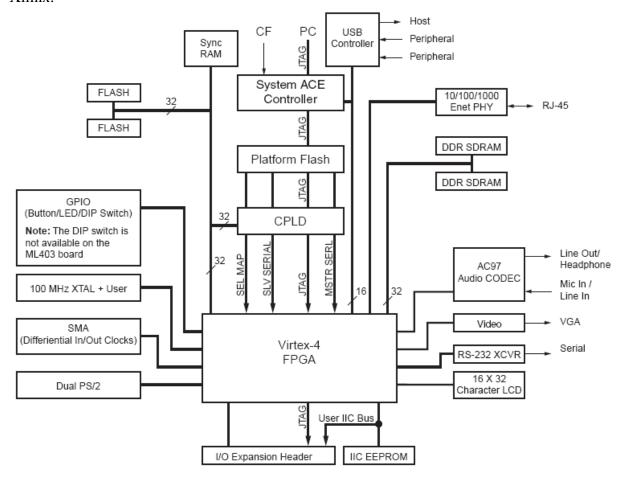

Als Grundlage dieser Arbeit dient das Virtex-4 ML403 Embedded Platform Board D.1 von Xilinx.

Abb. 2.1: ML403 Blockschaltbild

Es verfügt über folgende Peripherieelemente:

• Xilinx Virtex-4 XC4VFX12 FPGA mit eingebautem PowerPC Hardcore Prozessor: Der FX12-FPGA ist der kleinste der für eingebettete Systeme optimierten Virtex-4 FX Reihe. Er verfügt über einen eingebauten PowerPC Prozessor, 81kB Block-RAM, 5.472 Slices, 12.312 Logik Zellen, 12.312 Flip Flops und 320 I/O-Pins.

#### • Xilinx XC95144XL CPLD:

Da der Xilinx XC95144XL CPLD mit den Flash Speichern und den FPGA Konfigurations Pins verbunden ist wird er benutzt, um den FPGA mit Daten aus den verschiedenen Flash Speichern zu programmieren.

• Xilinx XCF32P Platform Flash Konfigurations-Speicher:

Der Platform Flash speichert die Bitstream-Konfigurationsdaten für den FPGA und damit den Microblaze Mikrocontroller sowie den Bootloader.

#### • 8MB Linear Flash, Intel StrataFlash Kompatibel:

Zwei 16Bit 4MB linear Platform Flash Speicher des Typ Micron "MT28F320J3RG-11 ET" sorgen für einen totalen Speicher von 8MB. Da der Flash den Speicher Bus mit dem

SRAM teilt können nicht gleichzeitig beide Speichertypen verwendet werden. Der lineare Flash speichert das Anwendungsprogramm, also die Regelung zusammen mit FreeRTOS.

#### • RS-232 Anschluss:

Der Serielle-Anschluss nach den EIA-232 Standard kann eine Geschwindigkeit von bis zu 115200 Baud erreichen. Zur Kommunikation wird ein Nullmodem-Kabel (Pin 2 und 3 gekreuzt) verwendet. Da nur die RX und TX Pins angeschlossen sind, kann kein Hardware-Flow verwendet werden.

- Schalter, Knöpfe, verschiedene LEDs. Es stehen 4 LEDs zur Verfügung, die zur Visualisierung benutzt werden können.

- JTAG Port Ermöglicht das Debuggen per Platform Cable USB oder Parallel Cable IV. Er kann auch benutzt werden, um den FPGA, CPLD oder Flash zu programmieren.

- 64MB DDR SDRAM

- Oszillator Fassungen, 100MHz Oszillator vorinstalliert

- Differenzial Takt Ein- und Ausgänge über SMA Verbinder

- 16 Zeichen x 2 Zeilen LCD

- Zwei 3x32 Pin Erweiterungsschnittstellen.

- Stereo AC97 Kodierer-Dekodierer

- 4kB EEProm am IIC Bus

- VGA Ausgang

- PS/2 Maus und Tastatur Anschluss

- System ACE und CompactFlash Anschluss

- 8MB SRAM

- 1000MBit Ethernet Karte

- USB Chipsatz mit Host und Peripherie Anschluss

Der Großteil der Peripherie ist direkt mit dem FPGA verbunden. Der Flash und der SRAM teilen sich einen Bus, weswegen nur einer zur Zeit benutzt werden kann. Der CPLD ist so positioniert, dass er Zugriff auf alle nicht-flüchtigen Speicher hat und mit denen den FPGA programmieren kann.

# 3 Übersicht zu den Regelungsfunktionen

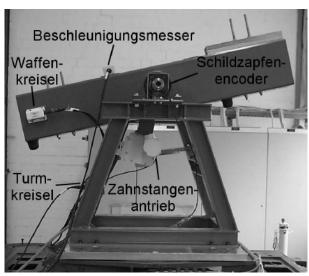

Zur Richtungsstabilisierung von Plattformen wie Radarantennen, optische Sichtgeräte und Rohrwaffen auf Fahrzeugen, sind die meisten Sensoren (Kreisel, Beschleunigungsmesser) auf der zu stabilisierenden Plattform angebracht. Dort sind sie Umweltbedingungen wie Nässe, Temperaturschwankungen und starken Erschütterungen ausgesetzt. Zusätzlich muss ein langer Kabelbaum die Sensoren mit der Reglereinheit verbinden. Hieraus entstand die Idee der sensorlosen Plattform: Anstatt auf der Plattform, werden die Sensoren im Inneren des Fahrzeugs untergebracht. Das sollte die Zuverlässigkeit der Sensoren erhöhen, sowie die Kosten der Montage reduzieren, da der lange Kabelbaum eingespart werden kann. Die Regelung ist das Ergebnis einer Studienarbeit[16] mit dem Thema "Entwicklung eines neuen Regelungskonzeptes zur Stabilisierung von Plattformen".

Abb. 3.1: Wippe, wie sie in der Firma ESW GmbH zum testen von Regelungen genutzt wird

Bei dem für diese Regelung benutzten Modell, können an jedem Ende des Profils Gewichte befestigt werden, damit es in der Trägheit und Unbalance dem Original entspricht.

Die Drehgeschwindigkeit wird vom Waffenkreisel und die Nickbewegung vom Turmkreisel gemessen. Zur Ermittlung des Winkels zwischen Waffe und Turm dient der Schildzapfenencoder. Zur Simulation wird nur die oberste Achse in Betrieb genommen, da nur der Höhenantrieb untersucht werden sollte.

# 3.1 Modell der Regelung zur Stabilisierung der Höhe von Plattformen

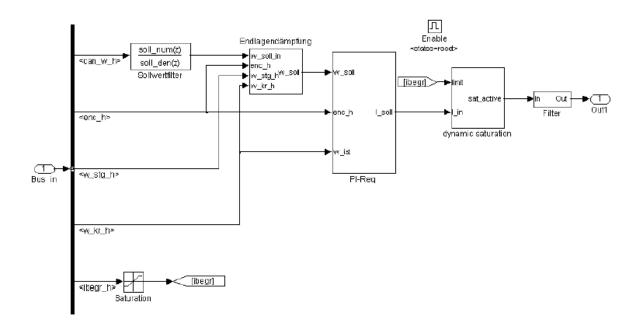

Entworfen wurde der Regler mit Matlab Simulink[15]. Daraus wurde der C Quellcode mit dem Matlab Real-Time Workshop[14] für den TI320C30 DSP von Texas Instruments generiert.

#### Eingänge

• can\_w\_h: Eingang CAN Omega Höhe: Soll Position über CAN.

Abb. 3.2: Regler

- enc\_h: Eingang Stellungssignal Zapfenencoder: relative Position der Waffe zum Turm.

- w\_kr\_h: Waffen Kreisel Höhe, Eingang vom Waffenkreisel in Rad/s.

- w\_stg\_h: Eingang Omega Stellungsgeber Höhe: Drehgeschwindigkeitssignal der Waffe.

#### **Parameter**

- **betr\_art**: Betriebsart. Es wird hier nur die Betriebsart 6 (Nachführen) verwendet, da sie die aufwendigste ist. In dieser Betriebsart wird die Waffe einem Sichtgerät nachgeführt. Sollwert ist hierbei *can\_w\_h* und Istwert ist *enc\_h*.

- **ibegr\_h**: Strombegrenzung.

#### Ausgänge

• iq\_soll: Ausgang für den Stromregler.

Da für diese Arbeit keine echte Hardware zur Verfügung steht, werden die Eingänge und Parameter vor jeder Ausführung mit neuen zufälligen Werten, die nicht Null sind, gesetzt.

# 3.2 Schnittstellen der Regelung

Mit den folgenden Funktionen wird auf den Regler zugegriffen:

Die Funktion *MdlStart()* startet den Regler, *MdlUpdate(int\_T tid)* und *MdlOutputs(int\_T tid)* aktualisieren den Regler. Das Argument *tid* wird ignoriert.

# 4 Der Microblaze Mikrocontroller

In diesem Kapitel wird der Microblaze mit den für diese Arbeit benutzten IP-Cores und ihren Merkmalen erläutert.

#### 4.1 Grundstruktur des Microblaze Mikrocontrollers

#### 4.1.1 Der RISC-Prozessor mit Harvard-Architektur

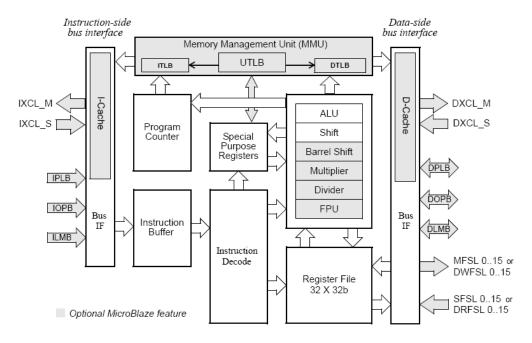

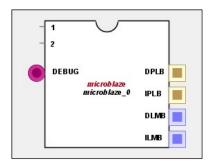

Der Microblaze ist ein 32 Bit RISC-Mikroprozessor mit folgenden Eigenschaften (vgl. Abb. 4.1):

- zweiunddreißig 32 Bit Register

- 32 Bit Instruktionssatz

- 32 Bit breiter Bus

- Datentypen Wort, Halbwort und Byte

- Byte-Reihenfolge Big-Endian

- Havard Architektur: Instruktionen und Daten liegen in verschiedenen Speicherbereichen. Die Speicherbereiche können jedoch überlappen, was das Software Debugging vereinfacht.

- Speichersparende 3-Stage oder schnelle 5-Stage Pipeline.

- optionale Komponenten: Fließkommaeinheit, Integer Multiplizierer, Integer Dividierer und Barrel shifter. Ein Barrel Shifter ermöglicht die Verschiebung von mehreren Bits auf einmal.

- Memory Mapped I/O: Ein- und Ausgabe liegen im gleichen Speicherbereich wie Daten.

Das folgende Bild gibt eine Übersicht der Fähigkeiten des Microblaze:

Abb. 4.1: Struktur des Microblaze

Die Abkürzungen im Abbildung 4.1 erklären sich wie folgt:

**DPLB:** Data interface, Processor LocalBus

**DOPB:** Data interface, On-chip Peripheral Bus

**DLMB:** Data interface, Local Memory Bus (BRAM only)

**IPLB:** Instruction interface, Processor Local Bus

**IOPB:** Instruction interface, On-chip Peripheral Bus

**ILMB:** Instruction interface, Local Memory Bus (BRAM only)

**MFSL 0..15:** FSL master interfaces

**DWFSL 0..15:** FSL master direct connection interfaces

**SFSL 0..15:** FSL slave interfaces

**DRFSL 0..15:** FSL slave direct connection interfaces

**IXCL:** Instruction side Xilinx CacheLink interface (FSL master/slave pair)

**DXCL:** Data side Xilinx CacheLink interface (FSL master/slave pair)

**Core:** Miscellaneous signals for: clock, reset, debug, and trace

#### 4.1.1.1 Ausnahmen

Der Microblaze unterstützt Reset, Interrupts und Hardware Ausnahmen (Exceptions). Hardware Ausnahmen sind ungültige Operationen, Fehler am Bus und nicht am 4-Byte Raster ausgerichtete Datenzugriffe.

#### 4.1.1.2 Cache

Der Microblaze verfügt über einen zuschaltbaren Instruktionen- und Daten-Cache im FPGA internen Block-RAM. Der Cache kann Zugriffe auf Speicher, die nicht an den LMB angeschlossen sind, erhöhen. Der Zugriff auf den Cache erfolgt mit der CacheLink (XCL) Schnittstelle.

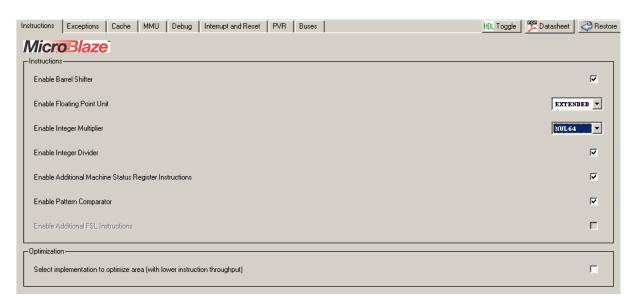

#### 4.1.1.3 Fließkommaeinheit

Die Microblaze Fließkommaeinheit (FPU) ist weitgehend IEEE754[13] kompatibel:

- Einfache Genauigkeit (32 Bit), definierte Werte für Not-a-Number (NaN), Unendlich und Null.

- Die Operationen Addition, Subtraktion, Multiplikation, Division und Vergleiche in Hardware.

- Operation für Quadratwurzel in Hardware zusätzlich schaltbar.

- Rundung auf nächstgelegenen Wert.

- Statusbits für "Underflow", "Overflow", Division durch Null und ungültige Operation

- "Overflow" resultiert immer in Unendlich, "Underflow" in Null als Ergebnis.

Gegenüber dem Standard gibt es folgende Abweichung:

- "Subnormal"-Werte, auch als "Denormalized"-Werte bezeichnet, werden nicht unterstützt. Eine Operation auf so einem Wert liefert NaN als Ergebnis und setzt das "sticky denormalized operand error"-Bit im Floating Point Status Register (FSR). "Subnormal"-Werte sind so kleine Zahlen, dass die Binäre Mantisse nicht mehr eins ist.

- Es wird Flush-to-Zero (FTZ) verwendet: Ein "Subnormal"-Ergebnis wird als 0 gespeichert und das "Underflow"-Bit im FSR gesetzt.

- Operation mit NaN-Werten ergeben immer den NaN-Wert 0xFC00000.

- Bei einem Overflow ist das Ergebnis immer  $\infty$ .

Ist die FPU deaktiviert werden Fließkommaoperationen in Software durchgeführt. Eine FPU für doppelte Genauigkeit ist nicht verfügbar.

| Schnittstelle              | Тур             | Anwendung                         |

|----------------------------|-----------------|-----------------------------------|

| Trace                      | Bus             | Trace                             |

| Debug                      | Bus             | Debug                             |

| IXCL, DXCL                 | Bus             | XCL Instruktionen, Daten          |

| IPLB, DPLB                 | Bus             | PLB Instruktionen, Daten          |

| ILMB, DLMB                 | Bus             | LMB Instruktionen, Daten          |

| MB_Halted                  | Bit Ausgang     | Status der Pipeline Aktiv/Inaktiv |

| Signale beginnend mit DBG_ | Bit Ein/Ausgang | Debug Signale des MDM             |

| Interrupt                  | Bit Eingang     | Externer Interrupt                |

| MB_RESET                   | Bit Eingang     | Reset                             |

Tabelle 4.1: Schnittstellen Microblaze

#### 4.1.1.4 Header-Dateien und Treiber des Microblaze

Der Microblaze kennt Funktionen, um Interrupts und Cache an- und auszuschalten. Sie sind in der Header-Datei *mb\_interface.h* definiert[22]. Automatisch generierte Konstanten, wie Adressen, Bitmasken und Hardware-Einstellungen der Peripherie finden sich in der Header-Datei *xparameters.h*. Die Adresse des ersten Timer findet sich in der Header-Datei z.B. als XPAR\_XPS\_TIMER\_0\_BASEADDR, der Interrupt von diesem Timer hat die Bitmaske XPAR\_XPS\_TIMER\_0\_INTERRUPT\_MASK. Die meisten IP-Cores kennen zwei Treiber, um auf ihre Hardware zuzugreifen: "Ebene 0" und "Ebene 1" Treiber. Treiber der Ebene 0 sind low-level-Treiber. Sie sind daran erkennbar, dass die Header-Dateien zusätzlich ein "\_1" im Namen tragen. Gegenüber den Treibern der Ebene 1 verbrauchen sie weniger Speicher und CPU-Zeit. Die abstrakteren Treiber der Ebene 1 unterstützen dafür mehr Funktionen.

#### 4.1.2 Bussysteme des Microblaze: FSL, LMB und PLB

#### 4.1.2.1 Fast Simplex Link

Über den Fast Simplex Link (FSL) ist der Microblaze in der Lage, Daten innerhalb von 2 Taktzyklen mit jedem Abschnitt des FPGAs auszutauschen. Er wird benutzt um Hardware Beschleuniger an den Microblaze anzubinden. Ein Hardware Beschleuniger kann z.B. außerhalb des Prozessors eine Zeitintensive Operation wie eine Laplace-Transformation durchführen und damit den Prozessor entlasten.

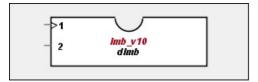

#### 4.1.2.2 Der Local Memory Bus

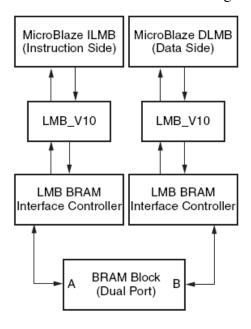

Der Local Memory Bus (LMB) ist ein synchroner Bus, der in erster Linie dazu da ist auf On-Chip Block-RAM zuzugreifen. Zugriffe auf Block-RAM über den LMB benötigen genau einen Taktzyklus was den Block-RAM am LMB zum idealen Cache oder schnellen Programmspeicher macht. Der Microblaze unterstützt zwei LMB, einen für Daten und einen für Instruktionen. Üblicherweise greifen Instruktionen- und Daten LMB auf den gleichen Block-RAM zu:

**Abb.** 4.2: Synchron getaktetes Block-RAM mit Dual-Ports an zwei LMB-Bussen.

Auf Abbildung 4.2 ist ein BRAM mit beiden Anschlüssen über zwei schnelle LMB Verbindungen an den Microblaze angeschlossen. Für Programme bis maximal 64k kann der an den LMB

angeschlossene Speicher als Hauptspeicher verwendet werden. Für größere Programme muss der Code in einen Massenspeicher wie DDR oder SRAM geladen werden. Der BRAM am LMB kann dann als Instruktionen und/oder Daten-Cache konfiguriert werden. Schnittstellen:

| Schnittstelle | Тур         | Anwendung |

|---------------|-------------|-----------|

| SYS_Rst       | Bit Eingang | Reset     |

| LMB_Clk       | Bit Eingang | Clock     |

Tabelle 4.2: Schnittstellen LMB

#### 4.1.2.3 Der Processor Local Bus

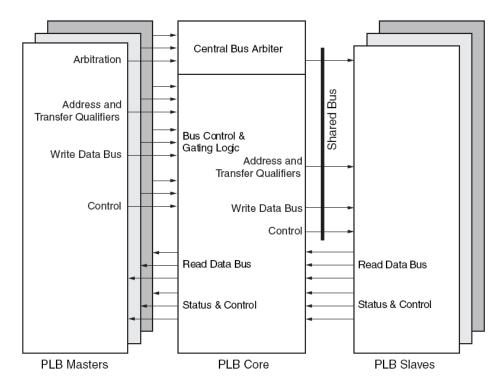

Der Processor Local Bus (PLB) ist ein von IBM[12] entwickelter, mehrfach Master und Slave Bus. Welcher Master die Kontrolle über den Bus erhält, erfolgt über Prioritäten oder das Round-Robin-Verfahren. Die drei Zyklen lange Kommunikation mit den Slaves erfolgt über einen 64 Bit breiten Bus für Adressen und einen 32, 64 oder 128 Bit breiten Bus für Daten. Der PLB ist seit dem EDK 10.1i der Nachfolger des ebenfalls von IBM entwickelten On-Chip Peripheral Bus (OPB). Gegenüber dem OPB verfügt der PLB über separate lese- und schreib Pfade. Damit können zwei verschiedene Adressen gleichzeitig gelesen und geschrieben werden. Außerdem kann er die Adresse für den nächsten Arbeitsvorgang während der Datenübertragung des aktuellen Arbeitsvorgangs senden. Der Device Control Register (DCR) -Bus kann benutzt werden, um auf die Status- und Kontroll-Register der verschiedenen OPB und PLB Master und Slaves zuzugreifen damit der OPB, bzw PLB entlastet wird. Der Processor Local Bus verbindet den Großteil der Peripherie mit dem Microblaze.

Die Implementation des Processor Local Bus besteht aus einem PLB Kern, an den alle Master und Slaves angeschlossen sind. Es werden bis zu 16 Master und unbeschränkt viele Slaves unterstützt. Die Anzahl der angeschlossenen Master und Slaves hat allerdings direkten Einfluss auf die Geschwindigkeit des PLB Kerns. Der PLB Kern besteht aus dem Bus Arbiter und der Logik für die Bus- und Taktkontrolle.

#### Schnittstellen:

| Schnittstelle | Typ               | Anwendung                                           |

|---------------|-------------------|-----------------------------------------------------|

| SDCR          | Bus               | Slave Anschluss für den Device Control Register Bus |

| Bus_Error_Det | Interrupt Ausgang | Liefert einen Interrupt, wenn ein Fehler vorliegt   |

| SYS_Rst       | Bit Eingang       | Clock                                               |

| PLB_Clk       | Bit Eingang       | Clock                                               |

Tabelle 4.3: Schnittstellen PLB

#### 4.1.3 Speicher am Microblaze: Block-RAM und Flash

#### 4.1.3.1 Der Block-RAM

Als Block-RAM (B-RAM) wird der FPGA-interne Speicher bezeichnet, der seit etwa 10 Jahren in FPGAs eingebaut wird. Er eignet sich dazu, größere Datenmengen aufzunehmen, für die im FPGA sonst nicht genügend Look-Up-Tabellen oder Flip-Flops zur Verfügung stehen. Ein Beispiel zur Verwendung ist als Audio- oder Videopuffer. Jeder Block-RAM im FPGA verfügt über zwei funktional identische Ports, die auf den gleichen Speicherbereich zugreifen. Jeder Port kann unabhängig von den anderen als nur lesen, nur schreiben oder schreiben und lesen konfiguriert werden. Ist der eine Port im nur-lesen-Modus und der andere im nur-schreiben-

Abb. 4.3: PLB mit drei Master und drei Slaves

Modus lässt sich der Block-RAM z.B. als FIFO einsetzen. Beide Ports dürfen gleichzeitig die selbe Adresse lesen. Schreibt der eine Port eine Adresse, die der andere Port gleichzeitig lesen möchte ist das read-after-write-Verfahren Voreinstellung, bei der die zu schreibenden Daten gleichzeitig an den Lesen-Port gesendet werden.

Als interner Speicher des FPGA arbeitet er mit der selben Taktfrequenz wie der Microblaze. Der Block-RAM kann über den LMB oder den PLB, bzw dessen Vorläufer OPB an den Microblaze angeschlossen werden. Programme die Block-RAM-Speicher benutzen, der an den PLB oder OPB angebunden ist, sind etwa um das 6.5fache langsamer als am LMB.

#### Schnittstellen:

| Schnittstelle | Тур | Anwendung                                                  |

|---------------|-----|------------------------------------------------------------|

| PORTA         | Bus | Anschluss an LMB oder PLB BRAM Interface Controller Port A |

| PORTB         | Bus | Anschluss an LMB oder PLB BRAM Interface Controller Port B |

Tabelle 4.4: Schnittstellen Block-RAM

#### 4.1.3.2 BRAM Interface Controller

Um den Block-RAM mit dem PLB oder LMB zu verbinden, wird noch ein LMB BRAM Interface Controller, btw XPS BRAM Interface Controller benötigt. Sie verfügen über genau einen Anschluss an den Bus und einen Anschluss für den Speicher.

#### 4.1.3.3 Externer Speicherzugriff

Der XPS Multi-Channel External Memory Controller (XPS MCHEMC) IP-Core ist für den Zugriff auf externe Speicher wie Flash oder DDR-SDRAM zuständig. Er sorgt dafür, dass der externe Speicher im Adressraum des Microblaze abgebildet wird. Speicher wie SRAM kann hiermit über Speicherzugriffe gelesen und geschrieben werden.

Flash-Speicher nimmt hier eine Sonderrolle ein: Er kann auf diese Weise nur gelesen werden.

Um den Flash zu löschen oder schreiben müssen mit Hilfe von diesem IP-Core I/O-Kommandos an den Flash gesendet werden. Dazu wird der Flash zuerst in den Schreib-, bzw Lösch-Modus geschaltet und dann die Daten gesendet. Ist der Flash im Schreib- oder Lösch-Modus kann er nicht gelesen werden. Vor dem Schreibvorgang muss immer ein Löschvorgang erfolgen. Schnittstellen:

| Schnittstelle              | Тур             | Anwendung                       |

|----------------------------|-----------------|---------------------------------|

| MCH1                       | Bus             | Anschluss an den Multi-Channel  |

| MCH0                       | Bus             | Anschluss an den Multi-Channel  |

| SPLB                       | Bus             | Slave Anschluss an den PLB      |

| Signale beginnend mit Mem_ | Bit Ein/Ausgang | Kommunikation mit dem Speicher  |

| RdClk                      | Bit Eingang     | Clock die verwendet wird um von |

|                            |                 | dem Speicher zu lesen           |

Tabelle 4.5: Schnittstellen Multi-Channel External Memory Controller

#### 4.1.4 Peripherie des Microblaze

#### 4.1.4.1 Das Timer/PWM-Modul

Der xps\_timer IP-Core ist ein maximal 32 breiter Timer, der an den PLB angeschlossen wird. Die Register-Breite des Zählers kann zwischen 8 und 32 Bit eingestellt werden. Der Entwickler kann auch auswählen, ob er einen oder zwei Timer instantiieren möchte. Der Timer arbeitet grundsätzlich mit der CPU Frequenz. Einen Vorteiler gibt es nicht. Er verfügt über ein Load, sowie ein Kontroll-Register und kann einen Interrupt auslösen. Der Interrupt Pin wird von beiden Timern geteilt.

#### Schnittstellen:

| Schnittstelle | Тур               | Anwendung                            |

|---------------|-------------------|--------------------------------------|

| SPLB          | Bus               | Slave Anschluss an den PLB           |

| Freeze        | Bit Eingang       | Hält den Timer z.B. beim Debuggen an |

| Interrupt     | Interrupt Ausgang | Interrupt                            |

| PWM0          | Bit Ausgang       | Ausgang der Pulsweitenmodulation     |

| GenerateOut1  | Bit Ausgang       | Generate Ausgang 1                   |

| GenerateOut0  | Bit Ausgang       | Generate Ausgang 0                   |

| CaptureTrig1  | Bit Eingang       | Capture Eingang 1                    |

| CaptureTrig0  | Bit Eingang       | Capture Eingang 0                    |

Tabelle 4.6: Schnittstellen Timer

#### Es gibt 3 Betriebsarten:

**Generate:** Der Timer generiert sich wiederholende Signale.

Entweder wird von 0 an hoch, oder bis 0 von dem Wert in dem Load-Register runtergezählt. Wenn der Endwert erreicht wurde kann der Timer einen Interrupt auslösen oder das GenerateOut Signal auf high ändern.

#### **Capture:** Externe Ereignisse aufnehmen.

Es wird entweder hoch oder runtergezählt. Wenn am CaptureTrig ein Ereignis eintritt wird der aktuelle Wert des Zählers in das Load Register gespeichert. Gleichzeitig kann ein Interrupt ausgelöst werden.

**PWM:** Im Pulse Width Modulation Modus arbeiten beide Timer zusammen. Timer0 setzt die Periode und Timer1 die Zeit, die das Signal einen positiven Wert liefert.

Um einen Timer in der Ebene-0 zu konfigurieren werden die Funktionen XTmrC-tr\_mSetLoadReg() und XTmrCtr\_mSetControlStatusReg() aus xtmrctr\_l.h benötigt. XTmrC-tr\_mSetLoadReg() setzt das Load-Register eines Timer:

#### Listing 4.1: Signatur von XTmrCtrm\_SetLoadReg()

```

void XTmrCtr_mSetLoadReg(u32 BaseAddress, u8 TmrCtrNumber, u32 RegisterValue);

```

Das erste Argument ist die Adresse des Timer, das zweite wählt die Nummer des Timer (0 oder 1). Das letzte Argument ist der Wert, der gesetzt werden soll.

Um das Kontrollregister zu setzen wird *XTmrCtr\_mSetControlStatusReg()* benutzt. Die Signatur ist wie folgt:

#### Listing 4.2: Signatur von XTmrCtrm\_SetControlStatusReg()

```

void XTmrCtr_mSetControlStatusReg(u32 BaseAddress, u8 TmrCtrNumber, u32 RegisterValue);

```

Die Argumente sind äquivalent zu *XTmrCtr\_mSetLoadReg()*. Der Register-Wert ist eine Liste mit den Timer Bit-Masken, die in Tabelle 4.7 zusammengefasst sind.

| Option                    | Beschreibung                                        |

|---------------------------|-----------------------------------------------------|

| XTC_CSR_ENABLE_ALL_MASK   | Aktiviert alle Zähler.                              |

| XTC_CSR_ENABLE_PWM_MASK   | Aktiviert die PWM.                                  |

| XTC_CSR_INT_OCCURED_MASK  | Ist 1, wenn ein Interrupt aufgetreten ist. Bit wird |

|                           | durch schreiben dieses Bits wieder gelöscht.        |

| XTC_CSR_ENABLE_TMR_MASK   | Aktiviert nur Timer 1 oder 2.                       |

| XTC_CSR_ENABLE_INT_MASK   | Aktiviert Interrupts.                               |

| XTC_CSR_LOAD_MASK         | Lädt den Timer mit dem Wert aus dem Load-           |

|                           | Register.                                           |

| XTC_CSR_AUTO_RELOAD_MASK  | Der Timer wird automatisch mit dem Wert aus         |

|                           | dem Load-Register geladen.                          |

| XTC_CSR_EXT_CAPTURE_MASK  | Aktiviert den Capture-Modus.                        |

| XTC_CSR_EXT_GENERATE_MASK | Aktiviert den Generate-Modus.                       |

| XTC_CSR_DOWN_COUNT_MASK   | Lässt den Timer runter- anstatt hochzählen.         |

| XTC_CSR_CAPTURE_MODE_MASK | Aktiviert den Capture-Modus.                        |

Tabelle 4.7: Timer Bit-Masken des Kontrollregisters

Wenn ein Interrupt auftritt ist das Bit *XTC\_CSR\_INT\_OCCURED\_MASK* im Kontroll-Register gesetzt. Um den Interrupt zu quittieren, muss das Bit gelöscht werden. Ohne die anderen Einstellungen zu verändern, wird das Kontroll-Register zuerst gelesen und anschließend mit dem selben Wert geschrieben:

#### Listing 4.3: Timer Interrupt quittieren

```

csr = XTmrCtr_mGetControlStatusReg(XPAR_XPS_TIMER_REGEL_BASEADDR, 0);

XTmrCtr_mSetControlStatusReg(XPAR_XPS_TIMER_REGEL_BASEADDR, 0, csr);

```

Das XTC\_CSR\_INT\_OCCURED\_MASK-Bit ist dann gelöscht.

Ein Timer wird also wie folgt aufgesetzt:

Listing 4.4: Beispiel Generate-Timer Konfiguration

```

XTmrCtr_mSetLoadReg(XPAR_XPS_TIMER_0_BASEADDR, 0, 10000);

```

```

XTmrCtr_mSetControlStatusReg(XPAR_XPS_TIMER_0_BASEADDR, 0,

XTC_CSR_ENABLE_TMR_MASK | XTC_CSR_ENABLE_INT_MASK |

XTC_CSR_AUTO_RELOAD_MASK | XTC_CSR_DOWN_COUNT_MASK );

```

Der Timer wird von 10000 runter zählen, einen Interrupt erzeugen, und anschließend wieder von vorne anfangen.

Für die Ebene-1-Konfiguration als Zähler stehen folgende Funktionen aus *xtmrctr.h* zur Verfügung:

| Funktion                           | Argumente                | Beschreibung             |

|------------------------------------|--------------------------|--------------------------|

| XTmrCtr_Initialize( XTmrCtr *In-   | InstancePtr ist ein Zei- | Initialisiert den Zeiger |

| stancePtr, u16 DeviceId)           | ger auf eine Variable,   | auf den Timer            |

|                                    | die den Timer repräsen-  |                          |

|                                    | tiert, DeviceId ist die  |                          |

|                                    | eindeutige ID des Ti-    |                          |

|                                    | mer                      |                          |

| XTmrCtr_SetResetValue( XTmrCtr     | TmrCtrNumber wählt       | Setzt den Reset-Wert.    |

| *InstancePtr, u8 TmrCtrNumber, u32 | den Timer 0 oder 1,      |                          |

| ResetValue)                        | ResetValue ist der       |                          |

|                                    | Initialisierungswert.    |                          |

| void XTmrCtr_Start( XTmrCtr *In-   |                          | Startet den Timer.       |

| stancePtr, u8 TmrCtrNumber)        |                          |                          |

| void XTmrCtr_Stop( XTmrCtr *In-    |                          | Stoppt den Timer.        |

| stancePtr, u8 TmrCtrNumber)        |                          |                          |

| XTmrCtr_GetValue( XTmrCtr *In-     |                          | Liest den aktuellen      |

| stancePtr, u8 TmrCtrNumber)        |                          | Wert.                    |

| XTmrCtr_Reset( XTmrCtr *Instan-    |                          | Startet den Timer neu.   |

| cePtr, u8 TmrCtrNumber)            |                          |                          |

Tabelle 4.8: Funktionen des Timer für Ebene-1-Konfiguration

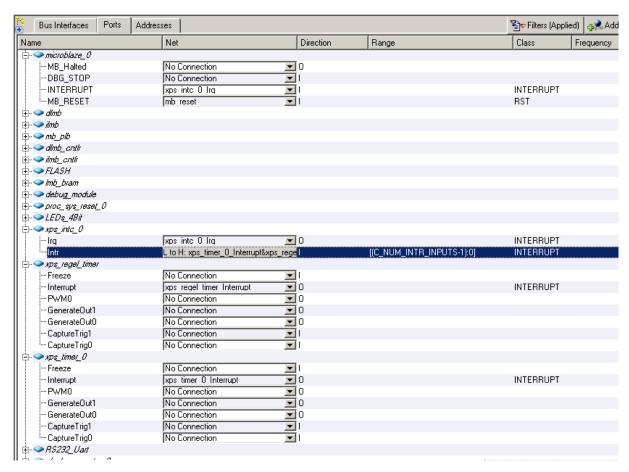

#### 4.1.4.2 Der Interrupt Controller

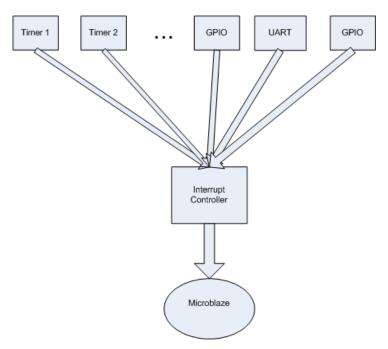

Der Microblaze unterstützt nur eine externe Interrupt Quelle. Existieren mehrere Interruptquellen, muss ein Interrupt Controller dazwischen geschaltet werden. Dieser empfängt die Interrupts von der Peripherie und leitet diese an den einen Interrupt Port des Microblaze weiter: Schnittstellen:

| Schnittstelle | Тур               | Anwendung                   |

|---------------|-------------------|-----------------------------|

| SPLB          | Bus               | Slave Anschluss an den PLB  |

| Interrupt     | Interrupt Ausgang | Interrupt                   |

| Intr          | Vektor Eingang    | Eingang für alle Interrupts |

Tabelle 4.9: Schnittstellen des Interrupt Controller

Der Interrupt Controller entscheidet wer den Interrupt ausgelöst hat und ruft die passende Routine auf. Die Routine muss dann der Hardware bestätigen, dass der Interrupt abgearbeitet wurde. Der Interrupt Controller verfügt außerdem über folgende Eigenschaften:

- Es werden maximal 32 Interrupt-Quellen unterstützt: Die Interrupt-Quellen werden in einem 32-Bit-Vektor gespeichert.

- Interrupt Prioritäten werden anhand der Position im Vektor gesetzt. Der Interrupt mit dem niederwertigstem Bit (LSB) hat die höchste Priorität.

**Abb.** 4.4: Mit dem Interrupt Controller unterstützt der Microblaze mehr als einen externen Interrupt.

- Ein- und abschalten von individuellen Interruptquellen wird unterstützt.

- Es werden Flanken- und Level-sensitive Interrupts unterstützt.

Interrupts, die von dem Interrupt Controller abgearbeitet werden bleiben aktiv, bis sie explizit von der Software zurückgesetzt werden.

Ein Interrupt läuft bei normaler Konfiguration mit dem Interrupt Controller wie folgt ab:

- 1. Eine Peripherie wirft einen Interrupt.

- 2. Der Interrupt Controller empfängt den Interrupt, hält ihn aktiv bis er explizit quittiert wird, und leitet den Interrupt an den Microblaze weiter.

- 3. Wenn das Interrupt Enable (IE) Bit im Machine Status Register (MSR) gesetzt ist, reagiert der Microblaze auf den Interrupt und führt die Interrupt Service Routine (ISR), die Funktion mit dem Namen \_interrupt\_handler(), auf. Das IE Bit wird gelöscht.

- 4. Die aufgerufene Funktion prüft, welche Funktion als Interrupt Handler eingetragen ist. In diesem Fall *XIntc\_DeviceInterruptHandler()* des Interrupt Controller.

- 5. XIntc\_DeviceInterruptHandler() testet anhand einer Liste, welche Interrupts anstehen und ruft die eingetragene Funktion für de Interrupt mit der höchsten Priorität als Interrupt Handler auf.

- 6. Der aufgerufene Interrupt Handler führt die gewollte Aktion aus und bestätigt gegebenenfalls der Peripherie, dass der Interrupt abgearbeitet wurde.

- 7. Nach Abarbeitung der Funktion quittiert XIntc\_DeviceInterruptHandler() den Interrupt bei dem Interrupt Controller, prüft ob noch ein weiterer Interrupt zur Bearbeitung ansteht und beendet sich.

- 8. Mit dem Assembler-Befehl *RTID* wird die ISR in \_interrupt\_handler() verlassen und das IE Bit wieder gesetzt.

Für die Ebene-0-Konfiguration werden die Funktionen XIntc\_RegisterHandler(), XIntc\_mEnableIntr() und XIntc\_mMasterEnable() aus xintc\_l.h benötigt.

Abb. 4.5: Arbeitsweise des Interrupt Controllers

XIntc\_mMasterEnable() aktiviert das Master-Interrupt-Bit im Master-Enable-Register und damit den Interrupt Ausgang. Standardmäßig ist der Master deaktiviert.

#### Listing 4.5: Signatur von XIntc\_mMasterEnable()

void XIntc\_mMasterEnable(u32 BaseAddress);

XIntc\_mEnableIntr() aktiviert die Interrupts mit der übergebenen Bitmaske. Standardmäßig sind alle Interrupts deaktiviert. Die Signatur ist die folgende:

#### Listing 4.6: Signatur von XIntc mEnableIntr()

void XIntc\_mEnableIntr(u32 BaseAddress, u32 EnableMask);

Das erste Argument ist die Basisadresse des Interrupts Controllers, das zweite eine Bitmaske von Interrupts, die aktiviert sein sollen. Der Befehl beschreibt das Interrupt-Enable-Register. Um das Interrupt-Enable-Register zu lesen wird der Befehl *XIntc\_In32()* mit der Adresse des Registers aufgerufen. Ein Beispiel dafür findet sich im Listing 7.2.

Mit XIntc\_RegisterHandler wird einem Interrupt eine Funktion als Interrupt-Handler zugewiesen. Die Signatur ist:

#### Listing 4.7: Signatur von XIntc\_RegisterHandler()

```

void XIntc_RegisterHandler(u32 BaseAddress, int InterruptId,

XInterruptHandler Handler, void *CallBackRef);

```

Nach der Basisadresse des Interrupts Controllers folgt die Interrupt ID und die Funktion, die aufgerufen werden soll. Das letzte Argument ist ist ein optionaler Parameter für die Funktion. Das folgende Beispiel registriert und aktiviert einen Timer- und einen RS-232-Interrupt:

#### Listing 4.8: Beispiel Interrupt Controller-Konfiguration

```

// register interrupt handler

XIntc_RegisterHandler(XPAR_XPS_INTC_0_BASEADDR,

XPAR_XPS_INTC_0_XPS_TIMER_0_INTERRUPT_INTR,

```

```

(XInterruptHandler) vTimerHandler, NULL);

XIntc_RegisterHandler(XPAR_XPS_INTC_0_BASEADDR,

XPAR_XPS_INTC_RS232_INTERRUPT_INTR,

(XInterruptHandler) vUartHandler, NULL);

// Start the interrupt controller

XIntc_mMasterEnable();

// Enable interrupts

XIntc_mEnableIntr(XPAR_XPS_INTC_0_BASEADDR, XPAR_XPS_TIMER_0_INTERRUPT_MASK |

XPAR_RS232_INTERRUPT_MASK);

```

#### 4.1.4.3 Ein- und Ausgabe

Der General Purpose Input/Output- (GPIO)-Core wird benutzt um einzelne Pins am FPGA zu lesen oder zu schreiben. Es gibt die Option einen Interrupt zu senden, wenn sich ein Eingang ändert. Der Core unterstützt Pins, die nur als Input, nur als Output und als In/Ouput funktionieren können.

#### Schnittstellen:

| Schnittstelle | Тур                            | Anwendung                  |

|---------------|--------------------------------|----------------------------|

| SPLB          | Bus                            | Slave Anschluss an den PLB |

| GPIO_IO, GPIO | in, Bit Bidirektional, Eingang | Verbindung zu einem FPGA   |

| GPIO_out      | Ausgang                        | Pin                        |

Tabelle 4.10: Schnittstellen GPIO

#### 4.1.4.4 Asynchroner serieller Datenstrom: RS-232

Der XPS Universal Asynchronous Receiver Transmitter (UART) ist die Steuerungs-Schnittstelle für serielle Übertragung. Es erlaubt das gleichzeitige Senden und Empfangen von Daten und verfügt über einen 16 Zeichen FIFO. Der UART kann einen Interrupt auslösen, wenn Daten in den RX FIFO geschrieben werden, oder der TX FIFO leer wird. Der Programmierer kann die Anzahl der Daten Bits, die Parität und die Baud Rate konfigurieren, jedoch nur in Hardware. Die Software kann diese Einstellungen nicht ändern.

#### Schnittstellen:

| Schnittstelle | Тур               | Anwendung                          |

|---------------|-------------------|------------------------------------|

| SPLB          | Bus               | Slave Anschluss an den PLB         |

| Interrupt     | Interrupt Ausgang | Interrupt                          |

| TX            | Bit Ausgang       | Senden, Verbindung zum FPGA Pin    |

| RX            | Bit Eingang       | Empfangen, Verbindung zum FPGA Pin |

Tabelle 4.11: Schnittstellen RS-232

Zur Ausgabe über die serielle Schnittstelle kann die Funktion  $xil\_printf()$  aus stdio.h verwendet werden. Sie ist in der Signatur zu dem 13kb großen printf() identisch, benötigt jedoch nur 3kb Speicher. Die Ausgabe von unsigned- und Fließkommazahlen werden von  $xil\_printf()$  nicht unterstützt.

#### 4.1.4.5 MDM Debug Module

Das Microblaze Debug Module (MDM) ermöglicht das Debuggen von dem Microblaze System über die JTAG Schnittstelle. Am angeschlossen PC dient die Xilinx Mikroprozessor Debug Engine (XMD) als Backend für den Software Debugger Insight oder den in Eclipse integrierten

Debugger (vgl. Abb. 4.6). Die Operationen Stop, Reset, Einzelschritt und lesen von Registern und Speicherbereichen werden unterstützt. Die Schnittstellen zeigt Tabelle 4.12.

| Schnittstelle | Тур               | Anwendung                                               |

|---------------|-------------------|---------------------------------------------------------|

| SPLB          | Bus               | Slave Anschluss an den PLB                              |

| XMTC          | Bus               | Verbindung zum Microblaze Trace Core                    |

| MBDEBUG_0     | Bus               | Direkte Verbindung zum Microblaze für die Debug Signale |

| MFSL0         | Bus               | Debug Verbindung zum FSL                                |

| Debug_SYS_Rst | Bit Ausgang       | Reset per Debugger ausgelöst                            |

| Interrupt     | Interrupt Ausgang | Interrupt                                               |

Tabelle 4.12: Schnittstellen Debug Module

Abb. 4.6: Microblaze Debug Hierarchien

#### 4.1.4.6 Clock Generator

Erzeugt aus einem Eingangs-Taktgeber mehrere Taktgeber, die in der Frequenz und Phase vom Eingang abweichen können. Der Ausgang "Locked" gibt an, ob die erzeugte Frequenz zuverlässig ist. Ein zweiter Taktgeber am Eingang "CLKFBIN" kann benutzt werden, um langfristige Abweichungen des erzeugten Taktes zu minimieren.

#### Schnittstellen:

| Schnittstelle | Тур         | Anwendung                        |

|---------------|-------------|----------------------------------|

| Locked        | Bit Ausgang | Signal ob die Clock stabil läuft |

| RST           | Bit Eingang | Reset                            |

| CLKOUT0       | Bit Ausgang | Ausgangs Clock                   |

| CLKIN         | Bit Eingang | Eingangs Clock                   |

Tabelle 4.13: Schnittstellen Clock Generator

#### 4.1.4.7 Prozessor System Reset-Module

Stabilisiert und synchronisiert den Reset:

- Der Asynchrone externe Reset wird mit dem Takt synchronisiert: Ein Reset sollte für mindestens 16 Takte anliegen. Das Reset-Module sorgt dafür, dass dies geschieht.

- Die minimale Pulsbreite für den Reset kann eingestellt werden.

- Sorgt für einen Reset wenn der Strom angeschaltet wird.

- Sorgt dafür, dass die Hardware Sequentiell aus dem Reset kommt:

- 1. Zuerst der PLB

- 2. 16 Takte Später die Peripherie

- 3. 16 Takte später die CPU.

- Der Digital Clock Generator "DCM Locked" Eingang kann an den Clock Generator IP-Core angeschlossen werden damit das System in den Reset-Zustand wechselt, sollte der Taktgeber unzuverlässig geworden sein.

#### Schnittstellen:

| Schnittstelle    | Тур         | Anwendung                          |

|------------------|-------------|------------------------------------|

| Peripheral_Reset | Ausgang     | Reset für die Peripherie           |

| Bus_Struct_Reset | Ausgang     | Reset für den Bus                  |

| MB_Reset         | Ausgang     | Reset für den Microblaze           |

| Dcm_Locked       | Bit Eingang | Locked Eingang vom Clock Generator |

| MB_Debug_Sys_Rst | Bit Eingang | Reset vom Debugger                 |

| Aux_Reset_In     | Bit Eingang | Zusätzlicher Reset Eingang         |

| Ext_Reset_In     | Bit Eingang | Externer Reset                     |

| Slowest_sync_clk | Bit Eingang | Clock                              |

Tabelle 4.14: Schnittstellen Reset Modul

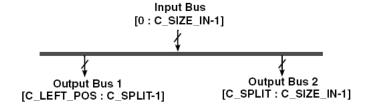

#### 4.1.4.8 Utility Bus Split

Erzeugt aus einem Eingangs Bus 2 Busse verschiedener Länge (vgl. Abb. 4.7). Ein 64 Bit Bus kann z.B. in zwei 32 Bit, oder einen 16 Bit und einen 8 Bit geteilt werden. Es kann auch nur ein Ausgang angeschlossen werden, wenn z.B. nicht die gesamte Bus-Breite genutzt werden muss.

**Abb.** 4.7: Utility Bus Split Arbeitsweise

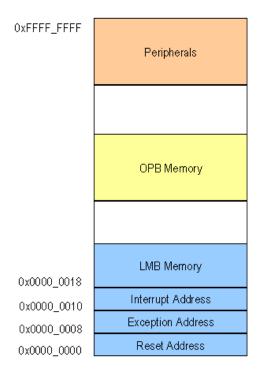

# 4.2 Speicher und Adressen des Microblaze

Abbildung 4.8 zeigt den Aufbau des Microblaze Adressraums. Mit einer Adressbreite von 32-Bit können maximal 4GB unterstützt werden.

Der Adressraum bis 0x4f ist für verschiedene Ausnahmen vorgesehen und muss in einem beschreibbaren Speicher liegen. Direkt darüber ist der Adressraum für den über den LMB angebunden Block-RAM auf dem FPGA. Dahinter befindet sich der Adressraum für den Speicher, der über den OPB oder PLB angeschlossen wird. Die höchsten Adressen sind für Peripherie vorgesehen.

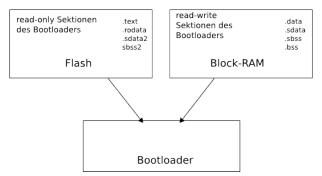

Wenn nicht anders vorgegeben packt der Linker alle Standard-Sektionen, sowie den Stack und den Heap in den LMB Block-RAM. Folgendes sind die Standard-Sektionen:

- .text: Der Maschinencode

- .data: Beschreibbare Daten

Abb. 4.8: Microblaze Speicheraufbau

- .rodata: Nicht-beschreibbare Daten Variablen, die in C mit dem Schlüsselwort const deklariert wurden.

- .bss: Von dem Programmierer nicht-initialisierte Daten. Der Bereich wird mit Nullen gefüllt und dadurch werden alle Variablen mit Null initialisiert. Damit sind alle, vom Programmierer nicht-initialisierte Variablen 0.

- .sdata: Beschreibbare Daten die kleiner als 8 byte sind.

- .sdata2: Nicht-beschreibbare Daten die kleiner als 8 byte sind.

- .sbss: Vom Programmierer nicht-initialisierte Daten die kleiner als 8 byte sind.

- .sbss2: Von dem Programmierer nicht-initialisierte-, nicht-beschreibbare Daten. Der Bereich wird mit Nullen gefüllt weswegen die Variablen in diesem Bereich immer Null sein werden.

Über ein Linker-Skript können die Sektionen auf alle angeschlossenen Speicher verteilt werden. Es können auch neue Sektionen erstellt werden, in die sich Funktionen ablegen lassen. Um z.B. die Funktion XFlashIntel\_WriteAddr in die selbst erstellte Sektion .text\_noflash zu legen wird die Funktion wie folgt definiert:

Listing 4.9: XFlashIntel\_WriteAddr in Sektion .text\_noflash

```

int XFlashIntel_WriteAddr(Xuint32 BaseAddress, Xuint32 Offset,

Xuint8 *BufferPtr, unsigned int Length)

__attribute__ ((section (".text_noflash")));

```

Im Linker-Skript lässt sich die neue Sektion jetzt jedem Speicherbereich zuordnen.

In diesem Kapitel wird das Open Source Echtzeitbetriebssystem FreeRTOS vorgestellt und in seiner Grundstruktur erläutert. Abschließend wird eine Beispiel-Task erstellt.

# 5.1 Das FreeRTOS.org Projekt

FreeRTOS[7] ist ein von Richard Barry entwickeltes, minimales, quelloffenes Echtzeitbetriebssystem. Die modifizierte GPL Lizenz[10] vereinfacht den Einsatz zu kommerziellen Zwecken. FreeRTOS wurde auf verschiedene Hardware-Architekturen portiert, darunter finden sich Portierungen für die Mikrocontroller der Atmel AVR Reihe, Freescale Coldfire, Hitachi H8 und Xilinx Microblaze sowie PowerPC. Derzeit werden über 20 Plattformen unterstützt. Kommerzieller Support wird angeboten.

Zum Projekt gehören noch die beiden nicht-freien Geschwister Projekte SafeRTOS und OpenRTOS die zu FreeRTOS funktional identisch sind und dieselbe API benutzen. OpenRTOS steht unter einer kommerziellen Lizenz. Projekte, die FreeRTOS benutzen müssen nach der GPL Lizenz den Quellcode des Systems inklusive aller Änderungen veröffentlichen. Dies ist bei OpenRTOS nicht der Fall. SafeRTOS ist die für sicherheitskritische Systeme nach IEC 61508 zertifizierte Variante von OpenRTOS. Vom TÜV Süd ist es zertifiziert bis Sicherheitsanforderungsstufe SIL 3[8]. Das Betriebsystem ist konfigurierbar, z.B. läßt sich mit verschiedenen Einstellungen der Speicherverbrauch bestimmen. Der FreeRTOS-Scheduler kann für den unterbrechenden, kooperativen oder Hybriden Betrieb konfiguriert werden. Der Großteil ist in der Sprache C geschrieben. Für einige Abschnitte musste auf Assembler zurückgegriffen werden.

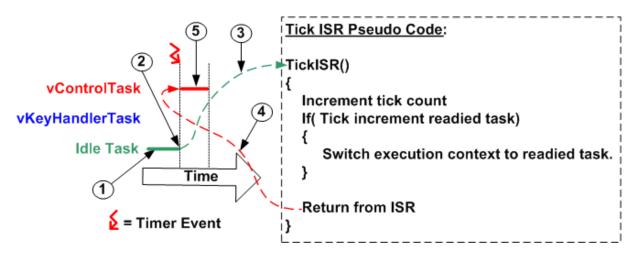

#### 5.2 Der Kernel

Der Scheduler ist der Kern von FreeRTOS. Seine Zeitmessung erfolgt auf Basis einer Tick-Variable. Der durch einen Timer ausgelöste FreeRTOS-Tick-Interrupt erhöht den Wert dieser Variablen mit einer vom Benutzer einstellbaren Frequenz. Der Wert kann in der Datei *FreeR-TOSConfig.h* geändert werden. Die Voreinstellung ist 1000Hz und damit jede Millisekunde. Im Normalfall unterbricht der FreeRTOS-Tick-Interrupt die derzeit laufende Task und kehrt nach Ausführung wieder in diese Zurück. Es gibt im unterbrechenden Betrieb den Sonderfall, dass eine höher priorisierte Task freigegeben oder geweckt werden muss. Dann muss der Scheduler nach Ausführung der ISR in die neue Task springen (siehe Abb. 5.1):

- 1. Die FreeRTOS-Idle-Task läuft.

- 2. Der FreeRTOS-Tick-Interrupt tritt auf: Die ISR wird aufgerufen. Dabei werden die aktuellen Werte der Register in den Stack gesichert.

- 3. Die Tick Variable wird in der ISR erhöht. Es wird festgestellt, dass die höher priorisierte vControlTask jetzt die CPU-Zeit bekommen muss. Es findet ein Context Switch statt: Die Register der Task, die gesperrt wird, werden vom Stack gesichert und mit den Register-Werten, der zu erwachenden Task überschrieben.

- 4. Die ISR springt nach Ausführung in die VControlTask zurück.

Abb. 5.1: Ablauf der FreeRTOS ISR

5. Die vControlTask wird ausgeführt.

FreeRTOS unterstützt Semaphoren[6] und Warteschlangen. Mit den Makros *taskEN-TER\_CRITICAL()* bzw *taskEXIT\_CRITICAL()* lassen sich Sektionen erzeugen, die nicht durch Interrupts unterbrochen werden.

#### 5.3 Aufbau des FreeRTOS-Sourcecodes

Das FreeRTOS-Projekt besteht aus folgenden Ordnern:

- **demo**: Enthält lauffähige Beispiele für verschiedene Architekturen und Boards, unter anderem für das ML403 unter EDK 7.1.

- license: Hier befindet sich die FreeRTOS Lizenz.

- traceon: Enthält einen Konverter für Scheduler Daten.

- source: Beinhaltet den kompletten FreeRTOS-Kernel.

Der FreeRTOS-Kernel setzt sich aus folgenden Dateien zusammen:

- **croutine.c**: Wird nur gebraucht, wenn Coroutines benutzt werden.

- **list.c**: Stellt dem FreeRTOS-Kernel den Basis Datentypen Liste zur Verfügung. Wird immer benötigt.

- queue.c: Muss nur eingebunden werden, wenn der Anwender Warteschlangen benötigt.

- tasks.c: Enthält die Funktionen um Tasks zu kontrollieren und muss deswegen in jedes Projekt eingebunden werden.

Alle Header-Dateien befinden sich im include/ -Ordner.

Der Ordner *portable/* enthält die Prozessor-Architektur abhängigen Dateien *port.c*, *portasm.s* und *portmacro.h*. Sie sind in jedem Projekt mit dabei. Für die Microblaze Architektur finden sich die Dateien im Ordner *gcc/Microblaze/*. Architektur abhängig sind vor allem das an- und ausschalten von Interrupts, der Context Switch, die Interrupt Service Routine, die Definition der Basis-Datentypen und die Timer Einstellungen für den FreeRTOS Interrupt.

Im Unterordner *memmang/ von portable/* befinden sich die Dateien *heap\_1.c*, *heap\_2.c* und *heap\_3.c*. Alle 3 Dateien enthalten verschiedene Beispiel-Implementierungen von *pvPortMalloc()* und *vPortFree()* um von den von FreeRTOS benötigten Speicher zu verwalten.

*heap\_1.c* enthält die minimalste Variante. Der Speicher kann nicht wieder freigegeben werden. Solange keine Tasks oder Warteschlangen gelöscht werden kann *heap\_1.c* verwendet werden.

Bei Benutzung der *heap\_2.c* kann Speicher wieder freigegeben werden. Zusammenhänge, freie Blöcke können aber nicht in einen einzelnen großen Block zusammengeführt werden. Deswegen kann Unvorhersehbares, eher zufälliges Belegen und Freigeben von Speicherbereichen bei dieser Version zu Fragmentation führen.

*heap\_3.c* greift auf die Compiler Implementierungen von *free()* und *malloc()* zurück. Eine der drei Varianten wird in jedem Fall benötigt.

Der FreeRTOS-Kernel für den Microblaze besteht also mindestens aus den Dateien

- source/tasks.c

- source/list.c

- source/portable/gcc/Microblaze/port.c

- source/portable/gcc/Microblaze/portasm.s

- source/portable/memmang/heap\_1.c, source/portable/memmang/heap\_2.c oder source/portable/memmang/heap\_3.c.

# 5.4 Einstellungen

Jedes Projekt benötigt noch die Header-Datei *FreeRTOSConfig.h*, die FreeRTOS Konfiguriert. Die Einstellungen sind in der FreeRTOS Dokumentation[9] erläutert.

#### 5.5 FreeRTOS Tasks

Es gibt immer mindestens eine Task: Die Idle-Task. Sie wird automatisch erstellt, erhält die niedrigste Priorität und wird immer dann ausgeführt, wenn keine andere Task ausgeführt wird. Mehrere Tasks können die gleiche Priorität haben. Eine Task kann sogar dieselbe Priorität wie die Idle-Task haben. Haben mehrere Tasks die gleiche Priorität und wollen beide ausgeführt werden, wird Round Robin verwendet. Tasks können mit *xTaskCreate()* erstellt und mit *vTaskDelete()* gelöscht werden.

Die Signatur von *xTaskCreate()* in *tasks.h* ist die folgende:

Listing 5.1: Signatur von xTaskCreate()

Die Parameter erklären sich wie folgt:

- *pdTASK\_CODE pvTaskCode*: Funktionszeiger auf die Task. Die Funktion muss z.B. durch eine Endlosschleife so programmiert werden, dass sie nie endet.

- *const portCHAR* \* *const pcName*: Anschaulicher Name für die Task. Wird zum Debuggen verwendet.

- unsigned portSHORT usStackDepth: Stackgröße für diese Task

- void \*pvParameters: Zeiger auf die Parameter für diese Task

- *unsigned portBASE\_TYPE uxPriority*: Priorität für diese Task. Die maximale Priorität wird mit der FreeRTOS Konfigurationsdatei festgelegt.

• *xTaskHandle \*pvCreatedTask*: Alias für die Task, der benutzt werden kann, um die Task von außen zu kontrollieren.

```

Listing 5.2: Beispiel für xTaskCreate()

```

```

xTaskCreate(vLedTask, NULL, configMINIMAL_STACK_SIZE, NULL, tskIDLE_PRIORITY+1, NULL);

```

Hier wird die Task vLedTask mit der, in der FreeRTOS Konfigurationsdatei festgelegten minimalen Stack-Größe und mit einer höheren Priorität als die Idle-Task erzeugt. Tasks werden in erster Linie mit den Funktionen *vTaskDelay()* und *vTaskDelayUntil()* (*tasks.h*) kontrolliert. vTaskDelay() legt eine Task für eine bestimmte Zeitspanne schlafen, *vTaskDelayUntil()* legt eine Task bis zu einem bestimmten Zeitpunkt schlafen.

Folgendes Beispiel schaltet jede Sekunde eine LED:

Listing 5.3: Beispiel für eine Task

```

static portTASK_FUNCTION( vLedTask, pvParameters ) {

portTickType xLastWakeTime;

while(1) {

xLastWakeTime = xTaskGetTickCount();

toggleLED(0);

// Wakeup every second

vTaskDelayUntil(&xLastWakeTime, 1000);

}

}

```

Dabei gibt xTaskGetTickCount() (tasks.h) die Anzahl Ticks zurück, seitdem der Scheduler gestartet wurde.

#### 5.6 Intertask-Kommunikation

Es gibt 3 APIs um zwischen Tasks zu kommunizieren: Eine mit allen Fähigkeiten (fully featured), eine Alternative und eine minimale (light). Die minimale Version braucht von allen 3 Versionen am wenigsten CPU-Zeit, ist auf die Benutzung von Interrupts heraus ausgelegt und sollte nicht aus Tasks heraus benutzt werden. Im Gegensatz dazu, sollten die Version mit allen Fähigkeiten und die alternative beide nicht aus einem Interrupt heraus benutzt werden. Die Version mit allen Fähigkeiten hat zum Ziel die Zeit, die in kritischen Sektionen verbracht wird, zu minimieren. Die Alternative API ist identisch zu der Version mit allen Fähigkeiten, jedoch nicht so durchdacht implementiert: Die Alternative Version benötigt weniger CPU-Zeit als die mit allen Fähigkeiten, verbringt allerdings mehr Zeit in kritischen Sektionen, was die Antwort-Zeit auf Interrupts erhöht. Die API ist in der FreeRTOS Dokumentation[5] erläutert.

# 5.7 Implementierung auf dem Microblaze

Der Microblaze Port von FreeRTOS wurde unter dem, inzwischen veraltetem, EDK 7.1 erstellt. Es hat für das aktuelle EDK >= 9.1i einige Änderungen gegeben und somit ist der Port ohne Anpassungen am aktuellen FreeRTOS 10.1i nicht mehr lauffähig. Die Liste der nötigen Änderungen befinden sich im Anhang B. Zusätzlich muss die Compiler Option -DMICROBLAZE\_GCC gesetzt werden, damit die korrekten FreeRTOS Quellen verwendet werden.

# 6 Konfiguration der Microblaze-Hardware für die Anwendungen

Dieses Kapitel beschreibt die Konfiguration der Hardware für die Verwendung mit FreeRTOS und einer Regelung. Pro instanziiertem IP-Core werden die benötigten Ressourcen im Virtex 4 FX12 FPGA mit angegeben. Der FPGA verfügt insgesamt über 5.472 Slices, 12.312 Logik Zellen und 12.312 Flip Flops. Die Werte stammen aus dem Design Report (Projekt→Generate and View Design Report) im EDK. Für die Regelung und FreeRTOS wird jeweils ein Interrupt benötigt, der zu einem exaktem Zeitpunkt ausgelöst wird. Dabei ist der Zeitpunkt für die Regelung kritischer, weswegen dessen Interrupt höher priorisiert werden muss. Dafür werden mindestens folgende Komponenten benötigt:

- Ein auf maximale Performance eingestellter Microblaze,

- je ein Speicher zur Ausführung der Anwendung, sowie des Bootloaders,

- jeweils ein Timer mit Interrupt für die Digitale Regelung und den FreeRTOS Tick,

- einen weiteren Timer um Messungen vorzunehmen,

- ein Interrupt Controller, da mehr als 2 Interruptquellen existieren,

- RS-232 Anschluss, sowie LEDs zur Visualisierung und Kommunikation,

- und Flash als nicht-flüchtigen Speicher, der die Anwendungen bis zur Ausführung enthält.

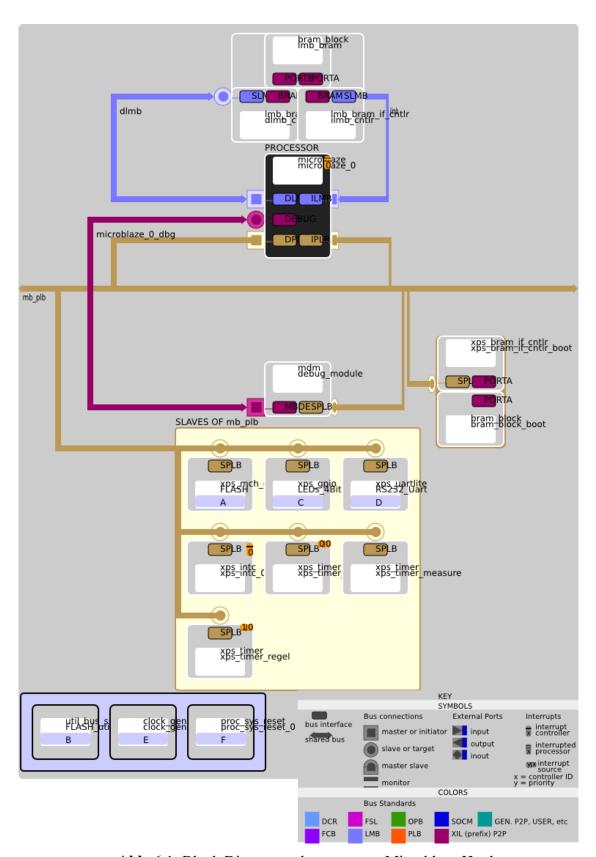

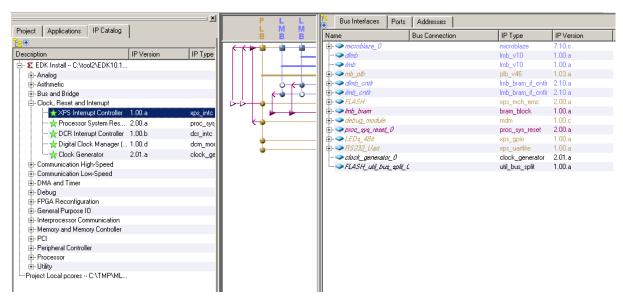

# 6.1 Übersicht der verwendeten Hardware

Das automatisch von Xilinx Platform Studio generierte Übersichtsbild auf der nächsten Seite veranschaulicht die generierte Hardware:

- Die komplette Peripherie ist über den PLB an dem Microblaze angeschlossen

- Der Block-RAM für den Hauptprogramm ist separat über den LMB angeschlossen, der Block-RAM für den Bootloader hängt ebenso wie der Flash am PLB.

- Das Debug Module verfügt zusätzlich über eine direkte Verbindung zum Microblaze

- Utility Bus Split, Clock Generator und das Prozessor System Reset Modul sind Schnittstellen und als solche nicht an einen Bus angeschlossen.

# **6.2 Eingesetzte Komponenten**

Die eingesetzten Komponenten werden nun erläutert:

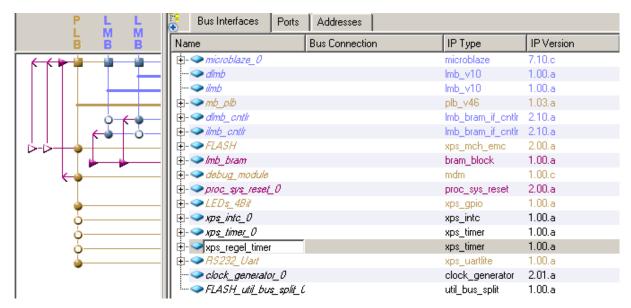

#### 6.2.1 Prozessor: Microblaze

Die Konfigurationsvariablen des Microblaze wurden auf maximale Performance eingestellt. Gegenüber der Standardeinstellung wurden aktiviert:

• Barrel shifter

Abb. 6.1: Block Diagramm der gesamten Microblaze Hardware

Abb. 6.2: Microblaze mit Debug, LMB, PLB, Clock und Reset Anschluss

- Extended Floating Point Unit

- 64 Bit Integer Multiplier

- Integer Divider

Es wird kein Cache verwendet. Das Programm wird im, am LMB angeschlossenem, Block-RAM ausgeführt, weswegen der ebenfalls den Block-RAM benutzende Cache keinen Geschwindigkeitsvorteil bringt.

Benutze Hardware:

| Art        | Benutzt | Verfügbar | Prozent |

|------------|---------|-----------|---------|

| Slices     | 2425    | 5472      | 44      |

| Flip Flops | 2319    | 10944     | 21      |

| LUTs       | 3749    | 10944     | 34      |

Tabelle 6.1: Belegung Microblaze

### 6.2.2 Memory Bus: LMB

Abb. 6.3: ILMB, DLMB mit Clock und Reset Anschluss

Verbindet den BRAM des Programms mit dem Microblaze.

Benutze Hardware pro LMB:

| Art        | Benutzt | Verfügbar | Prozent |

|------------|---------|-----------|---------|

| Slices     | 1       | 5472      | 0       |

| Flip Flops | 1       | 10944     | 0       |

| LUTs       | 1       | 10944     | 0       |

Tabelle 6.2: Belegung LMB

#### 6.2.3 Peripherie Bus: PLB

**Abb.** 6.4: PLB mit Clock- und Reset Anschluss

Prozessor Bus um die Peripherie anzubinden.

Benutze Hardware:

| Art        | Benutzt | Verfügbar | Prozent |

|------------|---------|-----------|---------|

| Slices     | 305     | 5472      | 5       |

| Flip Flops | 158     | 10944     | 1       |

| LUTs       | 449     | 10944     | 4       |

Tabelle 6.3: Belegung PLB

### 6.2.4 Programmspeicher: BRAM

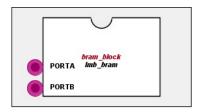

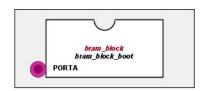

**Abb.** 6.5: BRAM für Programm (2 Ports) und (1 Port)

Es werden 2 Block-RAMs instantiiert: Einen für den Performance unkritischen Bootloader am PLB und einen am schnellen LMB für das Hauptprogramm. Vom lmb\_bram ist PortA mit dem Instruktionen-LMB, PortB mit dem Daten-LMB verbunden. Vom bram\_block\_boot ist nur der PortA mit dem PLB verbunden.

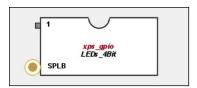

#### 6.2.5 Visualisierung: LEDs

**Abb.** 6.6: LED GPIO mit Verbindung zum PLB und zu einem FPGA Pin Zur Statusanzeige werden die 4 LEDs am ML403 verwendet Benutze Hardware:

| Art        | Benutzt | Verfügbar | Prozent |

|------------|---------|-----------|---------|

| Slices     | 63      | 5472      | 1       |

| Flip Flops | 91      | 10944     | 0       |

| LUTs       | 63      | 10944     | 0       |

Tabelle 6.4: Belegung LEDs

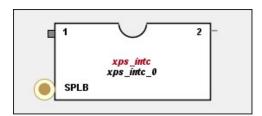

#### 6.2.6 Zeitmessung: Timer

**Abb.** 6.7: Timer mit Anschluss an den PLB. Der Regelung- und der FreeRTOS Timer verfügen noch über einen Interrupt Anschluss

Es werden drei unabhängige Timer IP-Core Instanzen benötigt: Einen für die Regelung, einen für den FreeRTOS-Scheduler und einen zum Messen der Performance. Der FreeRTOS- und der Regelungs-Timer werfen beide einen Interrupt. Alle 3 Timer Instanzen stellen auch nur einen Timer zur Verfügung.

Benutze Hardware je Timer:

| Art        | Benutzt | Verfügbar | Prozent |

|------------|---------|-----------|---------|

| Slices     | 252     | 5472      | 4       |

| Flip Flops | 294     | 10944     | 2       |

| LUTs       | 303     | 10944     | 2       |

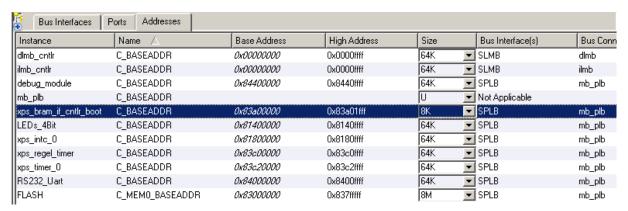

Tabelle 6.5: Belegung Timer